3D叠层封装集成电路的缺陷定位方法*

2016-07-19林晓玲恩云飞姚若河

林晓玲 恩云飞 姚若河

(1.工业和信息化部电子第五研究所 电子元器件可靠性物理及其应用技术重点实验室, 广东 广州 510610;2.华南理工大学 电子与信息学院, 广东 广州 510640)

3D叠层封装集成电路的缺陷定位方法*

林晓玲1恩云飞1姚若河2†

(1.工业和信息化部电子第五研究所 电子元器件可靠性物理及其应用技术重点实验室, 广东 广州 510610;2.华南理工大学 电子与信息学院, 广东 广州 510640)

摘要:三维(3D)叠层封装集成电路是高性能器件的一种重要封装形式,其独特的封装形式为失效定位带来了新的挑战.文中融合实时锁定热成像和X射线探测技术,提出了一种3D叠层封装集成电路缺陷定位方法.该方法首先利用X射线探测技术从器件的正面、侧面获取电路内部结构并成像,进而确定芯片的装配位置及面积、芯片叠层层数、引线键合方式;然后利用锁定热成像技术获得缺陷在封装内部传播的延迟信息及在封装内部xy平面上的信息,通过计算不同频率下的相移来确定叠层封装中缺陷在z轴方向的位置信息.对某型号塑料封装存储器SDRAM中缺陷的定位及对缺陷部位的物理分析表明,锁定热成像与X射线探测技术相结合,可以在不开封的前提下进行3D叠层封装集成电路内部缺陷的定位.

关键词:三维叠层封装;集成电路;缺陷定位;失效分析

用立体空间实现多芯片互连的三维(3D)叠层芯片封装技术在提高电路性能的同时,极大地降低了电路的功耗,成为高性能器件的一种重要封装形式[1- 2].

在叠层芯片封装中,通常采用液态环氧树脂或者环氧树脂薄膜作为多层芯片之间的粘合剂.封装过程中注塑压力的大小、环氧树脂颗粒的大小、叠层芯片之间的缝隙大小等,都是采用液态环氧树脂作为贴片粘合剂时容易出现网状芯片破裂的原因.与封装有关的缺陷是3D叠层封装器件的主要失效机理之一[3- 5].近年来,针对3D叠层封装集成电路失效的分析,大多集中在封装级缺陷导致的失效及其分析,分别采用声学扫描显微技术和剖面固封研磨法、聚焦离子束技术、ANSYS有限元模拟等去揭示及分析封装工艺造成的某层芯片网状破裂或者叠层芯片分层等失效[6- 7].

在3D叠层封装集成电路中,除了出现封装级失效外,还会出现如介质击穿、静电放电(ESD)损伤、过电应力(EOS)损伤、后道互连工艺相关的缺陷等芯片级失效,要求相应的缺陷定位技术不仅能定位缺陷在xy平面上的位置,还要能给出缺陷在z轴方向上的深度信息,以确定缺陷位置.3D叠层封装形式的出现,使失效分析面临新的挑战.传统的以机械探针、光学显微术、光发射显微技术、红外热像法、液晶法、扫描电子显微镜、电子束测试等针对单一芯片封装形式的失效定位方法无法满足多芯片叠层封装电路中缺陷的探测.时域反射技术(TDR)和磁显微缺陷定位技术由于空间分辨率等因素的限制也不能满足需要[8- 11],无法分辨出与电测结果相关的芯片级缺陷在封装内部多层芯片中的位置,无法为后续的物理分析(不同层对应的破坏性物理分析方法不同)缩小故障区域.

文中结合3D叠层封装的结构特点,提出了结合实时锁定热成像及X射线探测技术的3D叠层芯片封装器件内部缺陷定位方法,以便在不开封的情况下能对3D叠层芯片封装集成电路内部缺陷进行定位,确定缺陷部位在3D封装内部xy平面上的位置及具体芯片层.

1缺陷定位技术原理

1.1实时锁定热成像

热成像技术利用有缺陷或性能不佳的集成电路常常会出现异常热辐射并导致局部温度升高的原理进行定位.通过调制施加在被测电路上的电压并利用功率耗散和热辐射之间的关系来识别异常的发热,进而找到电路缺陷所在.在周期性时钟脉冲激励信号的作用下,缺陷产生周期性的热响应,并形成与信号频率相关的加电时的图像和断电时的图像[12- 15],分别用正交函数sint和cost表示.对sint和cost进行加权异或处理操作,得到异相位结果,即相位偏移(简称相移,用θ表示):

(1)

式中,θ代表激励信号及热响应之间的延迟信息,该结果与缺陷在z轴方向上的位置相关.对sint和cost的同相位结果用于表示缺陷所产生热源在xy平面上的位置.

利用锁定热成像技术可以得到缺陷在封装内部传播的延迟信息及在封装内部xy平面上的信息,但无法确定热源所处的具体位置信息,无法分辨缺陷位于叠层封装中的哪层芯片上.而且仅借助该技术时,由于不清楚叠层封装内部芯片的大小及位置等结构信息,故无法判断是芯片内部的缺陷还是引线等其他部位的缺陷.因此,不能仅仅依靠此技术来实现对叠层封装中芯片级缺陷的定位.

1.2X射线探测技术

X射线探测技术是根据样品不同部位对X射线吸收率和透射率的不同,利用X射线通过样品各部位衰减后的射线强度来检测样品内部缺陷.X射线衰减的程度与样品的材料品种、样品的厚度和密度有关.样品局部缺陷会造成该处的吸收系数异常,进而引起X射线影像图的局部衬度异常,通过观察X射线像,可判断样品是否异常.

X射线探测技术可以在不打开封装的情况下检测电子元器件及多层印刷电路板的内部结构、内引线开路或短路、粘接缺陷、焊点缺陷、封装裂纹、空洞、桥连及器件漏装等缺陷.利用该技术,可以观察叠层封装器件中的芯片位置、引线键合方式、叠层层数,但受空间分辨率的限制(亚微米量级),无法对封装芯片上的细微缺陷进行探测定位.

1.3缺陷的3D定位

根据叠层封装集成电路的结构特点,对叠层封装电路中缺陷的探测需要在不开封的情况下进行,单纯依靠上述两种方法均无法达到此要求.因为利用X射线探测技术从器件的正面、侧面等不同角度获取电路内部结构并成像,可确定芯片的装配位置及面积大小、芯片叠层层数、引线键合方式;然后结合X射线观察像与锁定热成像进行分析,根据X射线正面观察像与热成像的叠加可判断热斑所在的位置是在芯片范围内还是在引线键合范围内,但根据X射线侧面观察像显示的芯片叠层层数结合锁定热成像技术得到的z轴深度信息(延迟信息),仍然无法准确判断缺陷部位是位于哪层芯片中.

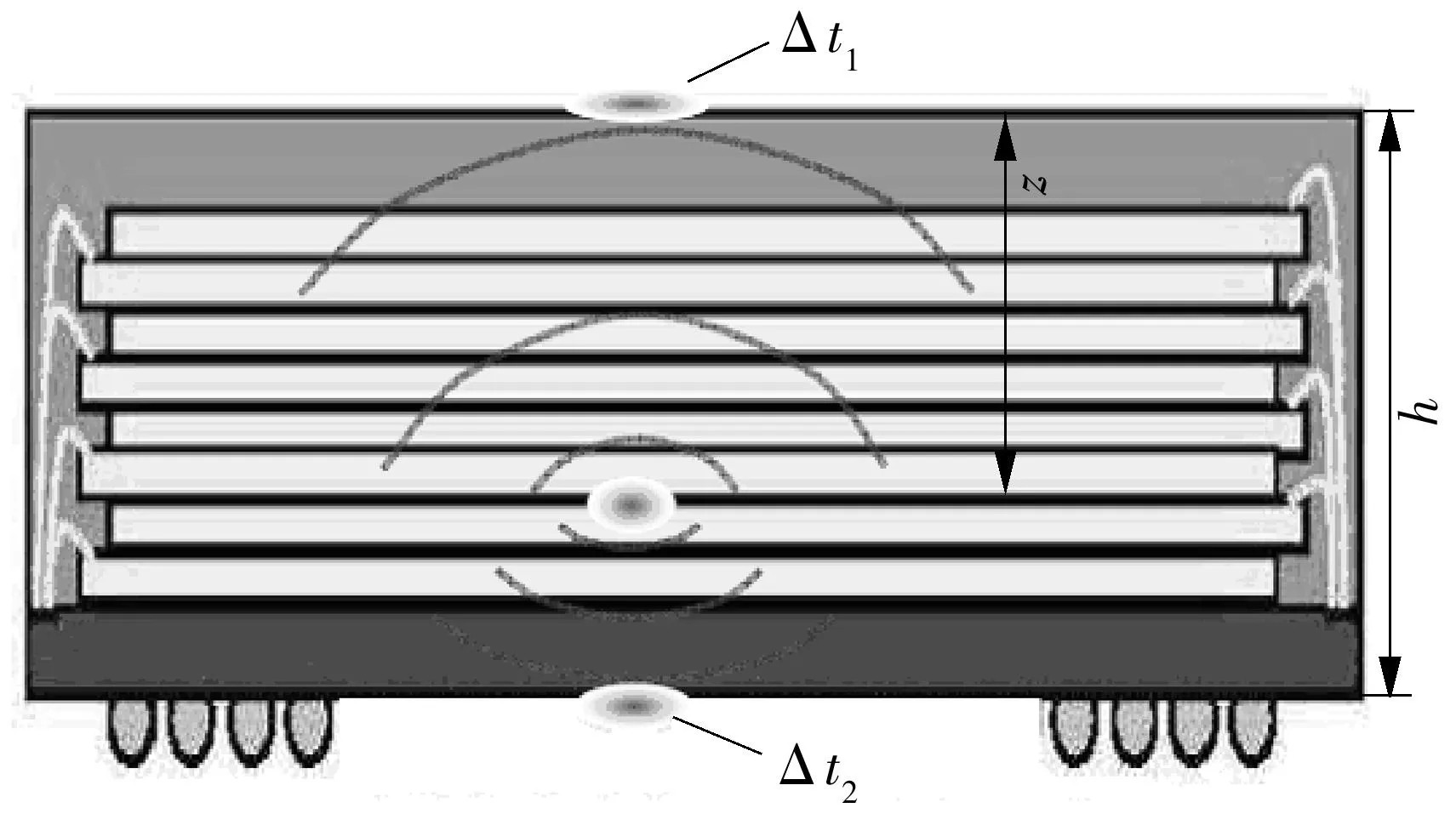

在不开封的情况下,封装内部缺陷所产生的热响应需穿透封装材料传播至器件的表面才能被探测到.假设封装内部所有材料的特性都是一致的,则热响应传播的原理可以简化,如图1所示.从器件的正、背面对封装内部的热传播进行探测,分别得到热延迟时间Δt1及Δt2,再结合器件本身的厚度h,可推算出缺陷所在位置的深度信息z:

(2)

图1 封装中缺陷热响应传播的简化原理

Fig.1Simplified principle of the thermal response propagation of the defect in the package

实际上,集成电路的封装中包含多种材料,如包括塑封料、芯片之间的粘合剂、Si芯片、芯片底座等,这些对红外光的透明性并不一致.因此,封装内部缺陷所产生的热响应并不能够立刻被直接探测到,而是在封装内部传播经过某种材料(塑封料、芯片、芯片之间粘接层等)产生一定的热延迟之后才到达器件表面而被探测到,热传播路径L是与频率相关的[16],也与封装内部的材料性能有关,如材料的密度ρ、热容率Cp、热导率κ等.

综合上述因素,不同频率下由材料特性决定的热传播路径为

(3)

式中:α=κ/(ρCp),为材料的热扩散率;f为频率.

热传播路径对应着激励信号由输入至在封装表面测到热响应时的热延迟θ,L和θ的关系如下:

(4)

(5)

Si芯片具有良好的热扩散,不会造成过多的热延迟,但芯片粘接剂及塑封料的热传播性则较差,会造成较大的热延迟.因此,非顶层芯片中缺陷的热耗散传播至封装表面所需的热延迟受芯片粘接剂等非Si材料的影响,势必远大于顶层芯片中缺陷的热延迟.将不同层次芯片的表面作为参考界面,对利用式(5)得到的参考相移值θref与利用式(1)得到的不同频率下的实际相移值θreal进行比较,可得到缺陷在封装内部的轴深度信息,解决叠层封装中缺陷在z轴方向上位置信息确定难的问题.

2实验验证

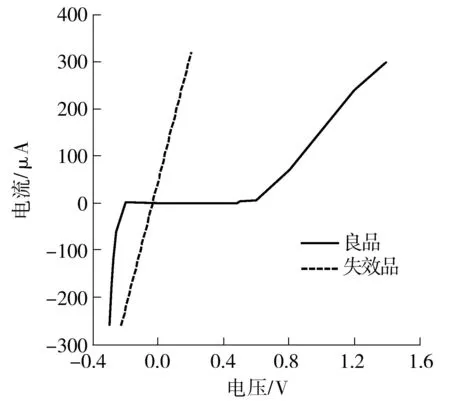

实验样品为某型号的塑料封装存储器SDRAM,采用极小尺寸BGA封装(107-ball FBGA).样品经ESD实验后,I/O 管脚(H8)对VSSN(E2)呈电阻性失效,如图2的虚线所示(实线为良品的I/O端口二极管特性).图3为样品的X射线侧面观察像,两层引线键合对应着封装内部的两层芯片叠层.

对3D叠层封装集成电路进行缺陷定位时,在没有电路设计资料的情况下,外管脚与封装内部键合引线的对应关系是无法知晓的.因此,虽然确定了H8管脚对VSSN(E2)呈电阻性失效,但却因分不清H8是上层芯片还是下层芯片上的键合引线而无法通过H8对E2所成的热成像直接判断该电阻性缺陷部位处于上层芯片还是下层芯片中.

图2 良品、失效样品的I-V特性曲线

Fig.2I-Vcharacteristic curves of the good and failed samples

图3 样品的X射线侧面观察照片

在H8对VSSN(E2)电压为0~0.5 V(5.7 mA)、热捕捉时间为5 min的条件下,捕捉H8对VSSN(E2)的热响应,得到断电和加电时的图像,如图4所示,从图4(b)可看到明显的红色斑点.将加电和断电时的图像叠加及异或处理,得到如图5所示的热成像,可初步确定红斑部位处于样品内部,对应着可能的缺陷位置.

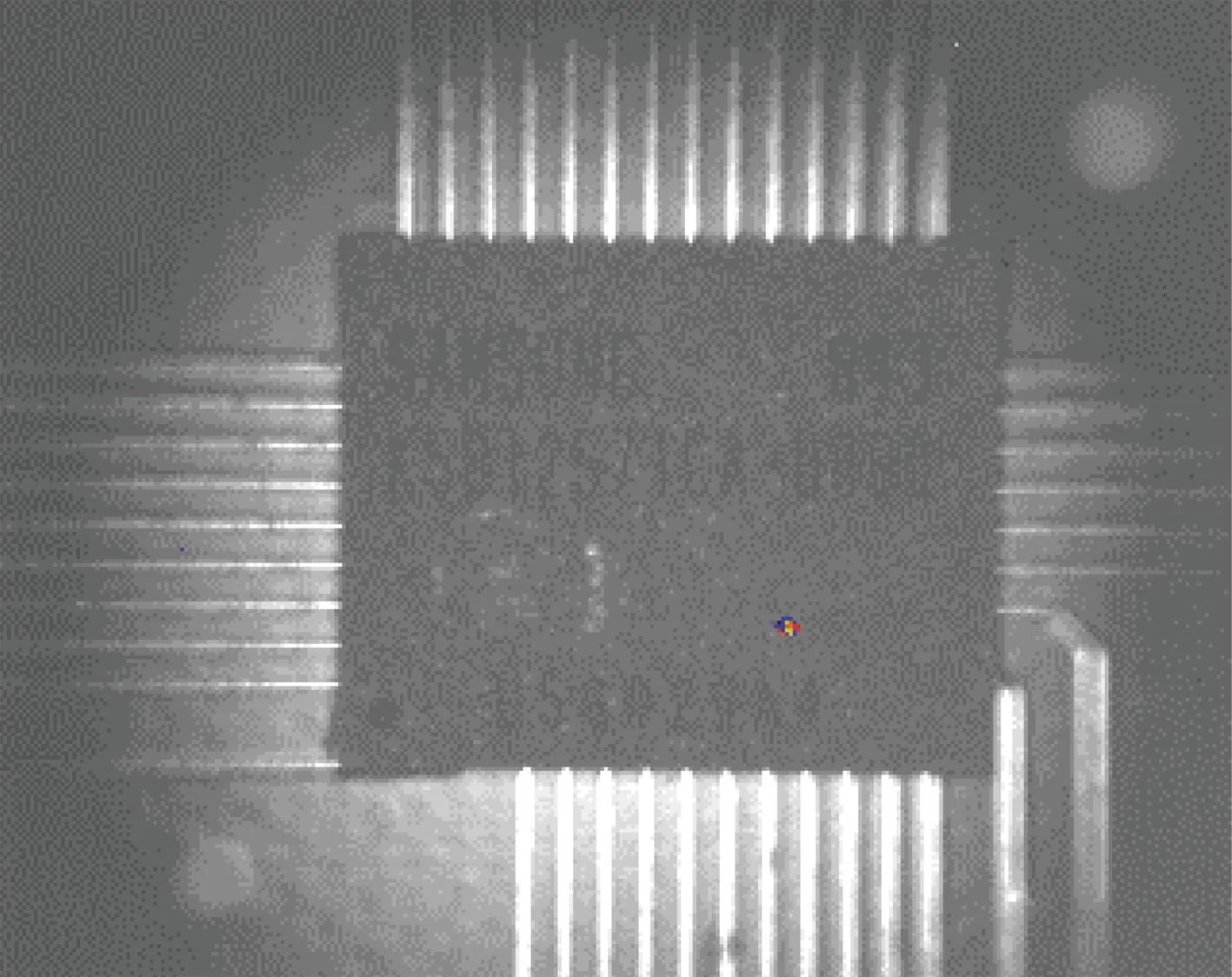

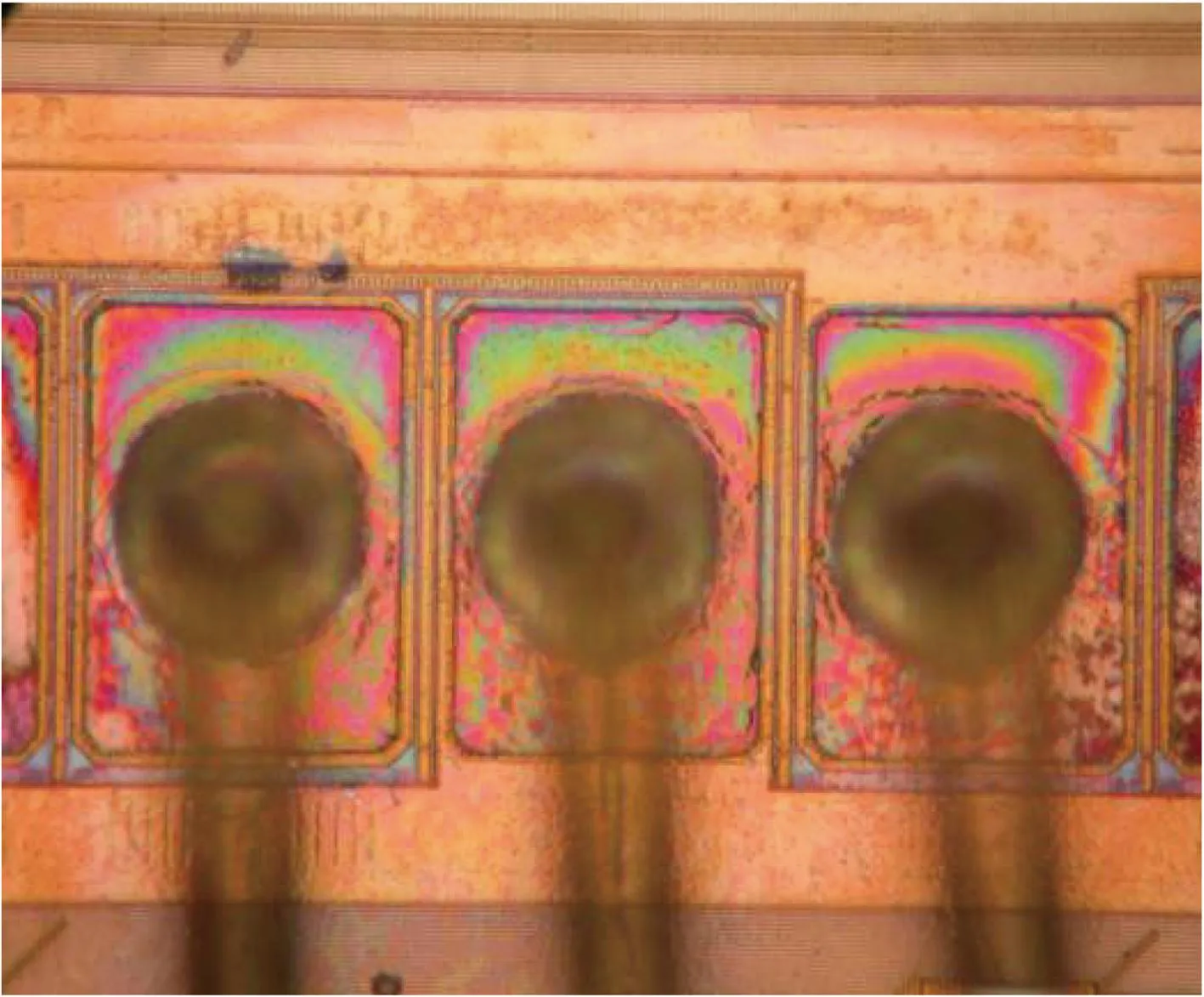

利用X射线探测技术观察样品的内部结构,得到的X射线观察正面像如图6所示.芯片采用金丝引线键合,键合丝、封装外部焊球及芯片均未见异常.将该X射线探测结果与图5的热成像相重叠并观察,结果见图7,从图中可以看到该红斑位于芯片内部,并不是引线互连方面的缺陷,进而获得了缺陷部位在封装内部xy平面上的信息.

该存储器样品的塑封封装整体高度为1 001 μm,对同批次良品进行环氧固封,之后利用研磨的方法制作剖面.分析该剖面,得到芯片上方塑封材料、上/下层芯片、芯片粘接剂的厚度分别为339.07、187.44、190.08、66.01 μm,如图8所示.因此,上层芯片上表面中缺陷产生的热辐射传播至封装表面被探测到的路径约为339.07 μm,下层芯片上表面中缺陷产生的热辐射传播至封装表面被探测到的路径约为592.52 μm.根据封装中塑封材料、Si芯片和层间粘合剂(环氧树脂薄膜)的密度、热容量、热导率,计算得到塑封材料、上/下层芯片、芯片粘接剂的热扩散率分别为0.80、87.00、87.00、0.13 mm2/s.

(a)断电时

(b)加电时

图5 H8对VSSN的热成像

图6 X射线图像

图7 热成像与X射线像重叠(H8对VSSN)

分别计算在不同频率(1、2、5、10、20 Hz)下缺陷在上层芯片上表面、下层芯片上表面时的参考热延迟θref,结果如图9所示.再结合样品中各材料的特性参数分别计算出不同锁定频率(1、2、5、10、20 Hz)下的热延迟θreal,结果如图9所示.从图中可以看出,实测的热延迟小于热延迟参考值.结合式(2)可知,缺陷在封装内部的位置越深,即z值越大,热传播距离越大,对应的热延迟也越大.因此,可判断缺陷部位在上层芯片上.

图8 由良品获得的封装内部的各层厚度

图9 热延迟与锁定频率的关系

Fig.9Relationship between theremal delay and lock-in frequency

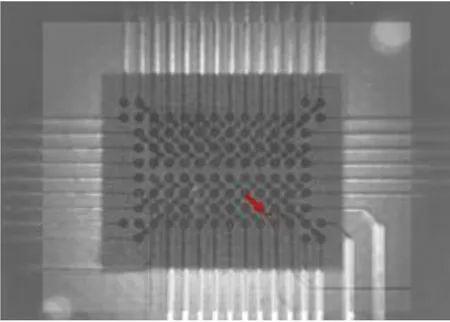

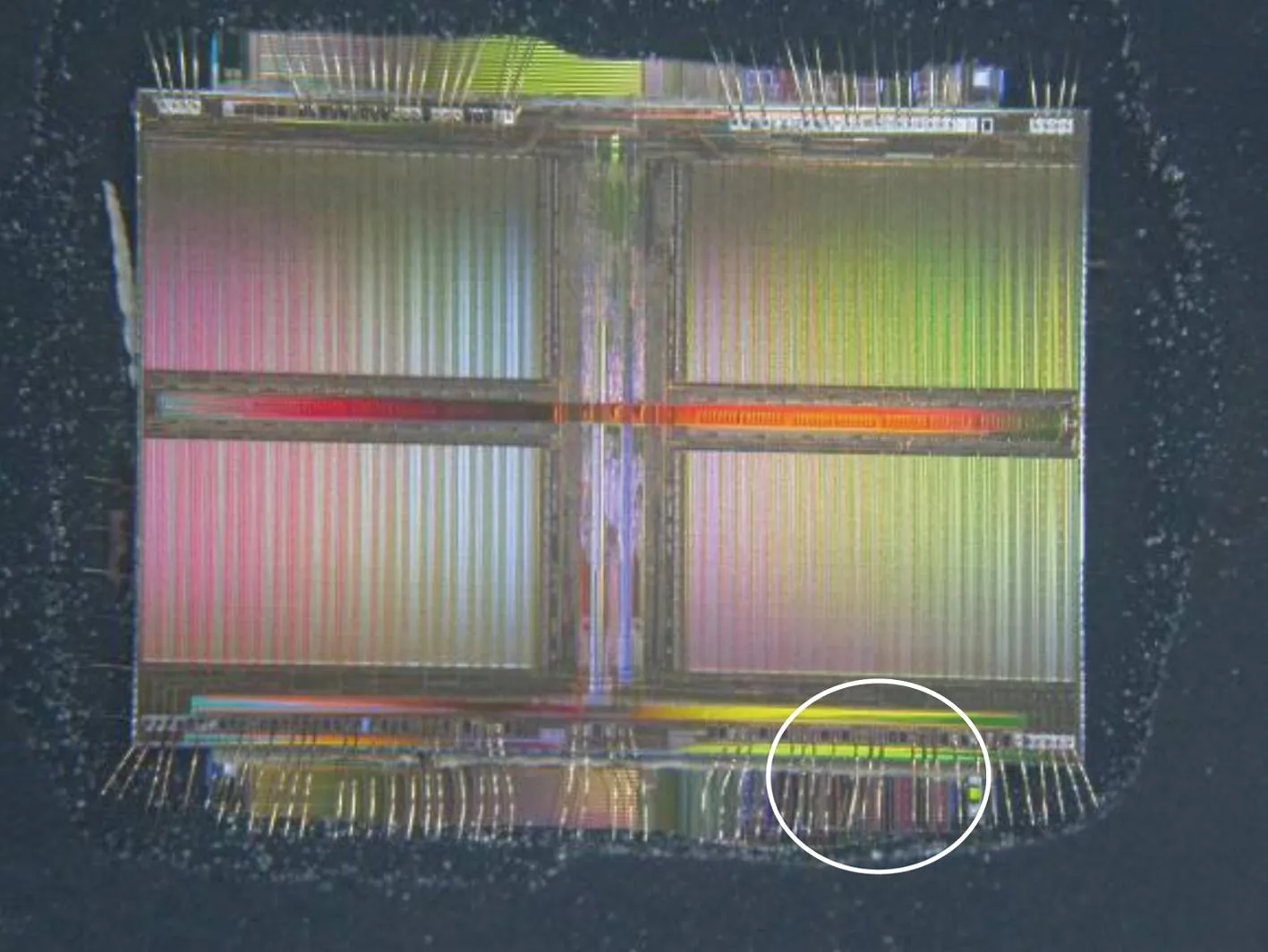

根据上述确定的缺陷在封装内部xy平面及z方向上的信息,利用化学腐蚀法对该样品进行开封.开封后的样品形貌如图10所示.结合缺陷探测定位的结果及管脚的分布图可确定缺陷位置(位于图11的白色圆圈内),斑点所在位置在电子扫描显微镜下的形貌如图12所示.从图12可见,斑点所示位置的端口保护电路中出现了击穿烧毁形貌.观察芯片内部其他部位,未见其他异常损伤.

图10 开封样品的内部形貌

图11 缺陷定位方法锁定的缺陷范围

以上分析结果表明,锁定热成像技术与X射线探测技术相结合,可有效地实现3D叠层封装集成电路内部缺陷的定位.

(a)光学显微图像

(b)图(a)的局部放大图

(c)缺陷在电子扫描显微镜下的形貌

3结论

文中结合实时锁定热成像及X射线探测技术来实现3D叠层封装集成电路内部缺陷的探测定位.实验结果表明,该方法可缩小故障检测范围,将缺陷三维定位在一个很小的空间,在不开封的前提下进行三维定位,为缺陷后续的物理分析、失效机理确认提供了一种技术手段.

参考文献:

[1]邓丹,吴丰顺.周龙早,等.3D 封装及其最新研究进展 [J].微电子器件与技术,2010,47(7):443- 450.

DENG Dan,WU Feng-shun,ZHOU Long-zao,et al.3D package and its latest research [J].Microelectronic Device & Technology,2010,47(7):443- 450.

[2]夏艳.3D集成的发展现状与趋势 [J].中国集成电路,2011,146(7):23- 28.

XIA Yan.Development and trend of 3D integration [J].China Integrated Circuit,2011,146(7):23- 28.

[3]CRAIGIN B K,ZHOU B L,BRIDGMON J R.Stacked-die failure mechanisms for an octal,current input 20-bit analog-to-digital converter [C]∥Proceedings of the 31st International Symposium for Testing and Failure Analysis.San Jose:ASM International,2005:21- 26.

[4]RAMA L de la,NUARTN D,NERY M.Die edge thin film delamination on the bottom die of a stacked chip scale package(SCSP) [C]∥Proceedings of the 31st International Symposium for Testing and Failure Analysis.San Jose:ASM International,2005:37- 39.

[5]CHRISTOPHER C,FLORES D,ASPERA B.Effect of inter-die adhesive profile on the integrity of die surface in die stacking package [C]∥Proceedings of the 33rd International Symposium for Testing and Failure Analysis.San Jose:ASM International,2007:126- 129.

[6]顾靖,王珺,陆震,等.芯片叠层封装的失效分析和热应力模拟 [J].半导体学报,2005,26(6):1273- 1277.

GU Jing,WANG Jun,LU Zhen,et al.Failure analysis and thermal stress simulation in a stacked die package [J].Chinese Journal of Semiconductor,2005,26(6):1273- 1277.

[7]BALACANO D E L,RAMA L D L.Effect of die chip-outs and reflow temperature on the mechanical behavior of a 5-die-stacked chip scale package [C]∥Proceedings of the 33rd International Symposium for Testing and Failure Analysis.San Jose:ASM International,2007:130- 133.

[8]CHEN X L,YUAN G H,XU G N,et al.Advanced fault localization techniques in microelectronics failure analysis [C]∥Proceedings of the International Conference on Reliability Maintainability and safety.Guangzhou:IEEE,2014:3- 9.

[9]FARINA M,ANDREA D,DAVIDE M,et al.Time-domain

reflectometry for near-field scanning microwave micro-scopy [C]∥Proceedings of the International Microwave Symposium.Phoenix:IEEE,2015:1- 4.

[10]林晓玲,练建文,章晓文,等.基于差分图像定位法的集成电路光发射探测技术 [J].华南理工大学学报(自然科学版),2014,42(9):70- 75.

LIN Xiao-ling,LIAN Jian-wen,ZHANG Xiao-wen,et al.Differential image localization method for IC PEM [J].Journal of South China University of Technology(Natural Science Edition),2014,42(9):70- 75.

[11]ALTON J,IGARASHI M.Non-destructive fault localization in advanced IC packages using electro-optical terahertz pulse reflectometry [C]∥Proceedings of the Microelectronics Packaging Conference.Grenoble:IEEE,2013:1- 4.

[12]RUDOLF S,SHINOBU M,TOSHI N,et al.Use of lock-in thermography for non-destructive 3D defect localization on system in package and stacked-die technology [C]∥Proceedings of the 37th International Symposium for Testing and Failure Analysis.San Jose:ASM International,2011:68- 72.

[13]SCHMIDT C,ALTMANN F,GROSSE C,et al.Lock-in-thermography for 3-dimensional localization of electrical defects inside complex packaged devices [C]∥Procee-dings of the 34th International Symposium for Testing and Failure Analysis.Portland:ASM International,2008:102- 107.

[14]ANDONOVA A,ANGELOV G,CHERNEV P.Diagnostics of packaged ICs by infrared thermography [C]∥Proceedings of the 37th International Spring Seminar on Electronics Technology.Dresden:IEEE,2014:261- 266.

[15]WADHWA K,SCHLANGEN R,LIAO J,et al.Failure analysis of low-ohmic shorts using lock-in thermography [C]∥Proceedings of the 21st International Symposium on the Physical and Failure Analysis of Integrated Circuits.Marina Bay Sands:IEEE,2014:62- 65.

[16]CHRISTIAN S,FRANK A,RUDOLF S,et al.Non-destructive defect depth determination at fully packaged and stacked die devices using lock-in thermography [C]∥Proceedings of the 17th International Symposium Physical & Failure Analysis of Integrated Circuits.Singapore:IEEE,2010:1- 5.

收稿日期:2015- 07- 22

*基金项目:广东省自然科学基金资助项目(2014A030313656)

Foundation item:Supported by the Natural Science Foundation of Guangdong Province(2014A030313656)

作者简介:林晓玲(1978-),女,博士,高级工程师,主要从事微电子可靠性物理、IC失效分析技术研究.E-mail:lin_x_l@163.com †通信作者: 姚若河(1961-),男,教授,博士生导师,主要从事集成电路系统设计、半导体物理及器件研究.E-mail:phrhyao@ scut.edu.cn

文章编号:1000- 565X(2016)05- 0036- 06

中图分类号:TN 322.8

doi:10.3969/j.issn.1000-565X.2016.05.006

Defect Localization Method of 3D Stacked-Die Packaged Integrated Circuits

LINXiao-ling1ENYun-fei1YAORuo-he2

(1.Science and Technology on Reliability Physics and Application of Electronic Component Laboratory,The Fifth Electronics Research Institute of the Ministry of Industry and Information Technology,Guangzhou 510610,Guangdong, China; 2.School of Electronic and Information Engineering,South China University of Technology,Guangzhou 510640,Guangdong,China)

Abstract:Three-dimension(3D) stacked-die package is one of the important package types of high-performance devices.Its unique packaging brings new challenges to defect localization.In this paper,a localization method of defects inside 3D stacked-die packaged integrated circuits,which integrates both lock-in thermography imaging and X-ray detection technology,is proposed.Firstly, X-ray detection technology is used to obtain internal structure of the device horizontally and vertically,and thus the chip location and size,the stack layers and the wire bonding mode inside the package can be determined.Secondly,the propagation delay information of defects inside package and the defect location on xy plane are obtained via lock-in thermography imaging.Then, more exact location information of the defect in z direction is obtained by calculating the phase shift at different frequencies. Finally,some experiments are carried out to discover the localization of defects inside a plastic packaging SDRAM,and the corresponding physical analysis is made.The results show that the integration of lock-in thermography imaging with X-ray detection technology helps localize defects of 3D stacked-die packaged devices without decapping the device.

Key words:3D stacked-die package;integrated circuit;defect localization;failure analysis