高速逐次逼近模/数转换器结构设计综述

2016-07-06佟星元位康康

佟星元, 位康康

(西安邮电大学 电子工程学院, 陕西 西安 710121)

高速逐次逼近模/数转换器结构设计综述

佟星元, 位康康

(西安邮电大学 电子工程学院, 陕西 西安 710121)

摘要:对基于逐次逼近(SAR)模/数转换的高速模/数转换器(ADC)结构设计进行讨论。针对SAR ADC转换速率慢的缺点,分别探讨结合两步式结构、每步多比特结构以及多通道时间交织结构的3种高速SAR ADC系统架构。3种ADC系统架构上的优化不仅将SAR ADC推向了高速片上系统应用,还保持了其原有的低功耗优点。通过对基于SAR ADC的3种主流高速ADC的结构及原理进行研究,总结比较各自的优缺点,并阐述其在高速低功耗方向的发展趋势。

关键词:模/数转换器;逐次逼近;高速;低功耗

随着集成电路CMOS工艺的发展,晶体管的工作速度不断加快,供电电压也越来越低,这有利于数字电路的设计,但对于模拟电路却是很大的挑战[1]。逐次逼近(Successive-Approximation-Register,SAR)模/数转换器(Analog-to-DigitalConverter,ADC)是目前流行的一种ADC结构,所需模拟电路较少,其基本结构仅由采样/保持电路、比较器、数/模转换器(Digital-to-AnalogConverter,DAC)和逐次逼近逻辑控制单元组成。SARADC简单的结构与先进的CMOS工艺兼容,具有功耗低、面积小等优点[1-2]。然而,单通道SARADC自身转换速率不高,一般小于5兆次采样每秒(Ms/s)[1]。为了充分利用SARADC低功耗的优势,利用现有的工艺及成熟的设计技术从系统架构的角度对ADC进行优化,进而提高ADC的转换速率,已经成为近年来ADC的重要研究方向之一。目前,研究人员基于SARADC已经提出了多种高速ADC的优化结构,如基于SARADC的两步式(Two-step)结构[3-7]、基于SARADC的多通道时间交织(Time-interleaving)结构、基于SARADC的每步多比特(Multi-bits/step)结构等[8-12]。以上ADC结构的优化,主要在速度和功耗之间进行折中,利用系统结构的优化提高整体ADC的转换速率,同时保持一定的低功耗优势,在现代通信系统、高分辨率视频图像处理、生物医学等领域已经广泛应用[3,6,10]。

本文拟研究基于SARADC的两步式结构、基于SARADC的每步多比特结构和基于SARADC的多通道时间交织结构等3种主流的基于SARADC的高速ADC结构。分析3种结构的电路结构及工作原理,总结各自的优缺点及近年来的发展现状,阐述SARADC在高速低功耗方向的发展趋势。

1基于SAR ADC的两步式ADC结构

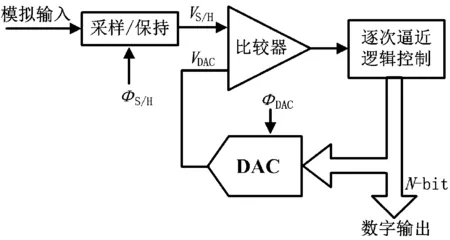

SARADC的基本结构如图1所示,其工作原理是基于二进制搜索算法产生基准电压,将模拟输入信号和DAC产生的基准电压逐次比较,进而产生ADC的数字输出。

图1 SAR ADC结构

两步式ADC也就是流水线ADC两级的结构,其实现方式是采用两级全并行模数转换器(FlashADC)级联。但在近几年,高集成绿色节能电路系统对低功耗指标的要求日益严格,将SARADC与两步式结构相结合已成为高速ADC的一种典型的低功耗优化结构。

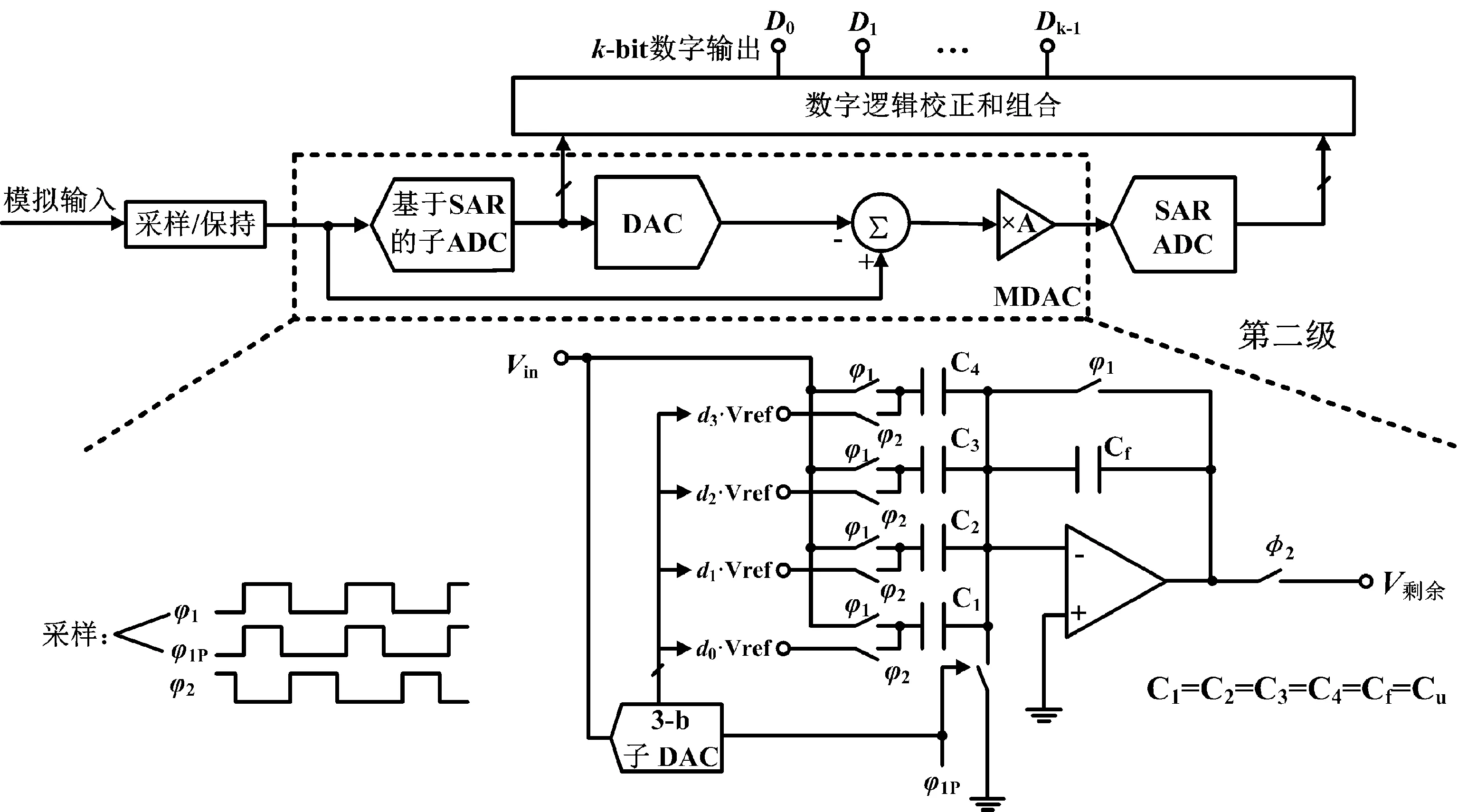

1.1基于SAR ADC的两步式ADC

基于SARADC的两步式ADC结构将传统两步式ADC中的两级FlashADC分别用SARADC代替,使其在实现两步式ADC高速工作特点的同时,兼具SARADC低功耗的优点。整个两步式ADC系统结构如图2所示,主要由采样/保持电路、第一级SARADC、中间级余量信号放大器、第二级SARADC和校准组合逻辑组成,图2还以第一级3比特为例,给出一种余量增益单元(MultiplyingDigital-to-AnalogConverter,MDAC)的实现方法。第一级基于SAR的子ADC用来产生m比特最高有效位(MSB)数字信号。余量信号经放大后作为第二级SARADC的输入,转换得到n比特最低有效位(LSB)数字输出。通常,第二级子ADC还设置1位冗余位用于数字校正。通过数字逻辑的校正组合,整个ADC输出k比特(k=m+n-1)数字信号。根据图2中MDAC部分的电路结构,传统的基于SARADC的两步式ADC和其第一级子ADC有着不同的采样路径,由于相位延时,采样信号很难同步。此外,如果子ADC离整个两步式ADC采样电容阵列的距离太远,采样时钟(φ1)和子ADC控制时钟(φ2)的时序偏移会引起孔径误差。针对上述问题,文献[3]中MDAC的输入采样电容与子ADC中的DAC共用一个电容阵列,该方法消除了图2中的采样路径不匹配问题。

图2 基于SAR ADC的两步式ADC

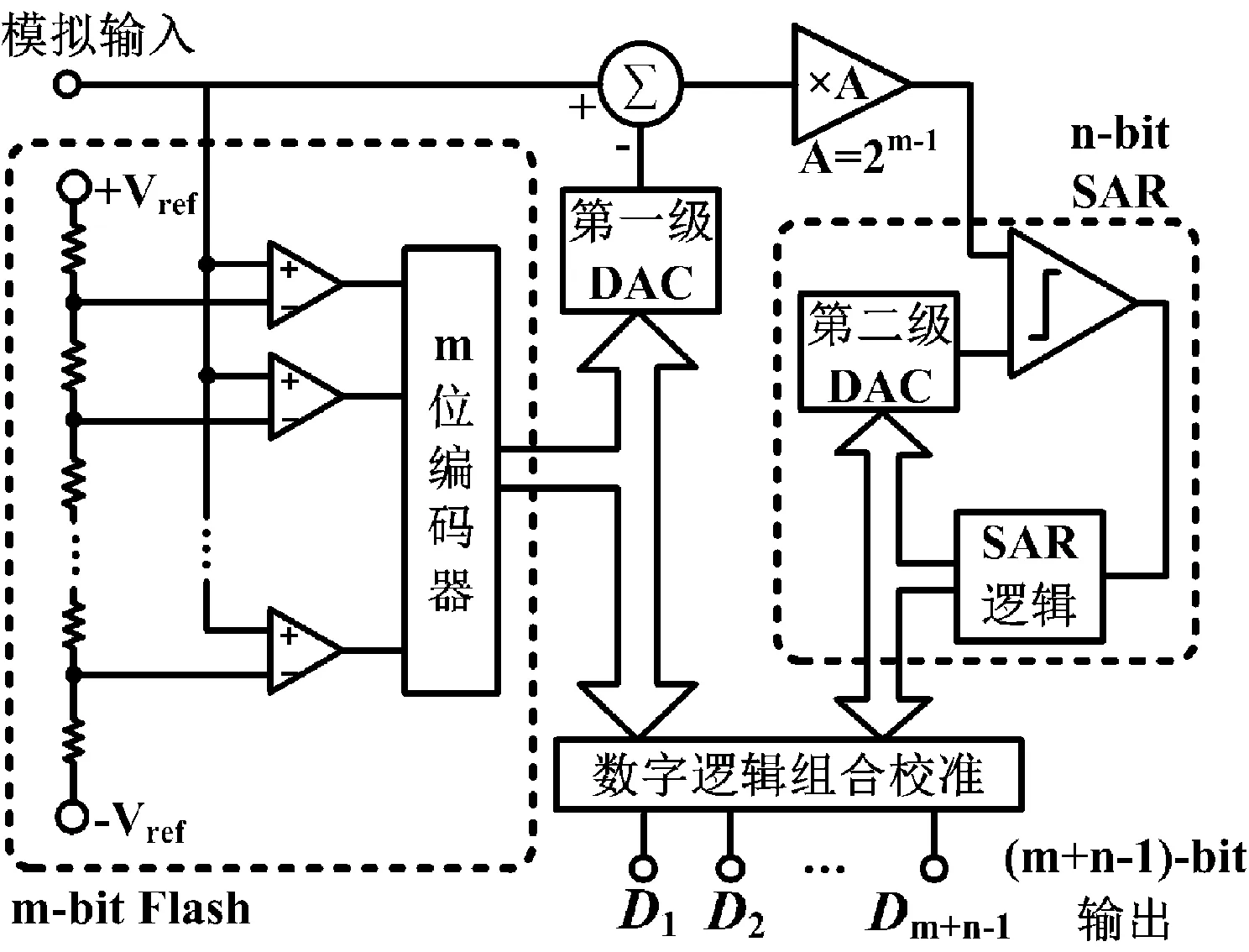

1.2基于Flash-SAR结合的两步式ADC

整个ADC的采样以及第一级子ADC的采样之间的匹配问题是设计难点。解决这一问题的一种有效方法是将FlashADC和SARADC通过两步式的工作方法相结合,如图3所示。与传统的两步式ADC类似,在采样阶段,采样/保持放大器对输入信号进行采样,之后进入保持阶段,第一级Flash子ADC对采样保持的信号进行量化、编码后输出m比特的MSB数字输出。余量信号经过中间级放大器放大之后送入第二级SARADC进行细量化,得到n比特LSB数字信号。最后,通过数字校正可以得到m+n-1位的数字输出。相比FlashADC,基于Flash-SAR结合的两步式ADC只需要2m+n个比较器,减少了比较器的数目,节省了功耗和面积。

图3 基于Flash-SAR结合的两步式ADC

基于SARADC的两步式ADC在实现较高采样速率的同时,保持了SARADC低功耗的优点。然而,SARADC的逐次逼近转换方式也限制了整体ADC的工作速度。基于Flash-SAR结合的两步式ADC比基于SARADC的两步式ADC采样速率更高,但也消耗了比基于SARADC的两步式ADC更多的功耗。综合以上,相比传统的两步式ADC、FlashADC以及SARADC,基于SAR的两步式ADC结构以及基于Flash-SAR结合的两步式ADC在采样速率和功耗之间进行了更好的折中,非常适合中高转换精度、中等采样速率的应用。目前,基于SARADC的两步式ADC可以在功耗仅1~9mW的条件下,实现12~14比特精度以及50~70Ms/s的采样速率[3-4]。基于Flash-SAR结合的两步式ADC转换速率可以达到百Ms/s左右的采样速率,能够用于卫星信号接收、有线电视、光电存储等应用[5-7]。

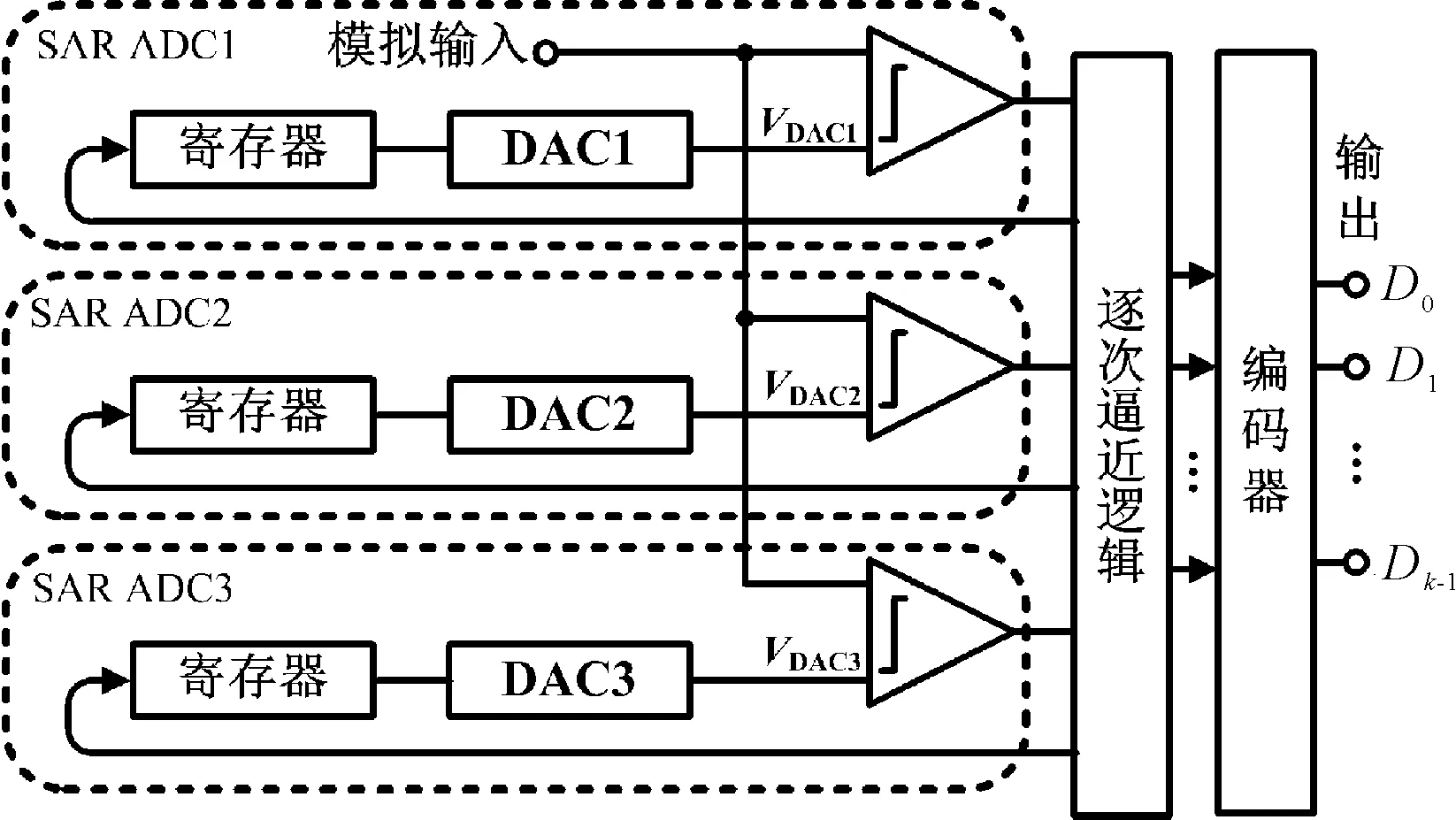

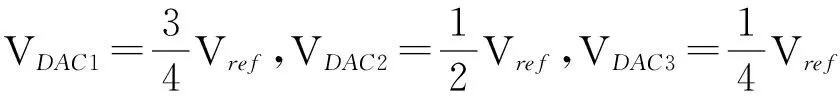

2基于SAR ADC的每步多比特ADC

传统SARADC只包含一个比较器,比较器的每次比较只产生一位数字输出。如果在SARADC中引入多个比较器,几个比较器同时比较则每步转换可以同时产生多位数字信号[9]。图4为一个基于2比特每步的SARADC结构,其中3个DAC分别基于二进制搜索产生逐次逼近所需的参考基准VDACi,初始值分别设置为

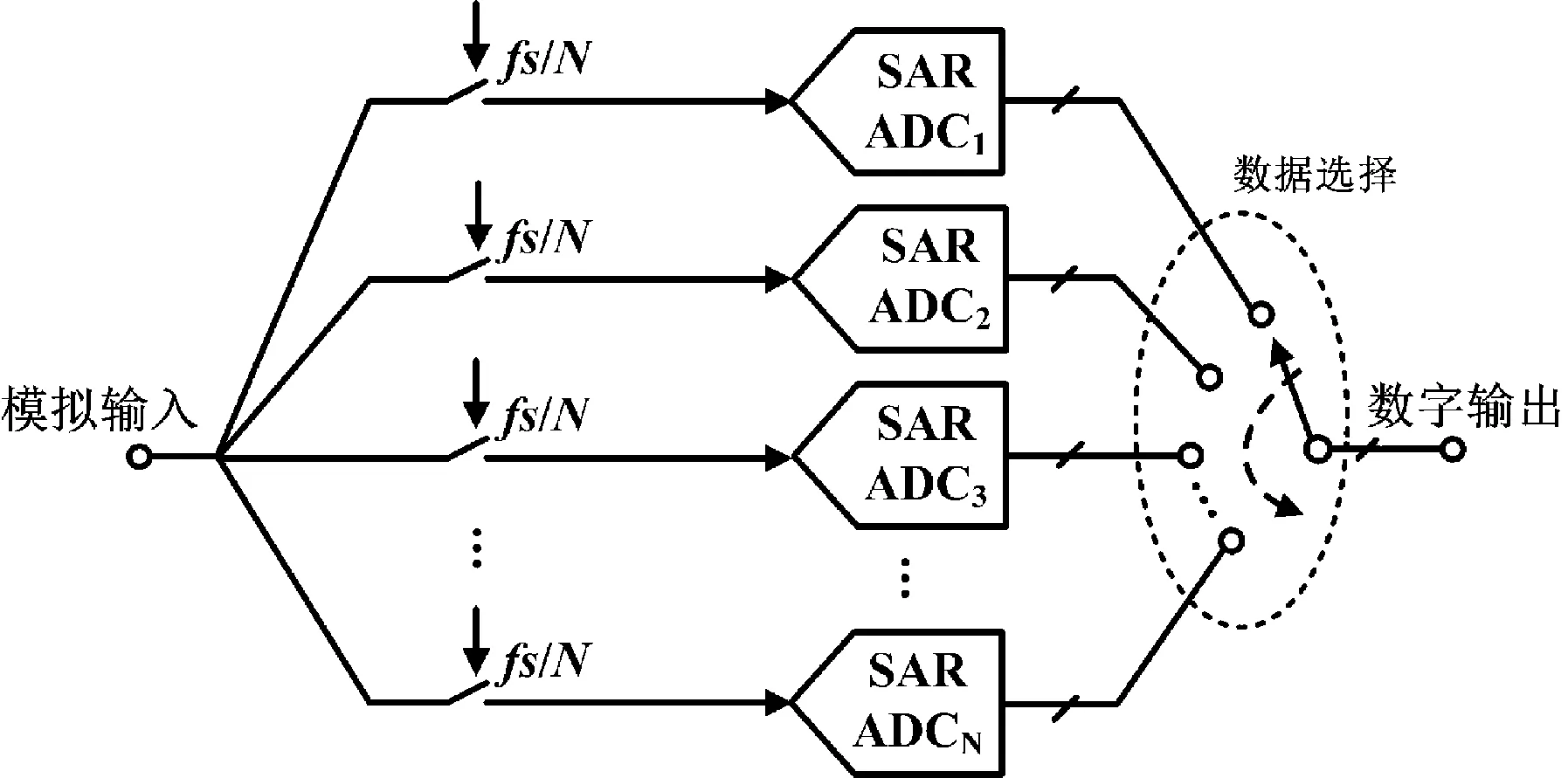

Vref为ADC的参考电压。如果3Vref/4 图4 基于SAR ADC的2比特每步ADC结构 基于SARADC的每步多比特ADC在整体结构形式上与FlashADC相似,考虑输入电容以及功耗方面的约束,一般精度不高(不超过8比特)[8-10]。相比传统的SARADC结构,基于SARADC的每步多比特ADC在采样速率和功耗/面积之间进行了折中,以较大的功耗和面积为代价,实现了更高的转换速率,但相比于FlashADC,基于SARADC的每步多比特ADC在功耗和面积方面具有明显优势。目前,基于SARADC的每步多比特结构已发展到400~800Ms/s转换速率的水平,精度一般在6~8比特,功耗为1~9mW左右,已广泛用于图像处理、超宽带接收等系统[9-10]。 3基于SAR ADC的时间交织ADC 尽管单通道SARADC的转换速率随着工艺的发展和设计水平的提高取得了显著提升,但通常仍小于100Ms/s。时间交织(Time-interleaving,TI)技术是实现超高速ADC最常用的方法之一[1]。时间交织ADC通过多个ADC并行同步量化的方法能成倍提高数据转换器的转换速率。如果N个通道进行交织,整个时间交织ADC的转换速率fs是单个通道ADC的采样速率fs/N的N倍。近年来,随着SARADC设计水平的提高,单通道SARADC已达到数十Ms/s的水平,通过使用时间交织技术使多通道SARADC并行工作,如图5所示,整个ADC已经可以实现Gs/s(吉次采样每秒)量级的转换速率[11-12],进而能满足超高速系统的要求。 图5 基于SAR ADC的时间交织ADC结构 相比基于SAR的两步式ADC和基于SAR的每步多比特ADC,多通道时间交织SARADC的功耗随着通道数目的增加而成倍数增大。基于功耗方面的考虑,同时考虑通道间的匹配性设计以及版图的布局难度,多通道时间交织ADC的通道数目不宜过大。目前,也有很多数十通道数目的时间交织SARADC,但为了减小由通道间的失配对性能的影响,需要采取复杂的误差校正和校准算法,这需要消耗额外的功耗。目前,多通道时间交织SARADC已经发展到8通道6Gs/s,160通道 40Gs/s的发展水平,广泛应用于高速数据通信,卫星信号接收等领域[11-12]。 4SAR ADC在高速系统的应用及展望 由于不同应用对ADC性能指标的要求不同,随着集成电路工艺的进步和设计水平的提高,模/数转换器总体上具有高速、高精度和低功耗3个发展方向。在便携式电子设备以及穿戴式、植入式生物医疗电子器件等领域,要求电路必须有足够小的面积和功耗,SARADC是这些应用领域中的首选ADC结构类型。然而,随着集成电路工艺尺寸减小到纳米级,同时考虑人们对电子产品绿色节能的不断追求,基于传统的流水线ADC、折叠差值ADC以及两步式ADC,由于电路结构复杂,已经很难满足低功耗的设计要求。 近年来,SARADC设计水平日益提高。在低功耗方面,单通道10比特SARADC功耗可以低至nW级[13]。在高精度方面,通过采取校准技术,目前也有14~16bit的SARADC产品[14]。在速度方面,得益于MOS器件本征速度的提升以及各种SARADC新型转换方案的出现,单通道SARADC的采样速率也已位于百Ms/s水平[15],这为SARADC在高速系统的应用打下了基础。 在ADC的高速应用领域不断出现新的功耗约束的情况下,考虑各种结构类型ADC的工作特点,并结合CMOS工艺尺寸日益减小的趋势,基于SARADC的混合式ADC结构逐渐成为高速ADC的低功耗优化结构。表1是对近几年基于SAR的高速ADC的发展现状进行了汇总,分别在转换速率、分辨率、功耗和面积等方面进行了对比。根据表1,基于SAR的混合式高速ADC结构已经有6~12bit分辨率范围内的研究成果,采样速率在数十Ms/s到数十GS/s范围。和同等指标的传统FlashADC、Two-stepADC相比,基于SAR的两步式ADC结构以及每步多比特ADC结构不仅面积较小,而且具有更优越的品质因数(Figure-of-Merit,FoM),FoM=Power/(2ENOB·fs)[16-17],其中Power、ENOB和fs分别代表ADC的功耗、有效位数和采样速率,单位为fJ/Conv.step。此外,SARADC结构简单的特点使其在先进的纳米级CMOS工艺下有很好的应用前景,基于单通道逐次逼近的时间交织ADC已成为高速ADC的重要结构类型,广泛应用于软件无线电及光通信领域。文献[12]中基于多通道时间交织SARADC所实现的40Gs/s采样速率的ADC,也代表着国内外高速ADC的领先水平。 表1 基于SAR的高速ADC研究现状 5结语 研究3种主要基于SARADC的高速ADC,讨论了基于SARADC的两步式结构、每步多比特结构以及多通道时间交织结构的工作原理、研究现状及各自的优缺点,并对SARADC在高速系统中的应用和发展前景进行了阐述。 参考文献 [1]佟星元 . 模/数转换器结构设计综述[J/OL],西安邮电大学学报,2013,18(2):75-79[2015-11-06].http://www.cnki.com.cn/Article/CJFDTotal-XAYD201302016.htm.DOI:10.3969/j.issn. 1007-3264. 2013.02.015. [2]TONGXY,YANGYT,ZHUZM,etal.Highspeed,highresolutionandlowpowerapproachesforSARA/Dconverter[C]//2009WiCOM,BeijingofChina:IEEE, 2009: 1-5.DOI:10.1109/WICOM.2009.5300895. [3]LEECC,FLYNNlMP.ASAR-assistedTwo-stagepipelineADC[J].IEEEJournalofSolid-StateCircuits, 2011, 46(4): 859-869.DOI:10.1109/JSSC.2011.2108133. [4]WUJF,CHANGSJ,LINSH,etal.LowpowerpipelinedSARADCwithloading-freearchitecture[C]//2014VLSI-DAT,Hsin-Chu:IEEE, 2014: 1-4.DOI:10.1109/VLSI-DAT.2014.6834906. [5]CHIOUF,WEIHG,ZHUY,etal.Designandexperimentalverificationofapowereffectiveflash-SARsubrangingADC[J].IEEETrans.Cir.andSyst,II:ExpressBriefs, 2010, 57(8): 607-611.DOI:10.1109/TCSII.2010.2050937. [6]LEEGY,YOONKS.DesignofalowpowerCMOS10bitflash-SARADC[C]//2014SOCC,LasVegasofUSA:IEEE, 2014: 88-91.DOI:10.1109/SOCC.2014.6948905. [7]TONGXY,CHENJM,ZHUZM,etal.Ahighperformance90nmCMOSSARADCwithhybridarchitecture[J].JournalofSemiconductors,2010, 31(1): 1-7.DOI:10.1088/1674-4926/31/1/015002. [8]WEIHG,CHANCH,CHIAOU,etal.An8-b400-MS/s2-b-per-cycleSARADCwithresistiveDAC[J].IEEEJournalofSolid-StateCircuits, 2012, 47(11): 2763-2772.DOI:10.1109/JSSC.2012.221418. [9]CAOZH,YANYS.A32mW1.25GS/s6b2b/StepSARADCin0.13μmCMOS[J].IEEEJournalofSolid-StateCircuits, 2009, 44 (3): 862-873.DOI:10.1109/JSSC.2008.2012329. [10]DAIG,CHENC.A400-MS/s8-b2-b/cycleSARADCwithsharedinterpolatorandalternativecomparators[C]//2014ISCAS,MelbourneofAustralia:IEEE, 2014: 2365-2368.DOI:10.1109/ISCAS.2014.6865647. [11]HUANGH,GROZINGM,JOHANNESD,etal.A6-GS/s6-bittimeinterleavedSAR-ADC[C]//2013MicrowaveIntegratedCircuitsConference,NurembergofGermany:IEEE, 2013: 37-40. [12]GRESHISHCHEVYM,AGUIRREJ,BESSONM,etal.A40GS/s6bADCin65nmCMOS[C]//2010ISSCC,SanFranciscoofUSA:IEEE, 2010: 390-391.DOI:10.1109/ISSCC.2010.5433972. [13]HARPEP,CANTATOREE,ROERMUNDAV.A10b/12b40kS/sSARADCwithData-DrivenNoiseReductionachievingupto10.1bENOBat2.2fJ/conversion-step,IEEEJournalofSolid-StateCircuits, 2013, 48(12): 3011-3018.DOI:10.1109/JSSC.2013.2278471. [14]AnalogDevices.16-bit, 1MSPSSARADC[EB/OL]. [2015-12-13].http://www.analog.com/cn/products/analog-to-digital-converters/ad-converters/ad7916.html. [15]HUANGGY,CHANGSJ,LinYZ,etal.A10b200MS/s0.82mWSARADCin40nmCMOS[C]//2013ASSCC,Singapore:IEEE, 2013:289-292.DOI:10.1109/ASSCC.2013.6691039. [16]VARZAGHANIA,KASAPIA,LOIZOSDN,etal.A10.3-GS/s, 6-BitFlashADCfor10GEthernetApplications[J].IEEEJournalofSolid-StateCircuits, 2013, 48 (12):3038-3048.DOI:10.1109/JSSC.2013.2279419. [17]CAOZH,YANSL.A52mW10b210MS/stwo-stepADCfordigital-IFreceiversin0.13μmCMOS[C]//2008CICC,CaliforniaofUSA:IEEE, 2008: 309-312.DOI:10.1109/CICC.2008.4672083. [责任编辑:祝剑] Overviewofthehigh-speedSARADCarchitecturedesign TONGXingyuan,WEIKangkang (SchoolofElectronicEngineering,Xi’anUniversityofPostsandTelecommunications,Xi’an710121,China) Abstract:The structures of Successive-Approximation-Register(SAR) based high-speed A/D converter(ADC) are discussed. Considering of the disadvantage of low-speed conversion in SAR ADC, three mainstream high-speed SAR ADC structures with two-step, multi-bit/step or time-interleaving techniques are respectively analyzed. These optimized structures endue SAR ADCs with rapidly gaining ground in high-speed Systems on chip, and can keep their inherent low-power merit. After a studying on the structures and operation principleson of these three high-speed SAR ADCs, their pros and cons are highlighted, and an outlook to use them with high speed and low power is given as well. Keywords:A/D converter, successive-approximation-register, high speed, low power doi:10.13682/j.issn.2095-6533.2016.02.014 收稿日期:2015-12-06 基金项目:国家自然科学基金资助项目(61204029);国家重大科技专项(2016ZX03001003-006);陕西省自然科学基金资助项目(2014JQ8332) 作者简介:佟星元(1984-),男,博士,副教授,从事集成电路设计研究。E-mail: mayxt@126.com 位康康(1990-),男,硕士研究生,研究方向为集成电路系统设计。E-mail:763865796@qq.com 中图分类号:TN432 文献标识码:A 文章编号:2095-6533(2016)02-0073-06