基于ARM+FPGA的EtherCAT主站设计及实现*

2016-07-04唐小琦

徐 健,唐小琦,宋 宝

(华中科技大学 机械科学与工程学院,武汉 430074)

基于ARM+FPGA的EtherCAT主站设计及实现*

徐健,唐小琦,宋宝

(华中科技大学 机械科学与工程学院,武汉430074)

摘要:为解决实时工业以太网协议EtherCAT应用于嵌入式主站控制器所产生的实时性和稳定性等问题,首先研究了EtherCAT主站控制器在EtherCAT网络控制系统中的功能需求,分析并提出了实现嵌入式EtherCAT主站的架构,然后针对上述架构设计了基于ARM+FPGA的EtherCAT主站实现的硬件方案,并设计了基于Xenomai补丁的实时Linux操作系统的软件实现方案,最后搭建了互联互通的互操作性测试平台,实验结果表明,该主站控制器具有EtherCAT标准协议的兼容性、极高的实时性以及稳定性。

关键词:EtherCAT主站;FPGA;ARM

0引言

实时工业以太网技术是在常规以太网技术上发展起来的,由于传统以太网采用CSMA/CD机制,应用于工业自动化控制系统时会产生实时性和稳定性问题[1-3]。因此,在传统以太网的通信模型基础之上进行修改来实现强实时性和稳定性的工业以太网,如EtherCAT、SERCOS等协议[4-5],不仅能够实现大数据量的高带宽传输,而且可以方便接入以太网网段,实现以太网直达现场级控制设备[6-7]。

EtherCAT由于其具有较为优良的性能而广泛应用于各类自动化控制系统当中。EtherCAT主站的实现大部分基于普通的网卡设备,利用系统软件的实时性来保证EtherCAT主站的实时性,可以实现微秒级别的实时性;其次,主站也可以利用专用硬件来实现,利用硬件的实时特性可以达到纳秒级别的实时性,同时具有较高的稳定性[8-9]。

本文针对实时工业以太网EtherCAT主站的实现进行了深入的研究,并设计和实现了基于嵌入式ARM处理器外挂主站专用硬件FPGA的软硬件实现方案,解决了EtherCAT主站控制器所要求的协议兼容一致性、强实时性和高的稳定性等技术问题。

1EtherCAT主站控制系统

1.1EtherCAT控制系统

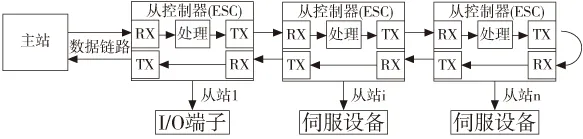

将EtherCAT协议应用于工业自动化控制系统当中,其控制系统结构如图1所示。EtherCAT工业以太网的控制系统属于一主多从的控制体系架构[10],其中主站属于整个网络控制系统的核心,用来调度整个网络的数据通信;而从站作为EtherCAT控制系统的执行部件,分布于整个控制系统当中,其类型可以包括I/O端子、伺服设备等。

图1 EtherCAT控制系统

EtherCAT主站发送集总帧数据帧依次经过各个从站,从站经过非常低延时的数据上传和下载操作后返回主站,主站根据相应子报文的响应来判别从站的状态,作为网络信息管理的输入迭代进行下一周期的通信数据准备。同时,EtherCAT主站作为系统上位机的调用接口,也为各种不同种类的自动控制应用提供了不同的API函数调用接口。

1.2EtherCAT主站控制器架构

根据EtherCAT主站置于EtherCAT控制系统中的作用可知,一方面EtherCAT主站负责EtherCAT网络信息的管理任务,而另一方面要负责与应用程序交互数据的API(Application Programming Interface)接口。

图2 EtherCAT主站控制器架构

因此,基于EtherCAT的主站控制器架构如图2所示,EtherCAT主站通过网口接入EtherCAT网络中,网口通过硬件接口层将网络中的差分信号进行处理生成能够被处理的数据帧流,数据帧到达EtherCAT数据帧接口层经过校验之后到达应用层协议处理单元,其按照EtherCAT协议来处理相对于的数据服务,例如周期性过程数据、非周期性的邮箱数据等,对于相应的数据服务则产生相应的应用程序API来直接调用有效数据。

2基于ARM+FPGA的EtherCAT主站硬件

设计

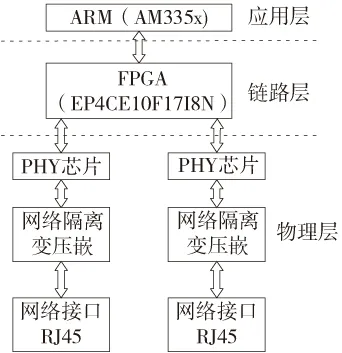

针对嵌入式处理器ARM外挂专用硬件FPGA实现的EtherCAT主站方案,其硬件设计框图如图3所示。本文采用的嵌入式ARM处理器为TI公司基于Cortex-A8的处理器AM335x,FPGA为Altera公司Cyclone IV系列的EP4CE10F17I8N。

其中,网络接口和PHY芯片等硬件部分主要完成与网络信号与处理数据信号的交互,负责EtherCAT通信参考模型的物理层部分;FPGA主要完成数据帧的解析和验算等过程,负责数据链路层部分;ARM主要完成EtherCAT协议驱动,负责应用层部分。通过这三部分的硬件设计可以完成EtherCAT主站控制功能。

图3 EtherCAT主站硬件总体方案

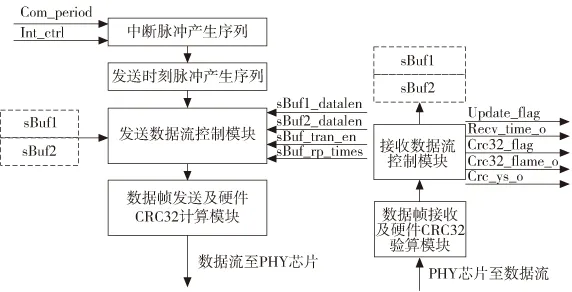

对于外挂专用硬件FPGA的设计,其设计框图如图4所示。FPGA中存在两个发送数据帧缓存区sBuf1、sBuf2和两个接收缓存区rBuf1、rBuf2,分别用来存放周期性数据帧和非周期性数据帧。利用中断脉冲产生序列能产生硬件等时中断,同时以硬件中断脉冲为基准产生数据帧发送脉冲序列用来发送数据帧,从而保证了EtherCAT主站的实时性。在产生发送时刻脉冲序列后,发送数据流控制模块根据ARM配置的本周期的发送配置寄存器发送缓冲区内相应的数据帧,同时并行硬件计算CRC32后将数据流发送至PHY芯片。对于PHY芯片数据接收而言,数据帧在一个周期内产生相应的接收标志寄存器供ARM进行读取从而操作相应的接收缓冲数据帧。

图4 FPGA设计链路层框图

图5 数据帧接口层设计

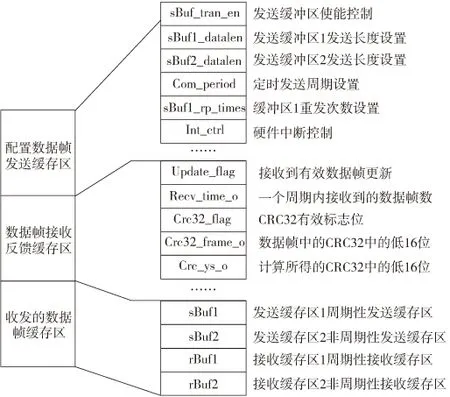

ARM与FPGA交互的数据层接口设计如图5所示,分为三个部分,分别为配置数据帧发送缓存区、数据帧接收反馈缓存区和收发的数据帧缓存区。其中,配置数据帧发送缓存区为ARM写入区域,作为上位机配置FPGA操作的寄存器接口;数据帧接收反馈缓存区作为FPGA接收数据的状态寄存器,作为ARM获取状态的接口;收发的数据帧缓存区作为ARM和FPGA交互有效数据帧区域。

3基于ARM+FPGA的EtherCAT主站软件

设计

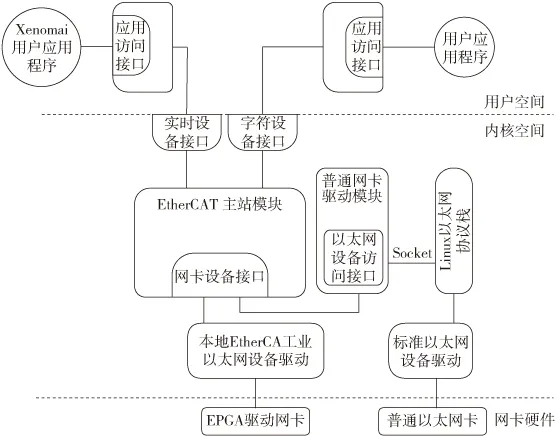

本文采用基于Xenomai的补丁构建的实时Linux操作系统,其主站软件架构如图6所示。其中,EtherCAT主站模块被是一个内核空间的模块加载在Linux内核中,相比较用户空间的代码有更好的实时性和更短的硬件操作特性。主站软件的功能主要完成EtherCAT协议驱动、基于FPGA的网卡设备驱动和应用程序接口模块,同时还包含了标准以太网卡的驱动,以便实现EtherCAT主站对普通网卡的兼容。

图6 EtherCAT主站软件架构

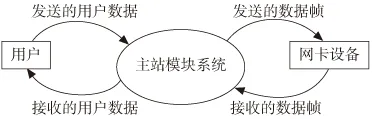

EtherCAT主站软件的三个模块之间的数据流如图7所示,用户直接通过应用程序接口(包括实时设备接口和字符设备接口)发送不同的指令数据给主站模块,主站模块根据EtherCAT网络状态信息将用户的指令数据进行封装打包成EtherCAT数据帧发送给网卡设备,网卡设备将数据帧处理后在发送在EtherCAT网络中实现用户层到底层设备的通信过程;反之接收数据的过程类似。

图7 EtherCAT主站的顶层数据流

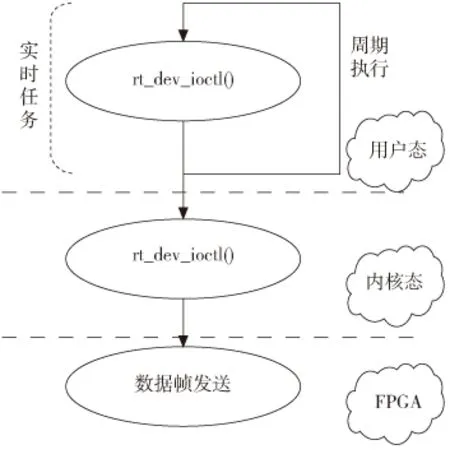

在嵌入式处理器ARM外挂专用硬件FPGA的软件实现的方案中,最关键的技术就是基于FPGA的硬件实时网卡驱动的调度设计。以单纯的处理器加Xenomai补丁运行Linux操作系统的软件实时调度为例,如图8所示。用户的实时任务通过周期调用实时控制函数来确保实时性,但是这种方式的实时性主要由Xenomai补丁的实时特性保证,当系统的负载过大或者存在多个实时任务调度的时候就会难以确保实时性的稳定。

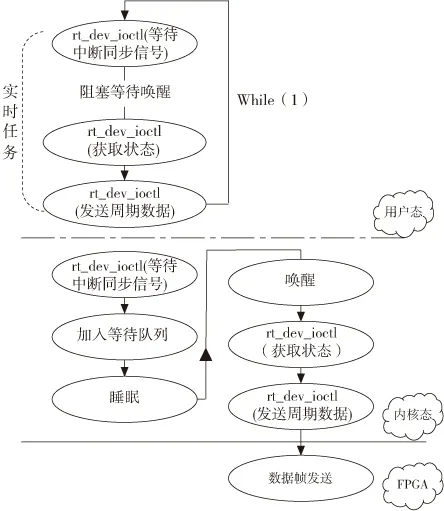

在外挂FPGA后,EtherCAT主站的实时性由FPGA和Xenomai实时补丁来共同保证,如图9所示。其中,实时任务不停地在执行三个函数,而在内核中等待中断同步信号函数的线程设为中断触发模式,等待FPGA产生的等时中断信号后唤醒该实时线程。实时任务负责与FPGA中的缓存区进行数据帧的交互,只要在FPGA内设定的中断至发送数据帧之间的时间范围内抖动都是可以接受的,而实际的数据帧发送时刻是以FPGA的时钟来精确保证的,确保了硬实时的任务调度。

图8 基于Xenomai的软实时任务调度

图9 基于Xenomai的FPGA硬实时任务调度

4系统集成测试及结果

本文所搭建的互联互通的互操作性实验平台采用的主站是基于ARM+FPGA的EtherCAT主站,从站采用SANYO DENKI公司生产的RS2系列伺服驱动器、Panasonic公司生产的A5B系列伺服驱动器和自制伺服驱动器,搭建了一个上位机运行数控系统G代码的三轴测试平台,如图10所示。

实验结果测试表明,该三轴控制系统能够在数控系统G代码下长时间运行,表明该系统具有很好的协议兼容性和具有稳定性。

最后,对专用外挂硬件FPGA方案的实时性进行了测试,以FPGA产生的定时中断脉冲信号为触发基准,测量发送数据帧使能时刻的信号抖动,测量结果如图11所示。由图中可以看出,在每个中断定时周期内,数据帧发送的时刻几乎维持不变,达到了纳秒级别的精度,远远高于传统网卡的方案,对于实时性要求高的控制系统来说具有很重要的意义。

图10 系统实验测试平台

图11 实时性测试结果

5结束语

本文在深入分析和研究了EtherCAT主站控制器的体系架构之上,对比了基于通用网卡方案和专用硬件FPGA方案的优缺点,提出了基于嵌入式处理器ARM外挂专用硬件FPGA实现的软硬件方案,实现了EtherCAT

主站控制器功能,实验达到了令人满意的效果,并且具有良好的协议兼容性、稳定性和较高的实时性。

[参考文献]

[1] 单春荣, 刘艳强, 郇极. 工业以太网现场总线EtherCAT及驱动程序设计[J].制造业自动化,2007 (11):79-82.

[2] 张少勋. 基于嵌入式数控平台的 EtherCAT 主站实现[D]. 广州:华南理工大学, 2013.

[3] 张磊. 基于 EtherCAT 的主站通信控制器设计[D]. 广州:广东工业大学, 2013.

[4] 李晓曦. 基于 EtherCAT 工业以太网嵌入式主站研究[D]. 广州:华南理工大学, 2014.

[5] 杨林. 基于 EtherCAT 工业以太网的现场控制系统主站设计与应用研究[D]. 南京:南京理工大学, 2014.

[6] Cereia M, Bertolotti I C, Scanzio S. Performance of a real-time EtherCAT master under Linux[J]. Industrial Informatics, IEEE Transactions on, 2011, 7(4): 679-687.

[7] 马春敏, 康存锋, 黄旭东, 等. 基于 Linux 的 EtherCAT 主站的研究[J]. 制造业自动化, 2011, 33(4): 78-82.

[8] Moon Y, Ko N Y, Lee K, et al. Real-time EtherCAT master implementation on Xenomai for a robot system[J]. International Journal of Fuzzy Logic and Intelligent Systems, 2009, 9(3): 244-248.

[9] Cereia M, Scanzio S. A user space EtherCAT master architecture for hard real-time control systems[C]//Emerging Technologies & Factory Automation (ETFA), 2012 IEEE 17th Conference on. IEEE, 2012: 1-8.

[10] 徐健, 宋宝, 唐小琦. EtherCAT 与 Modbus 协议转换网关的设计及实现[J]. 组合机床与自动化加工技术, 2015(4): 71-73.

(编辑赵蓉)

Design and Implementation of EtherCAT Master Based on ARM+FPGA

XU Jian, TANG Xiao-qi, SONG Bao

(School of Mechanical Science and Engineering, HuaZhong University of Science and Technology, Wuhan 430074, China)

Abstract:In order to solve real-time industrial Ethernet protocol EtherCAT applied to embedded master controller producing real-time, stability and other issues, first study EtherCAT master controller in the network control system functional requirements, analyze and propose architecture of embedded EtherCAT master, then for the above architecture design EtherCAT master hardware solution based on ARM + FPGA and software solution based on real-time Xenomai patch the Linux operating system, and finally build a interoperability testing platform, the experimental results show that the EtherCAT master controller has standard protocol’s compatibility, high real-time performance and stability.

Key words:EtherCAT master;FPGA;ARM

文章编号:1001-2265(2016)06-0084-04

DOI:10.13462/j.cnki.mmtamt.2016.06.022

收稿日期:2015-07-10

*基金项目:国家自然科学基金(51475185);"高档数控机床与基础制造装备"科技重大专项(2013ZX04007-021)

作者简介:徐健(1992—),男,江西宜春人,华中科技大学硕士研究生,研究方向为数控技术、现场总线及网络,(E-mail)xujian0935@163.com。

中图分类号:TH166;TG506

文献标识码:A