一种高速高精度的开环CMOS采样保持电路

2016-06-27唐小丽段吉海徐卫林向指航

唐小丽,段吉海,徐卫林,向指航

(桂林电子科技大学 信息与通信学院,广西 桂林 541004)

一种高速高精度的开环CMOS采样保持电路

唐小丽,段吉海,徐卫林,向指航

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

摘要:针对开关随输入信号幅度变化而导致的非线性,提出了一种基于栅压自举开关、带辅助电容的开环采样保持电路。电路采用双电容采样来消除电荷注入效应,并使用栅压自举开关代替传统双电容结构的输入开关,降低了输入开关的导通电阻,使得导通电阻与输入信号幅度无关,提高了电路的线性度。基于SMIC 0.18 μm CMOS工艺的设计仿真结果表明,在电源电压为1.8 V,输入信号频率为40 MHz,采样频率为500 MHz时,改进后的电路无杂散动态范围为92.49 dB,信噪比为124.29 dB,有效位数达14.98位。

关键词:采样保持电路;辅助电容;电荷注入效应;自举开关

模数转换器(ADC)被广泛应用于卫星通信系统、军事航空电子设备等领域,而采样保持电路作为ADC的一个重要组成部分,极大地影响了ADC的动态特性和输入带宽。按照拓扑结构,采样保持电路可分为闭环采样保持电路和开环采样保持电路。闭环采样保持电路包含一个闭环反馈,这也就限制了它的速度和稳定性。开环采样保持电路则具有结构简单、速度快、带宽大等优点[1-2],但由于线性度不高,限制了它的精度。其中影响线性度的最重要的因素是时钟馈通和电荷注入效应。通过添加辅助电容可消除电荷注入效应,减小电路的非线性误差[3],但其输入开关只采用普通的MOS开关,限制了电路的线性度。为此,采用自举开关代替MOS开关,以达到采样阶段导通电阻与输入信号无关,提高电路的线性度。

1基本结构及非理想特性

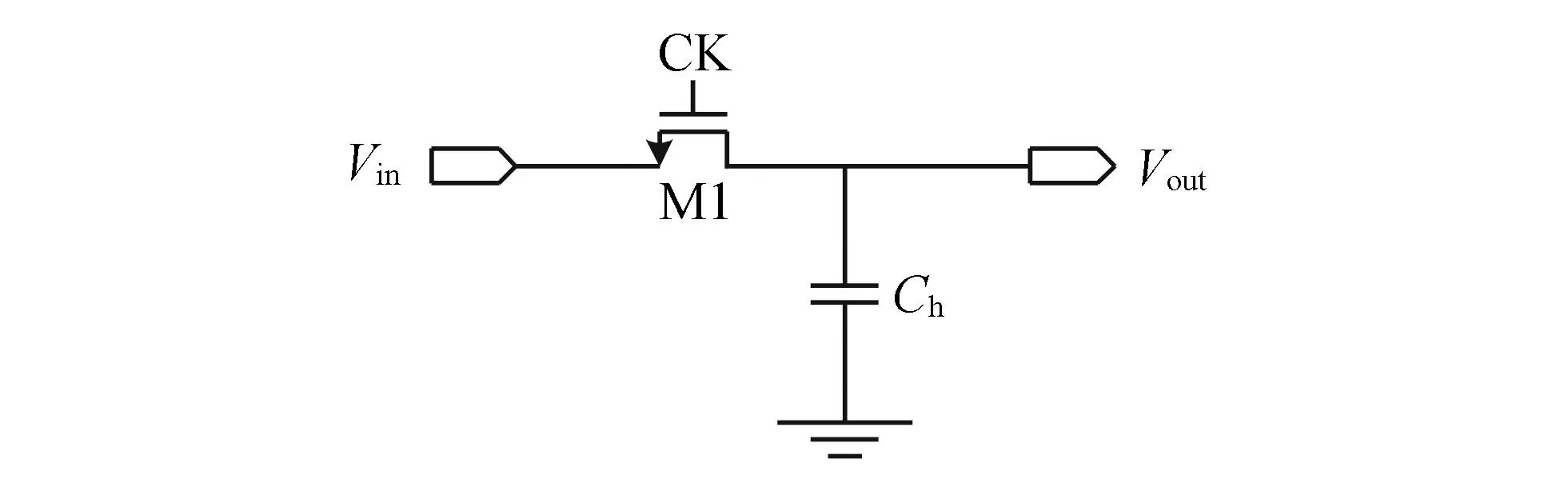

开环结构因为无全局反馈和补偿电路,也无需考虑系统的稳定性,所以具有非常高的采样速度。最基本的开环采样保持(S/H)电路如图1所示。主要由MOS晶体管、采样电容Ch和单位增益的输出缓冲器组成。

图1 开环S/H电路Fig.1 Open-loop S/H circuit

设计采样保持电路时,需要折中考虑以下因素。

1)带宽。理想开关的关断电阻为无穷大,导通电阻为零,但MOS管开关在导通时,却有不可忽略的导通电阻。当MOS管导通时,开环S/H电路可以简化为如图2所示。此时电路的-3 dB带宽为:

(1)

(2)

其中:Ron为导通电阻;Vin为输入电压;Vdd为电源电压;Vth为阈值电压;L、W分别为晶体管的长和宽。从式(2)可看出,导通电阻与输入电压相关,从而开关引入了非线性。从带宽的角度考虑,要应用在高速领域,Ron不能过大。

图2 开环S/H简化电路Fig.2 Simplified open-loop S/H circuit

2)电荷注入效应。电荷注入效应如图3所示,当晶体管导通时,其沟道中存在一定量的电荷,且总电荷可表示为:

(3)

图3 电荷注入效应Fig.3 Charge injection effect

当晶体管关断时,沟道电荷不能马上消失,分别流向晶体管的源极和漏极,流向源极的电荷不会影响被采样的电压,流向漏极的电荷则在保持阶段引起采样电容保持的电压发生误差。假设有一半的沟道电荷流入漏极,引起的误差为:

(4)

然而,沟道电荷在漏极和源极的分配比例是与多项参数相关的复杂函数[4]。

3)时钟馈通。由于MOS晶体管的寄生电容,使得在采样阶段,时钟信号通过栅漏交叠电容Coverlap将时钟信号和输出电压耦合,如图4所示。时钟馈通引起的误差为:

(5)

一般可通过增加虚拟开关的方法消除误差。

图4 时钟馈通效应Fig.4 Clock feed-through effect

2电路分析

2.1底极板采样技术

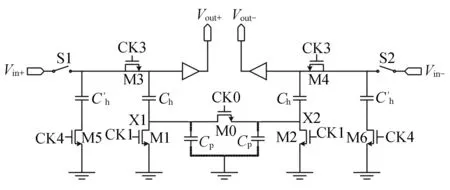

底极板采样技术通过控制采样开关在输入开关之前断开,从而保证电路在保持阶段的沟道电荷不会流向采样电容,避免引起误差[1]。采用底极板采样技术的S/H电路如图5所示。由于在X1、X2处M0、M1、M2漏极寄生电容的存在,使得在采样开关断开时仍存在通道,使得沟道电荷流向采样电容。因此,底极板采样并不能完全消除保持阶段的电荷注入效应。但此技术可以减小由电荷注入效应引起的误差,因为此时的等效电容Ceq为采样电容Ch和寄生电容Cp的串联,小于采样电容。

图5 底极板采样S/H电路Fig.5 S/H circuit with ground plate sampling

电荷注入效应引起的电压误差Verror表示如下:

(6)

(7)

(8)

其中Vin=Vin+-Vin-,Vth=Vth1-Vth2,是沟道电荷流入采样电容的比例因子。

图6 带辅助电容的底极板采样S/H电路Fig.6 S/H circuit with bottom plate sampling and auxiliary capacitors

增加辅助电容后,电荷注入效应引起的电压误差为:

(9)

(10)

(11)

对比式(8)、(11)可得出,在增加了辅助电容后,由电荷注入效应引起的误差明显降低。

2.2栅压自举开关底极板S/H电路

图7 栅压自举开关底极板S/H电路Fig.7 S/H circuit with bottom plate sampling and gate voltage bootstrapped switch

采用辅助电容的底极板采样技术虽然对保持阶段的电荷注入效应有一定的消除作用,但其输入开关只采用普通MOS晶体管。由式(2)可知,电路在采样阶段,晶体管导通电阻随输入信号幅度而变化,这样极大地引入了非线性。所以,在采样时,为了保证输入开关的线性度,用栅压自举开关S1、S2代替普通MOS晶体管,以提高电路的性能。栅压自举开关底极板S/H电路如图7所示。栅压自举开关底极板S/H电路运行模式如下:

1)跟踪模式。所有的开关闭合,输出随输入信号变化。

2)预采样模式。M1、M2打开,使得M0两端有相同的电压,以保证在M0打开时两端有固定的电荷注入。

3)采样模式。M0打开。

4)输入开关打开模式。栅压自举开关S1、S2打开,M3、M4关闭,吸收一部分输入开关的电荷注入,M5、M6仍然关闭,形成低阻通道来吸收开关的电荷注入。

5)预保持模式。在吸收电荷后,M5、M6打开。

6)保持模式。M1、M2闭合,进入保持阶段。

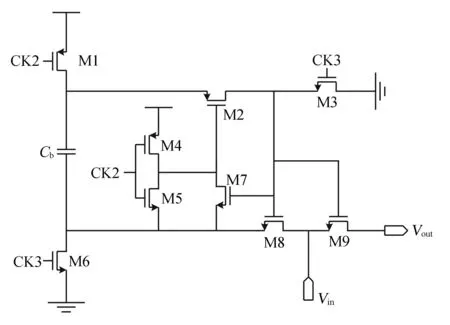

2.2.1栅压自举开关

开关S1、S2用栅压自举开关实现,如图8所示[5]。

图8 栅压自举开关电路Fig.8 Gate voltage bootstrapped switch circuit

当CK3为高电平时,CK2为低电平,M1、M3、M4、M6导通,自举电容Cb被充电到电源电压Vdd,晶体管M2、M5、M7、M8、M9关断,电路处于保持阶段。当CK3为低电平,CK2为高电平时,M1、M3、M4、M6关断,晶体管M2、M5、M7、M8、M9导通,电路进入采样阶段,M9的栅源电压为Cb保持的电源电压。M9的导通电阻可表示为:

(12)

对比式(2)、(12)可看出,导通电阻不再与输入电压有关,从而提高了电路的线性度。但因M9栅极处寄生电容的存在,在导通时M9的栅源电压实际上是对预充电电压Vdd的分压,根据电荷守恒原理,

(13)

其中:Vg,M9为M9的栅极电压;Cp为M9栅极处的寄生电容。由式(13)可得M9的栅电压

(14)

M9的栅源电压

(15)

则M9的导通电阻为:

(16)

从式(16)可看出,M9的寄生电容对预充电电压产生了分压[8]。因此,自举电容Cb必须足够大,用以克服寄生电容对预充电电荷的分享。

2.2.2时钟电路

在栅压自举开关底极板S/H电路中要用到5个不同的时钟,时钟电路如图9所示。通过使用反向器构成逻辑门和一个或门来产生所需的时钟,所有的时钟只需一个输入时钟信号CKin。因为时钟个数多,所以产生的时钟性能直接影响采样保持电路的性能,需要合理地设计反向器。

图9 时钟产生电路Fig.9 Clock generator circuit

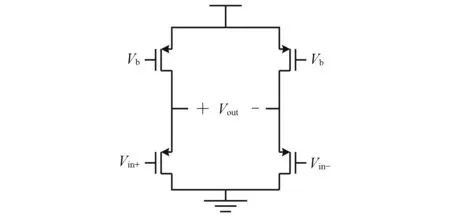

2.2.3缓冲器

图10 源跟随缓冲器Fig.10 Source follower buffer

电路的缓冲器主要由PMOS晶体管作为电流源的源跟随器实现,如图10所示。由于缓冲器的增益随输入信号幅度变化,从而引起了非线性。其交流增益表达式为:

(17)

其中:gm为输入管的跨导;rds为动态源漏电阻。

(18)

(19)

其中λ为沟道长度调制系数。从式(18)、(19)可看出,gm随输入变化,而rds也随输入变化,但变化的方向与gm相反。从式(17)可知,增益总小于1。采用PMOS晶体管的源跟随器可减小体效应带来的非线性。

3电路仿真

本研究在SMIC 0.18 μm CMOS工艺下,利用Cadence Spectres进行仿真验证。在电源电压为1.8 V的情况下,输入一个幅度为0.6 V的峰峰值、频率为40 MHz的正弦波,可得到在采样频率为500 MHz的输出频谱,如图11所示。从图11可看出,无杂散动态范围(SFDR)为92.49 dB,即最高点与次高点之差。通过Matlab计算得到的信噪比(SNR)达124.29 dB,S/H电路良好的信噪比保证了高速高精度ADC的性能。

图11 输出频谱Fig.11 Output spectrum

表1为本研究与其他文献在不同采样速率、不同输入频率下,信噪失真比(SNDR)的比较结果。从表1可看出,无论在何频段下,本研究的性能均优于文献[1,3,7],在高频时性能优于文献[6],但在低频时性能不如文献[6]。

表1 与同类高速S/H电路的SNDR性能比较

4结束语

通过改进已有的采用辅助电容的S/H电路,进一步提高了电路的线性度。仿真结果表明,在输入信号频率为40 MHz,采样频率为500 MHz时,改进后电路的SFDR为92.49 dB,SNR为124.29 dB,有效位数达14.98位。但由于本研究采用了辅助电容的方法消除电荷注入效应,即双电容采样,使得采样频率范围有限,需要进一步改进。

参考文献:

[1]HADIDI K H,MURAMATSU D,OUE T,et al.A 500 MS/s -54 dB THD S/H circuit in a 0.5 μm CMOS process[C]//IEEE Proceedings of the 25th European Solid-state Circuits Conference,1999:158-161.

[2]WEGMANN G,VITTOZ E,RAHALI F.Charge injection in analog MOS switches[J].IEEE Journal of Solid-state Circuits,1987,22(6):1091-1097.

[3]MOUSAZADEH M,HADIDI K,KHOEI A.A novel open-loop high speed CMOS sample-and-hold[J].AEU-International Journal of Electronics and Communications,2008,62(8):588-596.

[4]SHEU B J,HU C.Switch-induced error voltage on a switched capacitor[J].IEEE Journal of Solid-state Circuits,1984,19(4):519-525.

[5]LI Jian,ZHANG Jianyun,SHEN Bo,et al.A 10 bit 30 MS/s CMOS A/D converter for high performance video applications[C]//IEEE Proceedings of the 31st European Solid-state Circuits Conference,2005:523-526.

[6]ABOLHASANI A,HADIDI K,TOHIDI M.A new high-resolution and high-speed open-loop CMOS sample and hold circuit[C]//IEEE 21st Iranian Conference on Electrical Engineering,2013:1-6.

[7]MOUSAZADEH M,HADIDI K,KHOEI A.A highly linear open-loop high-speed CMOS sample-and-hold[C]//IEEE Asia Pacific Conference on Circuits and Systems,2010:228-231.

[8]谭智琴,王永禄,张龙生,等.一种高速采样/保持电路的设计与分析[J].微电子学,2014,44(2):164-166.

编辑:张所滨

A high-speed and high-resolution open-loop CMOS sample and hold circuit

TANG Xiaoli, DUAN Jihai, XU Weilin, XIANG Zhihang

(School of Information and Communication Engineering, Guilin University of Electronic Technology, Guilin 541004, China)

Abstract:In order to improve the nonlinearity caused by switch changing with the input signal amplitude, an open-loop sample and hold circuit based on a gate voltage bootstrapped switch with auxiliary capacitor is proposed. Double capacitance sampling method is adopted to eliminate the charge injection effect. And the input switch with traditional double capacitance structure is replaced by a grid bootstrapped switch, the input switch conduction resistance is effectively reduced, which makes conduction resistance independent of the input signal and improves the linearity of the circuit. The circuit is fabricated in SMIC 0.18 μm CMOS process. Simulation results show that the improved circuit spurious-free-dynamic range is 92.49 dB, signal-to-noise ratio is 124.98 dB, the effective number of bit is 14.98 bit on the condition that 40 MHz input signal at 500 MHz sample frequency and 1.8 V supply voltage.

Key words:sample and hold circuit; auxiliary capacitance; charge injection effect; bootstrap switch

收稿日期:2016-01-01

基金项目:国家自然科学基金(61161003,61264001,61166004);广西自然科学基金(2013GXNSFAA019333)

通信作者:段吉海(1964-),男,广西桂林人,教授,博士,研究方向为射频集成电路设计。E-mail:djh@guet.edu.cn

中图分类号:TN43

文献标志码:A

文章编号:1673-808X(2016)02-0099-05

引文格式: 唐小丽,段吉海,徐卫林,等.一种高速高精度的开环CMOS采样保持电路[J].桂林电子科技大学学报,2016,36(2):99-103.