基于FPGA的实时大窗口中值滤波器的设计

2016-05-14武继瑞刘泽

武继瑞 刘泽

摘 要: 中值滤波在图像预处理阶段有着重要的应用,尤其是对于图像中脉冲噪声的滤除。传统的中值滤波算法都是通过对原数据按照大小排序,然后才能取出中值。但随着窗口尺寸的扩大,因数据增多而造成比较次数的激增,这成为制约大窗口中值滤波器实时性的一个瓶颈。针对这一问题,该文提出一种基于FPGA的25输入的实时中值滤波器的设计方法。无需对原数据进行大小排序,而是根据各比特平面的信息,重新生成一个中值,特别适合于FPGA实现。设计专用的位处理单元,简化了电路结构。通过三级查找表的方式,解决“多数表决器”耗时长的问题。实验结果表明,滤波器资源占用少,数据吞吐率高,延迟小,可满足任何窗口形状的滤波要求。

关键词: 中值滤波; 数字滤波器; 图像处理; FPGA

中图分类号: TN713?34 文献标识码: A 文章编号: 1004?373X(2016)06?0117?03

Design of real?time big?window median filter based on FPGA

WU Jirui, LIU Ze

(Institute of Optics and Electronics, Chinese Academy of Sciences, Chengdu 610209, China)

Abstract: The median filtering has important application in image preprocessing stage, especially for filtering of impulse noise in image. The traditional median filtering algorithm is used to sort the original data according to its size to extract the median. The enlarged window size and increasing data cause the dramatical increase of comparison times, which becomes the bottleneck to restrict the real?time performance of big?window median filter. For this problem, a design method for the real?time median filter with 25 inputs based on FPGA is presented. It is unnecessary to sort the original data, but a new median is generated according to the information of each bit plane, which is particularly suitable for the filtering implementation based on FPGA. A special bit?processing unit was designed to simplify the circuit structure. The method of three?level lookup table can solve the time?consuming issue of “majority voter”. The experimental results show that the proposed filter has less sources occupation, high data throughput and short time delay, and can satisfy the filtering requirement of any window shapes.

Keywords: median filtering; digital filter; image processing; FPGA

中值滤波作为一种统计排序滤波在图像增强中有着广泛的应用,尤其对于脉冲噪声的滤除[1],它提供了一种优秀的去噪能力,且相比于同尺寸的线性平滑滤波,其能够带来更小的图像模糊。如今,对于3×3小窗口的中值滤波算法[2?3],已有众多研究,技术比较成熟。然而对于大窗口的中值滤波,因数据增多,造成比较运算次数成几何级数激增,这成为制约大窗口中值滤波实时性的一个瓶颈。为降低比较次数,文献[4?5]提出了基于均值加速和均值查找的滤波算法,然而计算均值本身就十分耗时,且从原始数据中取出中值需要几个时钟周期并不确定,不便于用硬件来实现。文献[6]提出了一种不完全排序的算法,但对于5×5的滤波窗口,依然需要多达108次比较运算,20级延迟,才可计算出中值。文献[7]提出了一种基于多级分组排序的滤波算法,把比较次数降低到了84次,只需要6级延迟即可取出中值,但这却是以牺牲数据吞吐率为代价的,无法满足更高速度的处理要求。有鉴于此,本文以FPGA为平台,设计了一种基于比特平面的中值滤波器,对原数据并未进行大小排序,而是根据各比特平面的数据结构,重新生成了一个中值;该滤波器对窗口形状无限制,对相邻区域数据无依赖,吞吐率高,延迟小,可满足高速、实时的滤波要求。

1 中值滤波原理

1.1 中值滤波基本原理

中值滤波的基本原理是对图像中某一像素点周围邻域的像素按照灰度级大小排列,并选取中间值代替该点像素值,以达到滤除噪声的效果。其滤波窗口根据具体需求可选择方形、十字形等。对于边缘像素点,滤波窗口可能覆盖到图像外侧无效数据。对此,一般的处理方式是对无效数据填充数据0或对边缘数据不进行滤波处理。

1.2 基于比特平面的中值滤波原理

本文以8位宽、5×5窗口的中值滤波器为例,说明基于比特平面的设计方法。对于任意8位宽的数据,可表示为如下形式:

[27b7+26b6+25b5+24b4+23b3+22b2+21b1+20b0]

式中:[bi=0或1;i=0,1,2,…,7。]

于是可将25个输入数据分别表示成如下行向量的形式:

[xTi=bi,7,bi,6,bi,5,bi,4,bi,3,bi,2,bi,1,bi,0]

式中:[i=1,2,…,25。]

记矩阵:

[A=xT1xT2 ?xT25=b1,7b1,6…b1,0b2,7b2,6…b2,0????b25,7b25,6…b25,0=y7,y6,…,y0]

设中值所对应的行向量表达式为

[mT=λ7,λ6,λ5,λ4,λ3,λ2,λ1λ0]

记函数

[?(yj)=1,向量yj中1的个数比0多0,向量yj中0的个数比1多]

式中:[j=7,6,…,0。]

为了确定向量[mT]中各元素的值,可通过如下步骤计算:

(1) 若25个原输入数据中,最高比特位1的个数比0多,则中值的最高比特位必然也为1,反之则为0,有:

[λ7=?(y7)]

(2) 假若[λ7=0],对于向量[xTi],若有[bi,7=1],则[xTi]所代表的数据必定大于中值,于是将[xTi]中所有元素全置1,而中值在原数据中的大小排序不会改变,以此来确保[λ6]生成的正确性;反之,对于[λ7=1],则将[xTi]中所有元素全置为0。即有:

[xTi=xTi,bi,j=λj1,1,1,1,1,1,1,1,bi,j≠λj,且bi,j=10,0,0,0,0,0,0,0,bi,j≠λj,且bi,j=0]

式中:[i=1,2,…,25;j=7,6,…,1。]

(3) 第(2)步更新完矩阵A后可再计算出[λ6]的值,即:

[λj=?(yj), j=6,5,…,0]

(4) 重复第(2)步和第(3)步,即可算出中值其他比特位的值。

2 基于比特平面的中值滤波的硬件设计

2.1 顶层电路结构设计

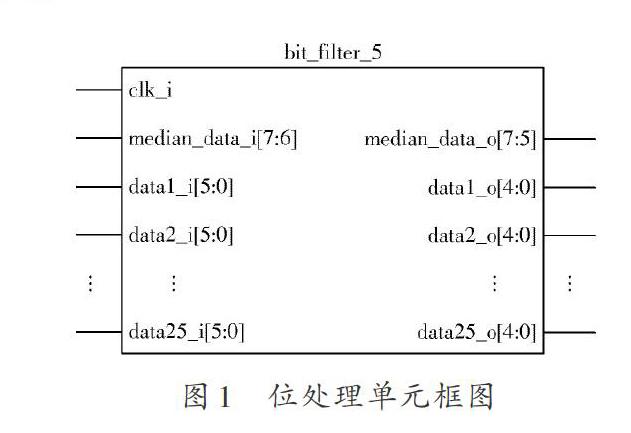

为简化电路结构,提高数据吞吐率,本文设计了一个bit_filter单元用来处理一个特定的比特平面。对于8位宽的像素数据,只需将8个bit_filter单元级联起来即可,其中每个bit_filter单元产生中值的一个比特位。为了便于说明,图1给出了j=5时,bit_filter单元的电路框图。

图1 位处理单元框图

图1中median_data为产生的中值,有:

median_data_o[7] = median_data_i[7] = [λ7],

median_data_o[6] = median_data_i[6] = [λ6],

median_data_o[5] = [λ5]

对于25个输入数据data1~data25来说,此时最高位和次最高位已不再需要,故输入端只用了低6位,输出端只输出了低5位供下级处理,以此来降低FPGA的资源消耗。其他各层面的bit_filter单元与此类似。

对于8位宽的数据,若每个时钟处理一个比特层面,则需要8个时钟的延迟方可算出中值。为降低延迟,也可以每个时钟处理2个或4个比特层面,此时只需要4级或2级延迟即可算出中值,但数据吞吐率也会随之降低。

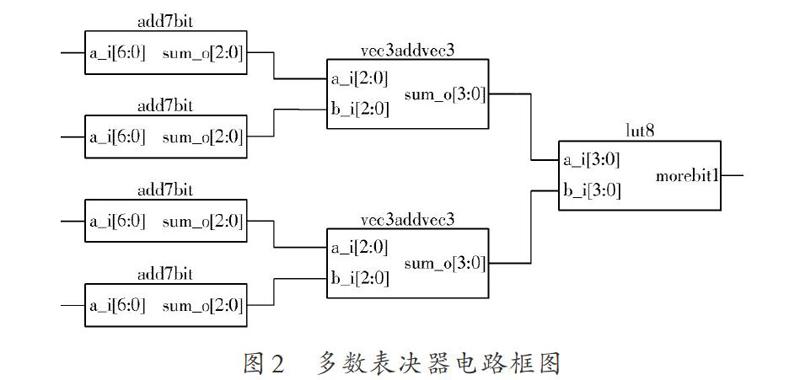

2.2 多数表决器的快速实现

在bit_filter单元中,[?(yj)]函数是限制整个系统速度的瓶颈。为解决这一问题,本文采用了三级查找表的方式来快速实现[?(yj)]函数,其顶层电路框图如图2 所示。

图2 多数表决器电路框图

首先将[yj]中的25个数据分为4组,每组7个,第4组补3个0。其中add7bit单元的作用是统计每组输入中1的个数,通过调用三个128深度的ROM来实现,每个ROM由两个6输入的查找表(LUT6)构成,用来输出一个比特位,将3个ROM的输出拼接起来即为sum_o(2:0)。vec3addvec3单元的作用是将两个3位宽的数据相加,其实现方式与add7bit类似。第三级采用一个256深度的ROM,将第二级算出的两个和作为地址,即可直接查找出[?(yj)]的值。经测试,在Xilinx 5vlx110tff1136?1芯片上,用该方式实现[?(yj)]函数共需消耗36个LUT6,计算时间仅需1.654 ns。

3 总体性能比较分析

在FPGA的设计中,如果单纯强调数据吞吐率是没有意义的,因为总可以通过插入多级寄存器,消耗更多资源来提高工作频率。根据前面所述的方法,本文在Xilinx 5vlx110tff1136?1 芯片上设计实现25输入的中值滤波器。同时,按照文献[7]的设计方法,在同款芯片上也实现了5×5窗口的中值滤波器。数据位宽为8,设计环境为ISE,综合工具为XST。表1列出两种设计方法在插入不同级寄存器时的性能和资源消耗情况。

表1 两种中值滤波器性能比较

表1中Algorithm_bit 为本文设计方法,Algorithm_7 为文献[7]的设计方法。表格中第4行为文献[7]的设计方法所能达到的最高频率,但此时需要22级的延迟。而本文的设计方法只需要8级的延迟就可使数据吞吐率达到308 MHz,同时资源消耗比文献[7]减少了大约40%。而对比前3行的数据可以发现,本文的设计方法在各方面均优于文献[7]。且文献[7]的滤波器仅适用于方形窗口,而本文设计的滤波器对窗口形状无任何限制。

4 结 语

本文在FPGA上设计一种基于比特平面的大窗口实时中值滤波器。根据原数据各比特层面的信息重新生成一个中值,而未对原数据进行大小排序,减少了资源消耗。为了解决多数表决器耗时长的问题,本文提出基于三级查找表的快速实现方式,大大提高了数据吞吐率。测试结果表明,采用本文方法设计的滤波器,资源消耗少,时延小,数据吞吐率高,可满足高速实时滤波的需求。

参考文献

[1] 冈萨雷斯,伍兹.数字图像处理[M].3版.阮秋琦,译.北京:电子工业出版社,2011:96?97.

[2] 付昱强.基于FPGA的图像处理算法的研究与硬件设计[D].南昌:南昌大学,2006:16?18.

[3] 沈学利,王肃国.基于FPGA的改进型中值滤波算法研究[J].微电子学与计算机,2014,31(1):21?24.

[4] 张丽,陈志强,高文焕,等.均值加速的快速中值滤波算法[J].清华大学学报(自然科学版),2004,44(9):1157?1159.

[5] 鲍华,樊瑜波,饶长辉,等.基于均值查找的快速中值滤波算法[J].四川大学学报(工程科学版),2011,43(2):76?79.

[6] 蒋涛,李自勤.基于FPGA的实时图像中值滤波算法及实现[J].微计算机信息,2012,28(10):196?197.

[7] 罗海波,史泽林,惠颖,等.基于多级分组排序网络的实时大窗口二维中值滤波器设计[J].红外与激光工程,2008,37(5):935?939.