高速电路PCB及其电源完整性设计

2016-05-11PCBofHighSpeedCircuitandtheIntegrityDesignforItsPowerSupply

PCB of High Speed Circuit and the Integrity Design for Its Power Supply

彭大芹 许海啸 谷 勇 万里燕(重庆邮电大学电子信息与网络工程研究院,重庆 400065)

高速电路PCB及其电源完整性设计

国家科技重大专项基金资助项目(编号:2012ZX03001012)。

修改稿收到日期: 2015-08-23。

第一作者彭大芹(1969-),男,2001年毕业于重庆邮电大学信号与信息处理专业,获硕士学位,高级工程师;主要从事移动通信终端、互联网、物联网以及车联网方向的终端协议和解决方案等方面的研究。

0 引言

目前,随着超高速集成电路技术的迅猛发展,印刷电路板(printed circuit board,PCB)设计技术也在日益推进[1]。作为PCB设计中最重要的部分,叠层结构的设计决定了PCB的整体性能[2]。具体来说,叠层结构包括了叠层的总层数、层厚度、不同类型层的层数及相对位置等方面[3]。所以本文首先对PCB的叠层结构进行了详细分析,重点分析了不同叠层结构下电源、地及信号层的相对位置对电源完整性的影响。

对于移动通信终端来说,最复杂的互连结构莫过于电源分配网络(power delivery network,PDN)。因为所有器件都直接或间接连接到PDN上,而PDN设计又是电源完整性设计的核心之一,这使得PCB的电源完整性设计已然成为业内关注的焦点[4]。一个好的PDN设计必须可以保证负载芯片有一个稳定、持续的电源供给,这是电源完整性的最终设计目的[5]。将PDN结构作为PCB电源完整性设计的切入点,通过对PDN结构的研究剖析,分析可能影响PCB电源完整性设计的因素;然后将这些因素作为变量,通过专业仿真工具Power SI对PCB进行PDN阻抗仿真;最后根据仿真结果验证PCB电源完整性设计方法的可行性与合理性。

1 PCB的叠层结构设计

1.1单板PCB的层数

单板的总层数,是指电源层数、地层数和信号层数的总和。在确定总层数时,要考虑到单板电源和地的种类、信号线的密集程度、板级的工作频率,尤其是高频部分、比较敏感的信号的特殊布线需求、单板性能指标的要求、成本以及电磁兼容(electromagnetic compatibility,EMC)指标等。

电源的层数是由电源的种类决定的。如果PCB只需要一个电源进行供电,那么一层电源就足够了。如果有多种电源供电,就要分为两种情况:一种是这些电源互不相交,那么可以采取电源层分割的方法;另一种是电源相互交错的情况,就要考虑两个及以上的电源平面。

地的层数是由电源和信号层来决定的。它要满足几个要求:一是关键的电源层要有对应的地层相邻,满足电源完整性的要求;二是关键信号,如时钟、高频、高速的一些信号需要有地层相邻;三是元器件的下面即第二层和倒数第二层一般要有一个完整的地平面。二和三这两种情况是为了获得更好的信号完整性。

信号层数的确定需要借助专业的PCB设计软件和有经验的工程师。工程师需要通过设计软件的布局和布线密度的参数,再结合板级工作频率、单板性能指标以及有特殊布线要求的信号数目估计所需信号层的数目[6]。

1.2信号、电源及地层的相对位置

信号层、电源层以及地层相对位置的确定有一些基本的原则,如所有信号层应尽可能与地层相邻、避免2个信号层直接相邻、主电源与对应地相邻等[7]。但是在实际的叠层设计时,一定要结合实际的情况,对这些原则灵活运用,不能生搬硬套。

下面对一些具体的PCB叠层结构进行分析,包括4层板、6层板、8层板、10层板。其中,S为signal,代表信号层; P为power,代表电源层; G为ground,代表地层。4层板叠层结构如表1所示。

表1 4层板叠层结构Tab.1 Stacked structure of 4-layer board

结构1是2层板中最常见的叠层方式。顶层布置器件,第2层地层为第1层提供参考平面,为满足电源完整性要求,第3层电源层与地层相邻,底层走非关键的信号线,第3层电源层也可为底层提供参考平面。

结构2较少用,因为2个信号层相邻,会产生信号完整性问题;电源层与地层相距较远,可能会产生电源完整性问题;元器件走在顶层,会造成地层和电源层的不完整,产生阻抗不连续的情况。但是结构2不会产生很大的电磁干扰(electromagnetic interferance,EMI)问题,这是因为顶层为GND,内层传输线的辐射得到很好的抑制,这是结构2最大的优点。

6层板叠层结构如表2所示。

表2 6层板叠层结构Tab.2 Stacked structure of 6-layer board

结构1是6层板中优先考虑的叠层方式。第3层与地层和电源层相邻,有良好的参考平面,是优先布线层;第4层电源层与第5层相邻,去耦效果良好,可以降低电源平面阻抗。

结构2适用于有成本限制、只能有一个地层的项目,所以优先选择第1层和第3层进行布线。

8层板叠层结构如表3所示。

表3 8层板叠层结构Tab.3 Stacked structure of 8-layer board

对于单电源的8层板来说,优先考虑结构1,第4层地层和第5层电源层相邻,保证了电源完整性,每个信号层都有较好的参考平面。

对于双电源的8层板来说,优先考虑结构2,结构2考虑到了无相邻布线层,电源层与地层相邻,信号都有参考平面等原则,但是由于底层的参考平面是电源层,所以底层不要走关键信号线。

结构3的底层相邻地层,信号完整性较好,但是电源与地相距较远,耦合较差,电源完整性问题严重。

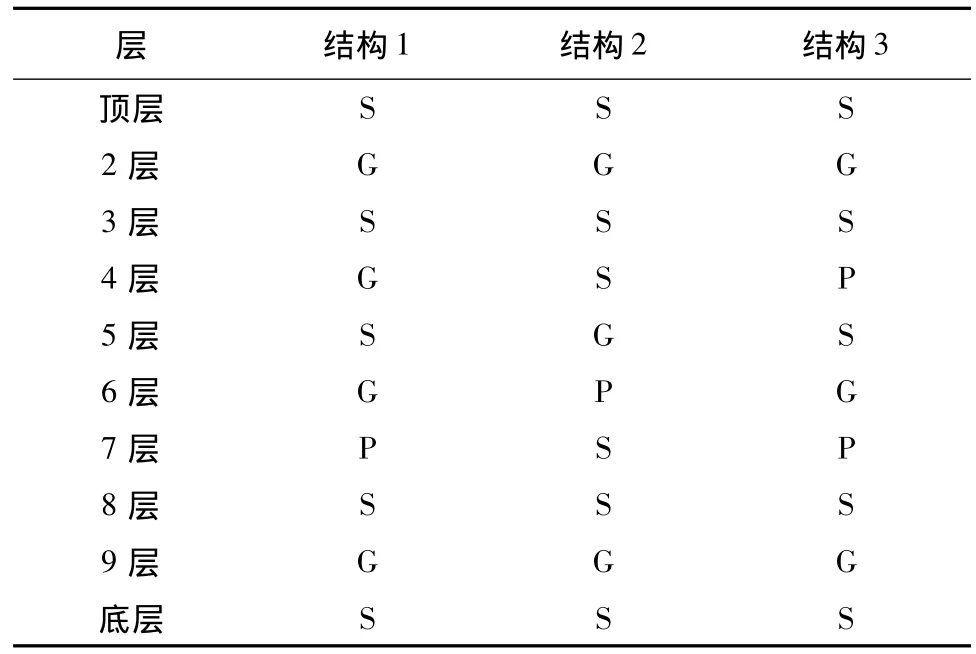

10层板叠层结构如表4所示。

表4 10层板叠层结构Tab.4 Stacked structure of 10-layer board

对于单电源的10层板来说,优先考虑结构1,结构1满足基本的设计原则,性价比较高。结构2有3层地,有明显的成本优势,但是有相邻的信号线,信号完整性较差。

对于双电源的10层板来说,优先考虑结构3,第3层、第5层以及第8层都可走关键信号线和敏感线,性价比较高。

对于12层及以上的单板PCB叠层结构设计,可选的组合方式较多,在此就不一一列举。最重要的是参考布线的一般原则,结合项目的实际需求和成本,进行具体分析。

2 PCB的电源完整性设计

2.1 PDN基本结构及分析

电源分配网络设计是解决电源完整性问题的关键。PDN包括从稳压模块到芯片的焊盘,再到裸芯片内分配本地电压和返回电流的片上金属层在内的所有互连[8]。PDN的基本结构如图1所示。

图1 PDN基本结构图Fig.1 Basic structure of PDN

由图1可以看出,PDN主要由稳压模块、体电容器、陶瓷去耦电容、PCB平面(包括电源平面和地平面)、封装等构成。

PDN设计的目的是提供一个从稳压模块到芯片负载低阻抗的路径,从而使得电流经过时不会产生很大的纹波噪声,最后到达负载的是一个稳定的电压。因此如何设计一个低阻抗的路径就成了PDN设计的关键,一般芯片规格书里会有具体的阻抗值,这个阻抗值被称为目标阻抗。

由公式Z = 2πfL可以看出,频率较高时回路电感L制约着阻抗。所以在进行PCB设计时必须考虑如何设计才能减小PDN路径上的回路电感,这样高频时回流路径上的阻抗才能够低于目标阻抗,符合PCB的电源完整性设计要求。

分析图1的PDN基本结构,可以得知PDN中的环路电感包括以下3部分:

①电源平面和地平面间的回路电感;

②元器件或芯片负载安装到PCB上的寄生电感;

③芯片内部的封装电感。

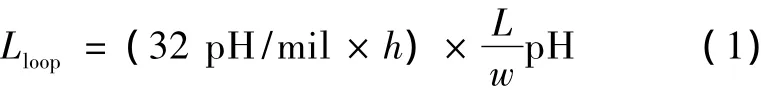

但是由于研究探讨的是PCB的PDN设计,所以只考虑电源和地平面之间的环路电感。平面之间环路电感由以下公式得到:

式中: h为电源和地平面之间的垂直距离; L为电源和地平面的长度; w为电源和地平面的宽度; pH/mil为磁导率单位。

由式(1)得知,环路电感值的大小与环路面积有关,面积越大,环路电感越大,所以减小环路电感最有效的方法就是减小环路面积。由式(1)可以推测,减小环路电感可以从两个方面进行:一是减小电源和地网络的长度L;二是减小电源和地网络的垂直距离h,即减小电源和地网络之间电介质厚度。

2.2 PDN仿真及仿真结果分析

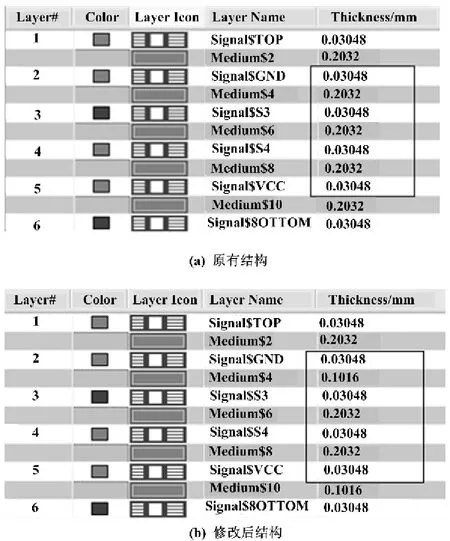

以影响PDN阻抗的因素为变量,利用仿真工具Power SI对PDN进行频域上的仿真,通过查看它的频率阻抗曲线,比较不同的电源平面和地平面距离对PDN阻抗造成的影响。此次仿真实例的PCB叠层结构如图2所示。

图2 PCB叠层结构图Fig.2 Stacked structure of PCB

由图2(a)可以看出,此次仿真的对象是一个6层的PCB,其中,第5层是电源层,第2层是地层,电源层与地层的距离是0.73 mm,相距较远。

通过比较修改前后的PCB叠层结构,可以看出电源层、地层和信号层的相对位置没有变化,变化的只有第2层地层和第5层电源层之间的垂直距离,距离改为0.53 mm。软件仿真得到的频率阻抗曲线如图3所示。

图3 频率阻抗曲线Fig.3 The curve of frequency vs.impedance

图3中,最高阻抗为78 Ω的曲线为修改前PCB叠层结构仿真得到的频率阻抗曲线,而最高阻抗为50 Ω的曲线为修改后的PCB叠层结构得到的频率阻抗曲线。通过比较仿真结果可以验证猜想,即PCB进行PDN设计时,尽量将电源与其对应的地平面相邻排布并且尽量靠近,从而减小平面间的回路电感,降低电源、地平面阻抗,使PCB设计满足电源完整性要求。图3中,600~700 MHz之间的阻抗峰值是由于PCB谐振引起,可以通过增加去耦电容来改进。

3 结束语

本文从PCB的设计出发,以正向思维方法,先研究PCB的总层数及不同类型层的层数;其次分析信号、电源及地层的相对位置对PCB设计的影响;最后从PDN结构入手,分析出可能影响PCB电源完整性设计的因素,将因素作为变量,对一个实际PCB进行仿真分析,验证PCB叠层设计及电源完整性设计的可行性与合理性。相信随着移动终端工作频率的不断提高,PCB及其电源完整性的设计也会越来越重要。

参考文献

[1]秦俊,李伟哲.基于改进目标阻抗的电源分配网络设计方法[J].电子科技,2013,26(5):74-77.

[2]张木水.高速电路电源分配网络设计与电源完整性分析[D].西安:西安电子科技大学,2009.

[3]王剑宇,苏颖.高速电路设计实践[M].北京:电子工业出版社,2012.

[4]陈兰兵,钟章民,肖定如.Cadence高速电路设计: Allegro Sigrity SI/PI/EMI设计指南[M].北京:电子工业出版社,2014.

[5]Madhavan S,Ege A.芯片与系统的电源完整性建模与设计[M].李玉山,张木水,译.北京:电子工业出版社,2009.

[6]于争.电源完整性设计详解[EB/OL].[2013-06-01].http: / /www.sig7.com.

[7]Eric B.信号完整性与电源完整性分析[M].李玉山,刘洋,译.北京:电子工业出版社,2015.

PCB of High Speed Circuit and the Integrity Design for Its Power Supply

彭大芹许海啸谷勇万里燕

(重庆邮电大学电子信息与网络工程研究院,重庆400065)

摘要:详细分析了印刷电路板(PCB)的叠层结构设计,包括单板总层数,信号、电源及地层层数,尤其是信号、电源及地层的相对位置排列。具体研究了PCB的电源完整性设计,分析了高速电路中的电源分配网络(PDN)结构,得出PCB设计中可能影响电源完整性设计的因素。基于这些因素,进行了仿真分析,仿真结果验证了PCB电源完整性设计的可行性与合理性。

关键词:PCB叠层结构电源完整性电源分配网络(PDN)电磁兼容电磁干扰

Abstract:The design of stacked structure for printed circuit board(PCB)is analyzed in detail,including total layer number of single board,layer numbers of signals,power supply and grounding,especially the relative arrangement position of signal,power and grounding layers.The integrity design of power supply for PCB is researched in detail.The structure of power delivery network (PDN)of high speed circuit is analyzed,the factors may affect the integrity design are obtained.Based on these factors,the simulation analysis is conducted; the results verify the feasibility and rationality of the integrity design of power for PCB.

Keywords:Printed circuit board(PCB)Stacked structurePower integrity Power delivery network(PDN)Electromagnetic compatibility Electromagnetic interference

中图分类号:TH7; TP21

文献标志码:A

DOI:10.16086/j.cnki.issn1000-0380.201603002