半导体集成电路可靠性测试及数据处理方法

2015-12-25雷凤霞潞安职业技术学院山西长治046204

雷凤霞(潞安职业技术学院,山西长治046204)

半导体集成电路可靠性测试及数据处理方法

雷凤霞

(潞安职业技术学院,山西长治046204)

摘要:可靠性是分析产品使用年限的一门全新学科,可以明确地反映出产品质量。随着全新的材料以及工艺的运用,半导体集成电路的线宽开始降低,集成度也不断提升,其对于集成电路可靠性也提出了更加严格的要求。近些年来,我国的集成电路制造产业开始得到快速的发展,这也为国内集成电路可靠性的研究创造了较好的条件。文章主要分析了半导体集成电路的晶圆级可靠性测试以及相关的数据处理手段。

关键词:半导体集成电路;可靠性测试;数据处理方法

随着半导体集成电路制造技术的快速进步和发展,以硅基单片数字为标志的超大规模集成电路体积不断缩减,电路结构以及制造工艺愈加繁杂。其可靠性受到工艺误差以及相关因素的影响也开始加重。因此为了确保集成电路工艺可靠性,并有效减少产品可靠性评价成本以及相关费用,愈来愈多的半导体集成电路厂商开始进行晶圆级的可靠性测试。

可靠性工程必须运用当前的现代科学技术,对产品功能进行系统考量,运用专门性的技术手段,降低产品故障率,最终确保系统运行良好。在集成电路的晶圆级可靠性测试中,使用非常普遍的测试类别主要是热载流注入测试、电迁移测试等等其他一些相关的测试项目。

一、热载流子注入测试以及数据处理方法

热载流子注入测试是半导体集成电路晶圆级可靠性测试中十分重要的一项目。其实际能量和费米能级相比较,大约超出几个kT以上的热载流子。在集成电路器件中,载流子在遗漏的源电压条件下到达漏电极限,这其中的原因就是漏端周围存在较高的电场强度区域,一旦载流子进入这个区域,便能够让这些高革的作用[J].中国新技术新产品,2011(17):234.

[4]余育仁,刘悦如.图书馆网上知识竞赛系统——高校图书馆资源利用新方式[J].上海高校图书情报工作研究,2011(01):38-40.

[5]郭诗维,雒晓卓.网络竞赛系统框架设计与功能模块实现[J].电脑编程技巧与维护,2011(10):84-85.

[6]潘振杰. ASP图书馆知识竞赛系统的构建与思考[J].电子世界,2012(04):54-56.

[7]陆永来.现场知识竞赛系统的设计[J].中国信息技术教育,2011,(19):65-66.

[8]朱森勇,周平.基于TCP/IP的通用型在线答题竞赛系统开发[J].电脑编程技巧与维护,2005,(06):70-71+74.

[9]归群峰.基于创新推广的学科竞赛网络支持系统的开发与研究[D].浙江师范大学,2011.

[10]王啸.电子设计预赛系统的研究与设计[D].北京邮电大学,2012.

[11]公慧玲,李致勋,邱睿韫.基于ADO的竞赛系统的设计与研究[J].数字技术与应用,2012,(08):137.能的能量子转变成为热载流子,而这种条件下的热载流子在电子的相互碰撞下成为新的电子空穴对,进行更深程度的电离。随着热载流子数量增多,能量也不断增加。热载流子测试一般都是对集成电路进行较长时间的电应力,同时在中间读点测量不同电性参数的数值。

编辑郑晶

图1 DS18B20初始化及读写控制时序

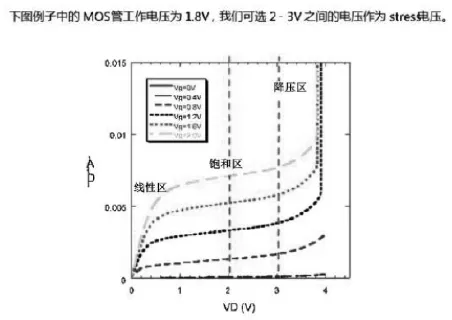

JEDEC国际标准的JESD28以及JESD60依次规定集成电路器件热载流子的测试过程以及整个的数据处理手段。以NMOS器件为范例如图1,图2所示。一般电性参数会按照时间的变化量同时演变为幂函数关系,也就是:Y(f)=Ctn,其中Y(t)为电性参数随时间的相对变化量:Y(t)=P(t)-P(0),其中P(0)是电性P(0)参数的原始数据,P(t)是电性的参数值在t时刻的素质。另外电性参数记录时间间隔常常选取数字表示,例如10s,30s,还有60s。

图2 HCI生存周期结果图

根据热载流子测试得出的数据处理结果和方法,在JESD28-1中重点介绍了NMOS器件所产生的热载流子测试数据的研究手段:1n Y(f)=1nC+n1nt,根据数学公式中的最小二乘法对得出的数据进行线性拟合之后,C与n这两个参数的数值就可以很好地算出来。一般的热载流子实验结果中数据的后期整理经常是根据原设定的参数C以及n的数值进行进一步的电性参数相对变化量Ytar的计算,让其达到某些预先设定的数值Ytar以及它所需的时间ttar。

试验中,不同的样品的ttarr往往会不断地用来预先判断热载流子测试的使用周期和最大寿命。在大多数情况下使用普遍的热载流子测试的寿命模型如下:"首先是衬底-漏电流比例模型:这当中的H,m可以看作是拟合线性参数,Isub是衬底电流,Id是漏电流的含义,W则是MOS的栅宽度。漏源性的电压加速物理模型详细的公式是中的t0、B可以作为模拟拟合的参数,Vds是漏源电压的含义。漏源电压的加速物理模型是利用不同条件下所要测量样品的ttar和Vds数值获取的拟合性参数to和B,在次基础上得到了正常合适物理条件和因素影响下热载流子的寿命。衬底一漏电流比例物理模型则是利用品的ttar和Isub等得到了拟合参数H、m,从而也得到了合适环境和条件下热载流子测试的寿命;最后的物理模型是衬底电流模型,具体的公式如图,其中C、b为拟合参数,Isub为衬底电流,w则为MOS中的栅宽度。衬底电流物理模型是在不同测试环境和条件下不同样品的tta,ISub数值得到的拟合参数C和b,最后得到了在正常环境条件下热载流子测试的寿命[1]。

二、栅氧化层测试以及数据处理方法

栅氧化层对于集成电路的制造而言可谓是很关键。栅氧化层的厚度会随着集成电路规模而扩大,以及器件体积的减小而不断减小。由于栅氧化层的作用很重要,所以栅氧化层可靠性问题也是极为瞩目的,其中较为引人注意也是较为常见的问题是栅氧化层的缺陷密度以及介质穿击问题。栅氧化层的可靠性测试主要是在同一时间内有联系介质的穿击测试和斜坡电压测试。其中,斜坡电压测试是指在栅极的上面加线性斜坡电压,一直到该电压将氧化层击穿为止。斜坡电流测试和斜坡电压的测试略有区别,是把一定指数的斜坡电流加在栅极之上,直到能够击穿氧化层为止。斜坡电业测试和斜坡电流测试均是为了测量出栅氧化层缺陷密度的。例如,在斜坡电压测试当中,一般情况下,是将斜坡电压测试规定在一定的电压标准之内,如果出现测试样本被击穿时的电压小于事先设定的电压标准的情况,就能够认定这是由于氧化层中有一定的缺陷导致的,并能够进一步认定该栅氧化层是没有效果的。如果依照JESD35中的标准而言,缺陷密度用基于Poisson分布的成品率公式来得到:Y=e-DoA,其中,Y表示成品率,这也可以认为是(有效样品数)/(总测试样品数)而A则代表受测样品的面积,Do代表所需计算出来的缺陷密度。在利用斜坡电流和斜坡电压对成品经过大量的测试后,应当算出Y的数值(成品率),并进一步利用A的数值(测试样品面积)得出Do(缺陷密度值)。一旦Do的数值越过了设置标准,这种情况下的测试就是失败的。

另外,则是介质击穿的实验。这个实验是指时间相关介质击穿。介质击穿测试如下:首先在栅极加以小于栅氧化层的本征击穿场强,这并不能造成本征击穿,可由于施加电应力的过程当中氧化层出现了一定的缺陷,这种情况下,经过一段时间以后就会出现击穿现象了。相同时间下相关栅氧介质的击穿被看作是限制集成电路可靠性评定的重要因素,一般情况下击穿现象是氧化硅当的电场超过限制,电流过高,才造成的电荷累积反应。现阶段,把整个氧化层被击穿的过程分为两个主要阶段,他们分别是构建磨损阶段和击穿阶段。其中,构建磨损阶段当中,二氧化硅的界面存在于电应力的运作之下,其中的缺陷就会不断累积。当累积数值达到一定量时,某些部分的缺陷数就会到达一定的临界值,并由量变产生质变,一举进入击穿阶段。当进入击穿阶段之后,电、热的双重作用之下,就会迅速的将氧化层击穿。因此,构建磨损阶段持续时间的长短决定了栅氧介质击破测试的年限。

三、电迁移测试以及处理方法

金属相互连线的电迁移情况通常都是按照集成规模的扩展速度不断变化,其集成器件的体积不断缩减,户连线电流密度不断提高,在电迁移的测试逐步开始占据了非常关键的地位。在物理现象中集成电路中的电迁移现象详细的表达方式就是,集成电路的不同器件在实际生产和实验的过程中,金属之间的互连线中有的电流通过,其中金属阳离子会根据导体的质量的进行电子的传输,这可以使得导体的某些空间出现空洞现象和小丘等不同的物理现象。集成电路中的的电迁移现象在实际中大多数都是在“强电子风”的影响和作用下进行的,当电子从负极流向电源的正极的时候,会受到一定的能量碰撞,其中的金属阳离子可以先正极不断的移动,而负极则产生一些空的穴位,在这个过程中不断地进行增加和积累,可以让金属形成短路,同时由于正极的金属离子的累积作用而使得出现晶须现象,而且有非常大的概率使得周边的金属线发生短路的现象[3]。

往往在电迁移的实验和测试中我们常常让样品在不同的压力和温度条件下进行恒定的加速的物理测试实验。这往往是加速过程中应力测试不应当更改器件的失效的机理,正常水平下不同应力条件下Lognormal的分布以及对数标准差是往往是相等的。有了不同的应力条件下不同的样品的使用年限数据,再根据Lognormal分布的估算方法和标准就可以得到同应力下的中位寿命,进而利用加速运动的物理模型就可以得到在正常情况下电迁移寿命分布的实际情况,然后得到不同的累积失效率情况下使用寿命的初步判断[4]。

总而言之,本文主要分析了半导体集成电路的晶圆级可靠性测试以及相关的数据处理手段,以期能够更加促进半导体集成电路的技术突破。从我国目前半导体集成电路的发展来看,要加强其相关测试技术的基础研讨,构建满足我国实际的可靠性保证流程,同时还应该构建和颁布相应的标准和要求,这对于提高我国集成电路产业的未来发展而言具有决定性的影响。

参考文献:

[1]许斌.采用TEG技术的半导体集成电路可靠性评价方法[J].微电子学,2012,06(20):856.

[2]秦国林,许斌,罗俊.集成电路圆片级可靠性测试[J].微电子学,2013,01(20):144-145.

[3]陈光浩.基于嵌入式Linux的集成电路老化测试设备软件系统的设计与实现[D].杭州电子科技大学,2013(12):13-22.

[4]许丹.基于图像处理上几乎的多约束通孔插入方法研究[D].西安电子科技大学,2013(12):14-20.

编辑朱荣华

作者简介:雷凤霞(1982-),女,山西汾阳市人,硕士,潞安职业技术学院助理讲师,研究方向为电子技术。

收稿日期:2015-02-09

文章编号:2095-8528(2015)04-100-03

文献标识码:A

中图分类号:TN3