沟道尺寸对深亚微米GGNMOS保护器件特性的影响

2015-12-22吴晓鹏杨银堂刘海霞

吴晓鹏,杨银堂,刘海霞,董 刚

(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

沟道尺寸对深亚微米GGNMOS保护器件特性的影响

吴晓鹏,杨银堂,刘海霞,董 刚

(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

基于测试结果,研究了不同沟道宽度、沟道长度对深亚微米单叉指栅接地N型金属氧化物半导体静电放电保护器件性能的影响机制,并得出保护器件沟道尺寸的优化准则.基于SMIC 0.18μm CMOS工艺进行流片及传输线脉冲测试,得到了不同版图参数条件下保护器件的I-V特性.基于失效电流水平变化趋势以及器件仿真结果,分析了相关物理机制.研究结果表明,沟道宽度的选取必须结合器件的导通均匀性情况,同时沟道长度值则通过改变器件沟道下方的热分布影响保护器件的鲁棒性.利用实验方法分析了沟道尺寸对单叉指栅接地N型金属氧化物半导体保护器件性能影响的物理机制,对深亚微米保护器件的版图设计提供了优化指导.

沟道宽度;沟道长度;静电放电;栅接地N型金属氧化物半导体

静电放电(ElectroStatic Discharge,ESD)保护器件的设计必须要考虑众多寄生效应以及布局因素的影响,这些因素对保护器件流片后具有的防护性能起着决定性作用[1-4].尤其在深亚微米工艺下,大尺寸静电放电保护器件更加容易受到版图布局以及工艺因素的影响.在设计过程中,若完全遵循静电放电设计规则,可以保证器件能满足最低的静电放电防护要求,例如达到人体放电模式(Human Body Mode,HBM)耐受电压不低于2 k V.但若要从版图面积优化的角度考虑,则有必要分析关键版图参数对保护器件性能的影响,并确定特定工艺下的最优参数取值,达到与静电放电水平的良好折中.

根据以往设计经验,一般通过将栅接地N型金属氧化物半导体(Gate Grounded Negative channel Metal Oxide Semiconductor,GGNMOS)保护器件的沟道长度选取为静电放电设计规则允许的最小值,而沟道宽度则在允许面积内设计得尽可能大,以期实现较高的保护性能[1,5-8].但在新的工艺和更小特征尺寸条件下,该经验法则是否仍然适用是需要分析研究的.笔者通过对基于中芯国际集成电路制造有限公司(Semiconductor Manufacturing International Corporation,SMIC)0.18μm互补金属氧化物半导体(Complementary Metal Oxide Semiconductors,CMOS)工艺流片实现的单叉指结构栅接地N型金属氧化物半导体保护器件进行传输线脉冲(Transmission Line Pulse,TLP)测试,并结合器件仿真分析,研究保护器件版图面积的关键参数沟道宽度W、沟道长度L对保护性能的影响并分析其物理机制,最终实现对保护器件版图优化的设计指导.

1 栅接地N型金属氧化物半导体保护器件关键版图参数

栅接地N型金属氧化物半导体保护器件是集成电路设计中最常见的静电保护器件,它与核心功能电路实现工艺相兼容,不需要引入额外的工艺步骤,具有很好的成本效益.通常在设计此类器件时会设置较大的宽长比,其栅极和源极同时接地,漏极则连接到需要保护的输入/输出焊盘(Input/Output PAD).文中所讨论的器件在流片时采用了硅化物屏蔽(SAlicide Blocking,SAB)工艺以实现更加优良的保护性能.保护器件的关键版图参数有:沟道宽度、沟道长度、漏极接触孔到栅距离(Drain Contact to Gate Space,DCGS)、源极接触孔到栅距离(Source Contact to Gate Space,SCGS)以及源极扩散到衬底接触扩散距离(Sourcediffusion to Bulk-contact-diffusion space,SB).笔者所研究的单叉指栅接地N型金属氧化物半导体结构依据文献[9]的热分析方法将DCGS和SCGS分别设定为2.6μm和0.75μm,而SB值的选取则依据了文献[10]中关于保护器件触发电压的设计要求而最终设定为2μm.

2 沟道宽度对栅接地N型金属氧化物半导体器件的特性影响

通常为了达到一定的静电放电水平需要较大的器件宽度,但是对于常采用多叉指结构实现的栅接地N型金属氧化物半导体保护器件来说,其单个叉指宽度的选取往往是根据设计者的经验来选取的.通过测试分析栅接地N型金属氧化物半导体保护器件的单个叉指宽度对静电放电性能的影响,笔者研究了相关物理机制并为最优单叉指宽度值的选取提供理论依据.

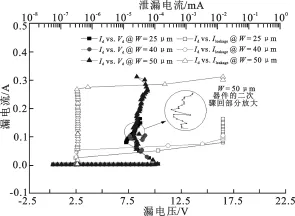

针对在SMIC 0.18μm CMOS工艺下流片实现的单叉指栅接地N型金属氧化物半导体器件,图1给出了对其进行传输线脉冲测试得到的I-V特性曲线以及对应的泄漏电流曲线.器件沟道长度为0.8μm,沟道宽度分别为25μm、40μm和50μm.可以看出,单叉指栅接地N型金属氧化物半导体器件的沟道宽度的增大对触发电压Vt1和保持电压Vh没有显著影响.以泄漏电流水平作为失效标准,观察发现二次击穿电流It2在W为50μm时显著增大.同时观察到单叉指宽度达到50μm时的I-V特性出现了轻微的二次骤回现象,这意味着保护器件叉指可能出现了不均匀导通现象[11-12].

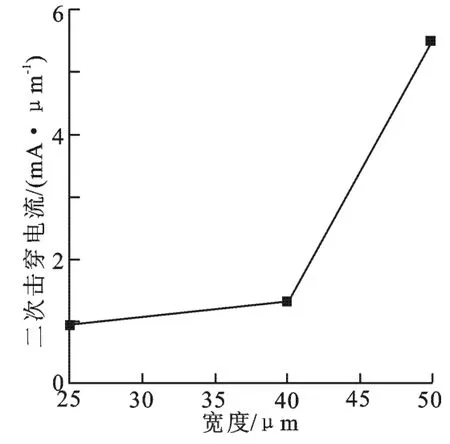

为了能够评估不同单叉指宽度的保护器件性能,图2给出单位宽度上的二次击穿电流水平.从图中可以看出,当单叉指器件宽度增大时,器件的保护性能也随之提高,且在宽度为50μm处达到约5.5 m A/μm的防护水平.而深亚微米保护器件达到5 m A/μm的静电放电水平就能够满足电路防护要求[13].

研究表明,雪崩倍增通常始于电场最大的漏衬结靠近沟道处[14].由于此处的PN结曲率导致雪崩电流在宽度方向上分布非常不均匀,因此在较大的器件宽度下无法保证其寄生横向NPN(Lateral NPN,LNPN)晶体管在整个宽度方向上全部导通,而是取决于保护器件源漏极在宽度方向上的电场分布情况.文献[15]中的微光显微镜失效分析图也表明,对基于非硅化物工艺实现的单叉指栅接地N型金属氧化物半导体器件在60 m A的电流驱动下,其80μm的单个叉指宽度方向上仅导通了约1/10且导通位置不连续.因此,结合文中的测试结果可知,当单叉指器件宽度取值超过某临界值时,会导致二次击穿电流值显著减小,无谓地增大器件宽度并不能换取性能的提升.综上所述,将笔者所设计的单叉指栅接地N型金属氧化物半导体保护器件宽度设定为50μm可避免出现显著不均匀导通,并且实现所需的静电放电防护水平.

图1 不同宽度单叉指栅接地N型金属氧化物半导体保护器件的传输线脉冲测试曲线

图2 单叉指栅接地N型金属氧化物半导体单位宽度上It2的变化趋势

3 沟道长度对栅接地N型金属氧化物半导体器件的特性影响

3.1 不同沟道长度的测试结果

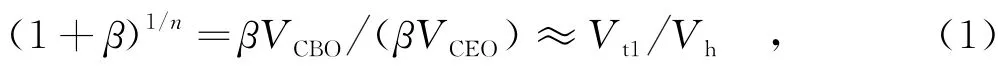

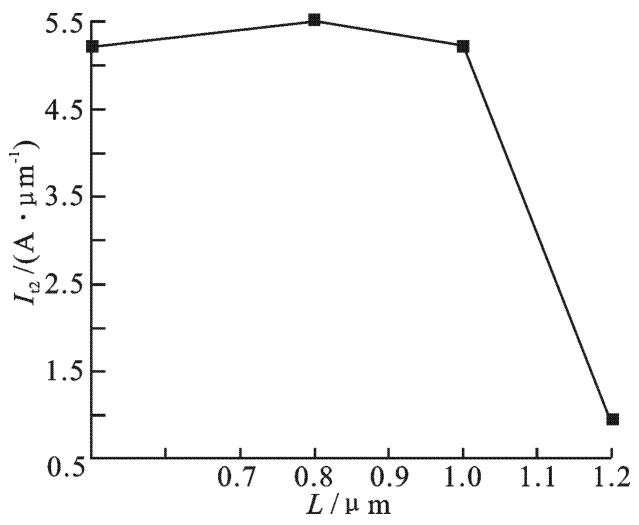

图3给出器件宽度取上述分析得到的优化值50μm,沟道长度分别取0.5μm、0.8μm、1μm和1.2μm时的I-V特性.当沟道长度增大时,保护器件的保持电压Vh呈增大趋势,这是由于较小的沟道长度可使寄生LNPN获得较大增益,也就是说可以在较小的电压偏置下维持寄生LNPN的导通状态.由于栅接地N型金属氧化物半导体的寄生LNPN电流增益β在自偏置模式下正比于触发电压与保持电压之比,即

图3 不同沟长单叉指栅接地N型金属氧化物半导体保护器件的传输线脉冲测试曲线

其中,VCBO为共基极结构击穿电压,VCEO为共射级结构击穿电压,n为常数.因此,从图4所示测试所得Vt1Vh值与沟长的关系曲线可以验证电流增益与沟道长度的反比关系.据此有文献推断具有较小沟道长度的器件较易导通且功耗较小,所以可以获得最大的二次击穿电流和HBM水平[17].

为了验证保护器件性能是否如预期的那样随沟道长度的减小而得到提升,给出图5所示的单位宽度二次击穿电流随沟长的变化趋势.观察发现,在沟道长度从0.5μm增大到1.2μm的过程中,保护器件的最大单位宽度二次击穿电流值并没有出现在最小沟长值0.5μm处,而是位于沟长值相对较大的0.8μm处.同时,当沟长增大到1.2μm时,单位宽度It2值呈现出较大的下降趋势.这与以往文献得出的结论存在差异.为了解释该现象,有必要进一步分析不同沟道长度器件的内部工作情况.

3.2 器件仿真分析

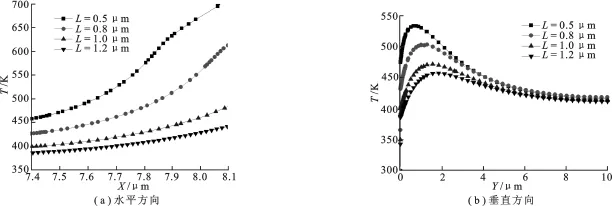

根据栅接地N型金属氧化物半导体保护器件的工作机理可知,失效电流的取值主要与保护器件的热效应相关,并且绝大多数的器件失效均是由电流过于聚集导致器件局部发热,最终发生硬失效.据此推断从传输线脉冲测试结果得到失效电流随沟道长度增大而减小的趋势,其原因可能是由于较短沟道器件中沟道下方的电流在静电放电应力期间急剧增大,同时由于较短沟道器件的热容积较小使得热量无法及时散发,从而导致其二次击穿电流水平偏低.而具有较长沟道长度的器件其电流分布可相对较为分散,因此发生热损伤的几率降低,保护器件可以获得较高的鲁棒性水平.为了验证上述推断,笔者通过对不同沟长保护器件进行器件仿真,得到如图6所示的温度分布曲线.

图4 保护器件的Vt1Vh比值与沟长的关系曲线

图5 单叉指栅接地N型金属氧化物半导体保护器件二次击穿电流随沟长的变化关系

图6 保护器件沟道下方的温度分布情况

从图6(a)发现,越靠近漏极方向,沟道下方的温度就越高,这是漏极靠近沟道方向发生的强烈碰撞电离导致的.同时,由于短沟道器件的沟道下方有更多的电流聚集,使得温度升高很快,短沟道器件的温度峰值比长沟道器件高出近1倍.图6(b)所示为沟道下方靠近漏结处垂直方向上的温度分布情况.观察发现,长沟道器件的温度峰值最低,且分布位置相比短沟道器件更加深入衬底,位于约2μm处;而短沟道器件的温度峰值则更靠近器件表面,位于约0.8μm处.通过上述分析可知,较短沟道器件虽然具有较小的保持电压因而降低了器件功耗,但是由于散热容积问题将导致其静电放电鲁棒性并没有得到预期的提升,所以沟道长度的选择需要在功耗与热损耗之间折中考虑.对于文中的情况,将沟道长度设定为0.8μm时,保护器件可在不过多占用版图面积的前提下具有最佳的静电放电鲁棒性.

4 总 结

基于0.18μm CMOS工艺,笔者对具有不同沟道宽度和沟道长度的单叉指栅接地N型金属氧化物半导体保护器件进行了流片以及传输线脉冲测试分析.测试结果表明,保护器件失效电流水平随沟道宽度的增加而提升的同时也出现了不均匀导通现象,并且保护器件并未在最小沟道长度时获得最佳保护性能.基于传输线脉冲测试结果分析了保护器件在宽度方向上部分导通的物理机制.利用热分析方法研究了减小沟道长度产生的散热容积问题及其对静电放电鲁棒性的影响.这项研究工作对深亚微米栅接地N型金属氧化物半导体静电放电保护器件的版图优化设计具有一定的参考意义.

[1]Liou J J.Challenges of Electrostatic Discharge(ESD)Protection in sIlicon Nanowire Technology[C]//Proceedings of the 18th International Conference on Microelectronics.Piscataway:IEEE Computer Society,2012:11-13.

[2]王源,贾嵩,孙磊,等.栅耦合型静电泄放保护结构设计[J].物理学报,2007,56(12):7242-7247. Wang Yuan,Jia Song,Sun Lei,et al.Design of a Gate-coupled Electrostatic Discharge Protection Structure[J].ActaPhysica Sinica,2007,56(12):7242-7247.

[3]Jiang Y X,Li J,Ran F,et al.Influence of Layout Parameters on Snapback Characteristic for a Gate-grounded NMOS Device in 0.13μm Silicide CMOS Technology[J].Chinese Journal of Semiconductors,2009,30(08):82-89.

[4]刘红侠,刘青山.0.18μm CMOS工艺下的新型ESD保护电路设计[J].西安电子科技大学学报,2009,36(5):867-870. Liu Hongxia,Liu Qingshan.Analysis and Design of Novel ESD Protection Circuit in 0.18μm CMOS P5rocess[J]. Journal of Xidian University,2009,36(5):867-870.

[5]Linten D,Vassilev V,Thijs S,et al.Anti-series GGNMOS ESD Clamp for Space Application IC’s[C]//Electrical Overstress/Electrostatic Discharge Symposium Proceedings.New York:ESD Association,2014:1-7.

[6]Abou-Khalil M J,Gauthier Jr R J,Lee T C,et al.Bi-directional Back-to-back Stacked SCR for High-voltage PIN ESD Protection,Methods of Manufacture and Design Structures:US,8503140B2[P/OL].[2013-06-08].http://www. freepatentsonline.com/8503140.html.

[7]Xie H L,Zhang R Y,Wang A,et al.Real 3D Electro-thermal Simulation and Analysis for ESD Protection Structures [C]//Proceedings of the IEEE International Caracas Conference on Devices,Circuits and Systems.Piscataway:IEEE,2004:61-64.

[8] 朱志炜,郝跃,方建平,等.静电放电应力下深亚微米栅接地NMOSFET源端热击穿机理[J].西安电子科技大学学报,2006,33(6):911-916. Zhu Zhiwei,Hao Yue,Fang Jianping,et al.Investigation of the Source Soide Thermal Breakdown Mechanism in the Deep Submicron Technology GGNMOSFET under ESD Conditions[J].Journal of Xidian University,2006,33(6):911-916.

[9] 张冰,柴常春,杨银堂.源、漏到栅距离对次亚微米GGNMOS ESD保护电路鲁棒性的影响[J].物理学报,2010,59 (11):8063-8070. Zhang Bing,Chai Changchun,Yang Yintang.Effect of Distances from Source or Drain to the Gate on the Robustness of Sub-micron GGNMOS ESD Protection Circuit[J].Acta Physica Sinica,2010,59(11):8063-8070.

[10]吴晓鹏,杨银堂,高海霞,等.基于深亚微米工艺的栅接地NMOS静电放电保护器件保护器件衬底电阻模型研究[J].物理学报,2013,62(4):47203. Wu Xiaopeng,Yang Yintang,Gao Haixia,et al.A Compact Model of Substrate Resistance for Deep Sub-micron Gate Grounded NMOS Electrostatic Discharge Protection Device[J].Acta Physica Sinica,2013,62(4):47203.

[11]Lee J H,Wu K M,Huang S C,et al.The Dynamic Current Distribution of a Multi-fingered GGNMOS under High Current Stress and HBMESD Events[C]//Proceedings of IEEE International Reliability Physics Symposium. Piscataway:IEEE,2006:629-630.

[12]Meng K H,Rosenbaum E.Layout-aware,Distributed,Compact Model for Multi-finger MOSFETs Operating under ESD Conditions[C]//Electrical Overstress/Electrostatic Discharge Symposium Proceedings.New York:ESD Association,2013:6635912.

[13]Duvvury C,Ramaswamy S,Amerasekera A,et al.Substrate Pump NMOS for ESD Protection Applications[C]// Electrical Overstress/Electrostatic Discharge Symposium Proceedings.New York:ESD Association,2000:7-17.

[14]Johnsson D,Pogany D,Willemen J,et al.Avalanche Breakdown Delay in ESD Protection Diodes[J].IEEE Transactions on Electron Devices,2010,57(10):2470-2476.

[15]Oh K H,Duvvury C,Salling C,et al.Non-uniform Bipolar Conduction In Single Finger NMOS Transistors and Implications for Deep Submicron ESD Design[C]//Annual Proceedings of Reliability Physics Symposium.Piscataway: IEEE,2001:226-234.

[16]Sze S M,Ng K K.Physics of Semiconductor Devices[M].New York:Wiley,2006:62.

[17]Amerasekera E A,Duvvury C,Anderson W,et al.ESD in Silicon Integrated Circuits[M].New York:Wiley,2002: 328.

(编辑:郭 华)

Research on the influence of the channel dimension on the characteristics of the gate grounded NMOS protection device

WU Xiaopeng,YANG Yintang,LIU Haixia,DONG Gang

(Ministry of Education Key Lab.of Wide Band-Gap Semiconductor Materials and Devices,Xidian Univ.,Xi’an 710071,China)

The effect of the channel width and channel length on the single finger GGNMOS ESD protection device based on the deep sub-micron technology is researched,which gives the insight into the selection of the optimum value for the channel.The I-V characteristic of the protection device with various layout parameters results from the tapeout based on the SMIC 0.18μm CMOS process and the TLP test. The physics mechnism is detailed based on the variation tendency of the failure current level and the device simulation.The results show that the selection of the channel width should consider the on-off uniformity and that the channel length affects the robustness of the protection device by changing the heat distribution under the channel.This paper analyzes the physical mechnism of the effcts of the channel dimension on the single finger GGNMOS protection device and gives the guidauce for the optimum layout design of the deep sub-micron ESD protection devices.

channel width;channel length;electrostatic discharge;gate grounded negative channel metal oxide semiconductor

TN406

A

1001-2400(2015)06-0113-05

10.3969/j.issn.1001-2400.2015.06.020

2014-12-31

时间:2015-03-13

陕西省科技统筹创新工程计划资助项目(2011KTCQ01-19);中央高校基本科研业务费专项资金资助项目(K5051325011)

吴晓鹏(1979-),女,西安电子科技大学博士研究生,E-mail:xpwu@mail.xidian.edu.cn.

http://www.cnki.net/kcms/detail/61.1076.TN.20150313.1719.020.html