一种新型P沟道VDMOS复合耐压终端

2015-12-22张得玺

蒲 石,杜 林,张得玺

(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

一种新型P沟道VDMOS复合耐压终端

蒲 石,杜 林,张得玺

(西安电子科技大学宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

针对终端结构耐压的提高,研究了高压P沟道垂直导电双扩散型场效应晶体管的场限环和场板复合耐压终端结构,提出了一种采用单N+偏移区场限环和多级场板复合的耐压终端结构.仿真发现,该结构能更有效地改善器件主结的边缘电场分布,从而提高了器件的整体击穿电压.根据以上理论,将该结构运用在一款大功率P沟道垂直导电双扩散型场效应晶体管器件上.经流片测试结果表明,该P沟道垂直导电双扩散型场效应晶体管器件样品的击穿电压为-90 V,与仿真结果中主结击穿电压达到-91 V有很好的吻合,证明了该结构设计的正确性.

P沟道垂直导电双扩散型场效应晶体管;终端结构;场限环;N+偏移区;多级场板

垂直导电双扩散型场效应晶体管(Vertical Double-diffuse MOSFET,VDMOS)作为一种重要的功率器件,因其具有输入阻抗高、开关速度快和驱动功率低等优点在开关电源、直流转换、电机驱动控制等领域得到广泛运用.近年来,N沟道VDMOS器件的研制在国内取得了重大突破,而P沟道VDMOS由于性能相对较弱且运用领域狭窄,国内对其研究十分匮乏.目前,P沟道VDMOS器件主要用于图腾柱式功率管组电路与高压端联接的控制开关中,相比于N沟道VDMOS的运用,其既减少了高压电平位移电路,也不存在高侧开关与低侧开关的信号同步问题,具有不可替代的优势[1].作为VDMOS最重要的指标,其能承受的反向关断电压在很大程度上是由终端结构决定的,这是因为位于VDMOS器件中间的有源区,由于并联的元胞之间互相耗尽,它们之间的表面电压大致相等,电场强度相对较低;而处于器件边缘处的PN结(主结),在VDMOS处于关断状态时,主结与衬底之间和有源区一样存在着源漏电压VDS,而主结为浅平面结工艺制作形成的柱面结,一般结深为4~7μm,曲率半径较小,这导致其耗尽区边缘处的电场强度远大于有源区耗尽区的电场强度[1-3].随着VDS的增加,此处将因较高的电场强度而先于有源区发生雪崩击穿.因此,需要在主结附近加入终端结构以降低该处的电场强度,提高击穿电压.经仿真结果分析发现,如不采用终端结构,主结的击穿电压将比有源区元胞的击穿电压低40%以上,即使采用了常规终端结构,主结击穿电压一般也仅有平行平面结的80%左右[4].

笔者重点研究了高耐压P沟道VDMOS结构,通过对场限环和场板相关理论进行分析研究,提出了一种用于P沟道VDMOS器件的复合场限环和多级场板结构,该结构能有效改善P沟道VDMOS器件主结的电场分布,将其击穿电压提高到与有源区相当的水平,从而提高了器件的整体耐压.

1 结终端结构的简单理论

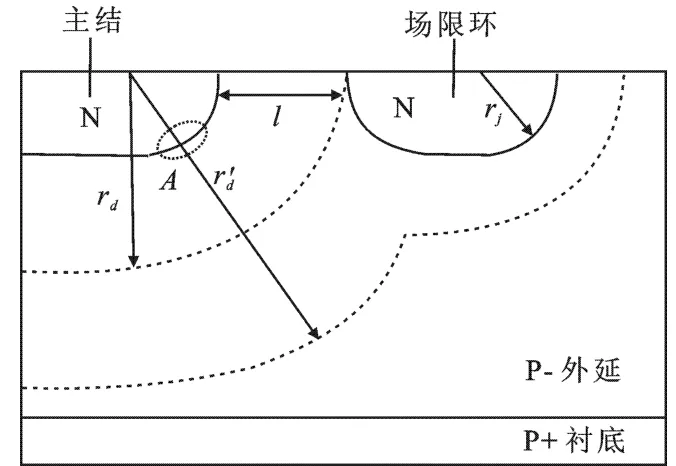

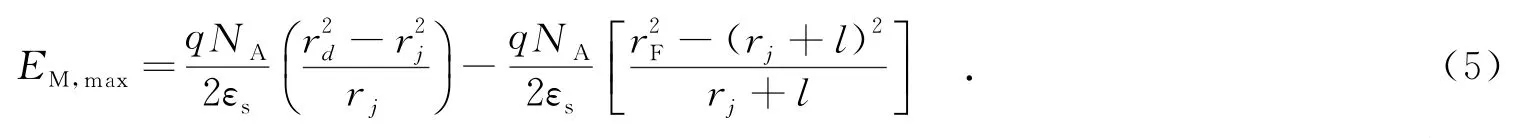

场限环和场板结构对提高VDMOS的击穿电压十分有效.场限环是在扩散形成VDMOS体区和沟道区的同时,在主结外侧制作1个或多个与衬底杂质相反的重掺杂环状结将主结包围起来,这些环状结与元胞区或其他电极并无电接触,因此也称之为浮空场限环(Floating Field Limiting Ring,FFLR),其基本结构如图1所示.其基本原理是,在主结反偏电压作用下,主结的耗尽区逐渐向边缘扩展,在电压还未增加到主结的雪崩击穿电压之前,主结的耗尽区扩展到场限环的耗尽区部分,使得两个结的耗尽区交叠,此时主结与场限环处于穿通状态[3],使得场限环电位提高.如果主结上的电压继续增加,则耗尽层将向场限环外侧扩展,使得增加的电压落在场限环上以分担主结电压.由图1可以看出,场限环的存在使主结耗尽区的曲率半径由r′d增加到rd,降低了边缘处的电场强度,并且主结与场限环之间的间距l对耗尽区的曲率半径起主要作用.场板的作用是通过改变表面电势的分布来增加主结的曲率半径,抑制表面电场集中,从而达到提高器件击穿电压的目的[4-5].

图1 场限环结构剖面图

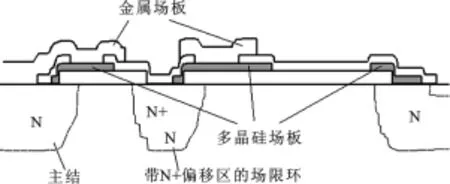

图2 文中设计的结终端结构剖面图

2 终端复合结构与实现

场限环的制作工艺简单,可与主结同步制作形成,而且能明显提高主结的耐压值,但这种浅平面结结构对表面电荷非常敏感,表面电荷的存在会导致表面电场的集中和不稳定,从而明显影响到器件的耐压特性[2].而场板可以有效改善表面电荷分布,使得采用该技术的器件对界面电荷不是很敏感,但在场板的边缘,由于场板与外延层之间的电位差很大,所以在此处存在一个强度很大的电场,击穿容易在较低电压时就提前发生,从而限制了器件耐压值的进一步提高.因此,通常采用在主结与场限环外侧加入场板的复合耐压终端结构来达到提高终端耐压的目的.不同VDMOS器件的制作工艺不同,会导致主结电场分布不同,因此,需要针对不同耐压和工艺的VDMOS设计与之相应的终端结构.文中提出了一种P沟道VDMOS的终端复合结构.该结构由单个带N+偏移区的场限环和两个多级场板共同组成(如图2所示),该结构能有效改善器件主结的电场分布,将主结击穿电压提升至与有源区相当的水平.

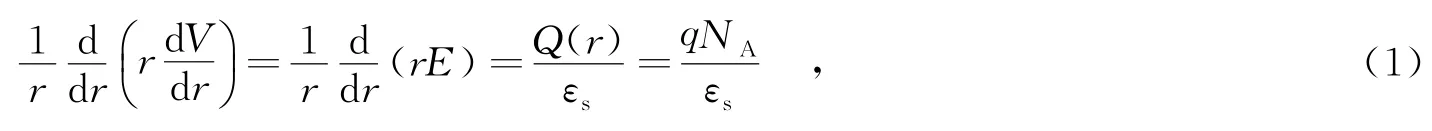

对于文中设计的P沟道VDMOS器件所采用的浅结结构,其主结杂质浓度远高于衬底的杂质浓度,此时,主结击穿是由于载流子在耗尽区反向电压所产生的强电场作用下发生碰撞电离而形成的雪崩击穿.为研究该结构的特性,对于图1中P-漂移区的耗尽区可用泊松方程的圆柱坐标形式进行简单近似,以简化讨论过程[4],即有

其中,NA是P-外延层杂质浓度,εs是硅材料的介电常数,q是电子电量.为方便计算,设主结N电位为0,反偏电压加在P+衬底的漏极上,以耗尽区外边界电场强度为0和结上电势为0作为边界条件,可以求得

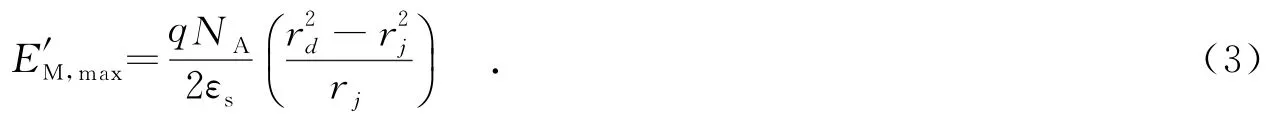

对于主结,当不考虑场限环时,主结的边界峰值电场E′M,max与主结的耗尽区外边界rd之间的关系为

当加入场限环后,场限环与主结的耗尽区部分交叠形成穿通模式,场限环起到分压的作用.此时,反偏电压VR为主结承担电压VM与场限环电压VF之和.场限环右侧边界峰值电场EF,max与场限环耗尽区右边界rF之间的关系为

此时,主结的边界峰值电场EM,max是由反偏电压所产生电场(由式(1)确定)和场限环分担电压在主结边界分别产生的电场之差决定,可表示为

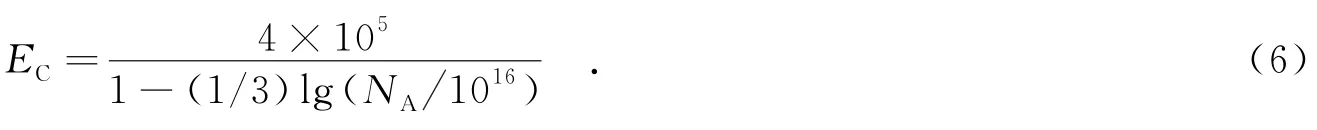

在P沟道VDMOS设计中,由元胞结构可确定rj和NA,反偏电压VR为设计要求击穿电压VDS-B.要使场限环充分发挥分压作用,就要让击穿同时发生在主结和场限环右侧处,此时,对应的击穿电压即为终端结构能承受的最大击穿电压[5-8].为此引入临界电场EC的概念:当PN结的最大电场达到EC值时发生击穿[2].对于文中浅平面结使用突变近似的平面结模型,EC可表示为[9]

在氧化工艺中氧化层内部引入的负电荷使得P沟道VDMOS的耐压易受到表面电荷的影响.为此利用场氧化层与多晶硅作为掩膜,在场限环靠近主结一侧注入磷,形成一个N+偏移区[10-11],该步工艺可与N阱区同时注入,不需要增加任何额外步骤,工艺兼容性好.在增加N+偏移区后,可有效抑制氧化层内部的负电荷在界面处产生的空穴积累层所导致的电场尖峰.

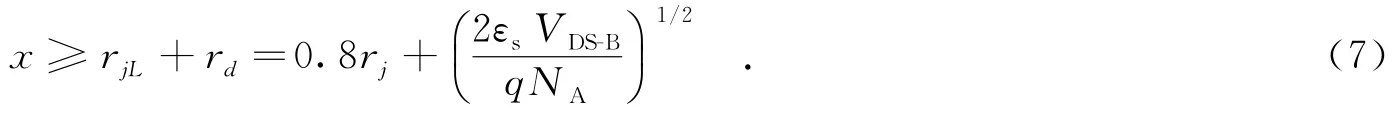

对主结和场限环边缘电场分布的影响,需要在主结与场限环的右侧氧化层上加入场板.当器件处于关断状态时,主结处于反偏,主结上方与源相连接的场板在主结右侧形成空穴耗尽区,将场板下方的表面负电荷完全抵消掉,使其不再影响到耗尽区的电场分布.场限环右侧的浮空场板也有类似作用[2].因此,主结右侧场板的长度x应大于或等于横向结深rjL与未加入场限环前主结击穿时的耗尽层宽度rd之和,即

实际上结终端区耐压能力与介质厚度也有关系,单场板下方的表面电场分布并不均匀,在场板两端会出现尖峰,尤其是场板末端的尖峰对击穿电压的影响很大.理想的场板应该是由主结向外介质层逐渐变厚的斜场板,但考虑到工艺上理想的斜场板极难实现,因此,可用多级场板进行简单的近似来替代[12-13].文中设计采用了两级场板,第1级在场氧化层上利用多晶硅跟多晶硅栅一起制作,经过Si3N4隔离并刻蚀出通孔之后,再与源极金属化一起制作第2级场板,具有优良的工艺兼容性.

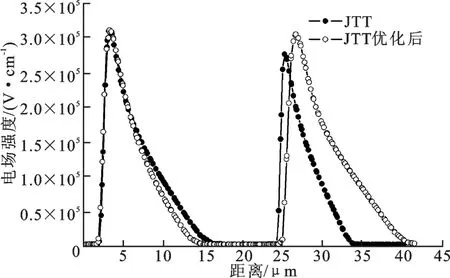

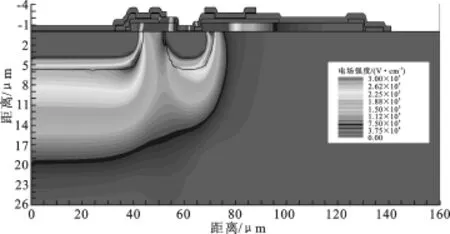

文中所研究的P沟道VDMOS器件要求击穿电压VDS-B为-80 V,电流为14 A.因此,可得到[14-17]外延层厚度为15μm,掺杂浓度为2.5×1015cm-3,N+主结与场限环结深为5.7μm,注入剂量为1×1015cm-2.据此利用Silvaco软件中的工艺仿真模块ATHENA得到图2所示结构,再利用Silvaco中的ATLAS模块对终端结构进行仿真,分析其击穿特性以便做出进一步的优化.文中所采用的结终端技术(Junction Termination Technique,JTT)未优化前的击穿电场强度分布如图3中JTT曲线所示,此时环间距与场板长度亦由前述方法求得.事实上,由于扩散工艺在垂直方向上的速度略大于水平方向,使得主结的外形更接近椭圆柱面,N+偏移区和多级场板的加入,使得整个终端结构的电场强度最强处位于该椭圆柱面的曲率最大处(如图1所示A区域),即靠近主结底部的位置,而并非传统认为处于场氧化层的Si-SiO2界面下方.主结右侧的场板对电场的调制作用,减弱了主结靠近场氧化层附近的电场强度,进一步增加了A区域的电场强度,使得按文献[6]所得环间距的主结处最大电场强度大于场限环处的最大电场,说明此时环间距偏小,主结分担电压过高,将先于场限环发生击穿.

图3 几种终端结构的最大电场强度比较

图4 优化后的该结终端结构击穿前的电场分布

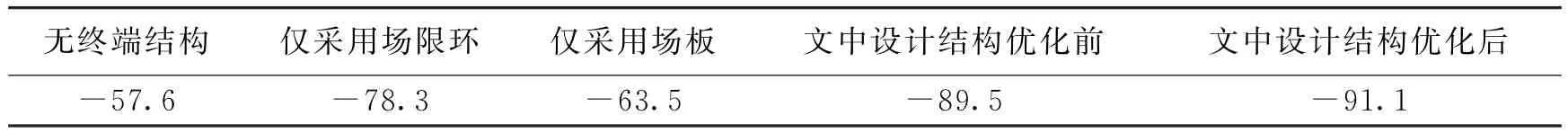

考虑到终端结构最佳的情况是主结与场限环同时击穿,因此需将主结与场限环之间的环间距进行一定的增加,来提高场限环分担电压.通过仿真优化并考虑实际工艺的光刻精度,得到基本满足要求的环间距lopt=15μm.优化后的终端结构击穿时的最大电场强度分布如图3中Opt JTT曲线所示,可见主结右侧最大电场强度与场限环右侧最大电场强度接近.优化后该终端结构击穿前的电场分布如图4所示.对主结击穿电压的仿真结果见表1.仿真结果表明,主结的耐压值达到了-91 V左右,最终优化的结构相比于单独使用场限环或者场板,分别提高了16.3%和43.3%,并且相比于优化前的结构也有明显提高.

表1 不同终端结构的击穿电压仿真值 V

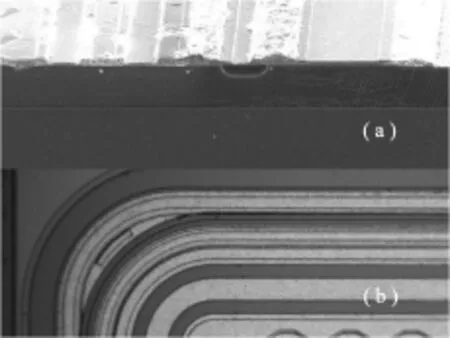

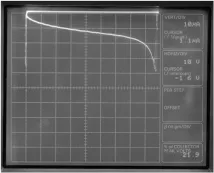

根据以上数据进行流片,得到的P沟道VDMOS样品的终端结构的扫描电镜及显微镜照片如图5所示.使用Tektronix370B晶体管图示仪测试样品的击穿电压达到-90 V(如图6所示),表明设计结果与实验结果一致[14].

图5 样品终端结构形貌

图6 样品实测击穿电压曲线

3 结束语

分析了P沟道VDMOS中场限环和场板复合终端结构的电场分布,并为之设计了一种带N+偏移区场限环和多级场板复合的终端结构.对该结构进行仿真的结果表明,这种结构中主结和场限环的电场会受到场板的影响.因此,通过仿真结果中主结与场限环外侧的击穿电场强度来优化该结构中主结与场限环距离,有效提高了器件的整体击穿电压.最后,流片测试结果表明,文中所设计的这种新型终端结构能有效达到设计目标.

[1]Sze S M,Gibbons G.Effect of Junction Curvature on Breakdown Votage in Semiconductors[J].Solid-state Electronics,1966,9(9):831-845.

[2] 陈星弼.功率MOSFET与高压集成电路[M].南京:东南大学出版社,1990.

[3]Huang H M,Chen X B.New Expressions for Non-punch-through and Punch-through Abrupt Parallel-plane Junctions Based on Chynoweth Law[J].Journal of Semiconductors,2013,34(7):63-67.

[4]Baliga B J.Fundamentals of Power Semiconductor Devices[M].New York:Springer-Verlag,2008.

[5]He J,Zhang X.A Semi-theoretical Relationship between the Breakdown Voltage of Field Plate Edge and Field Design in Planar P-N Junction Terminated with Finite Field Plate[J].Microelectronics Journal,2001,32(9):763-767.

[6]He J,Huang R,Zhang X,et al.Analytical Model of Threedimensional Effect on Voltage and Edge Peak Field Distributions and Optimal Space for Planar Junction with a Single Field Limiting Ring[J].Solid-state Electronics,2001,45(1):79-85.

[7]Tam W S,Siu S L,Wong O Y,et al.Modeling of Terminal Ring Structures for High-voltage Power MOSFETs[J]. Microelectronics Reliability,2012,52(8):1645-1650.

[8]Baradai N E,Sanfilippo C,Carta R,et al.An Improved Methodology for the CAD Optimization of Multiple Floating Field Limiting Ring Terminations[J].IEEE Transactions on Electron Devices,2011,58(1):266-270.

[9]Sze S M,Kwok K N.Physics of Semiconductor Devices[M].Third Edition.New Jersey:John Wiley&Sons Incorporated,2007.

[10]Bose S C J V,De Souza M M,Narayanan E M S,et al.Influence of a Shallow P+Offset Region on a Novel Edge Termination Technique Using Lightly Doped P-Rings[C]//Proceedings of the International Semiconductor Conference: 1.Piscataway:IEEE,1999:63-66.

[11]De Souza M M,Bose S C J V,Narayanan E M S,et al.A Novel Area Efficient Floating Limiting Ring Edge Termination Technique[J].Solid-state Electronics,2000,44(8):1381-1386.

[12]Tihanyi J.Integrated Power Devices[C]//Technical Digest of International Electron Devices Meeting.New York:IEEE,1982:6-10.

[13]Feiler W,Falck E,Gerlach W.Multistep Field Plates for High-voltage Planar p-n Junctions[J].IEEE Transactions on Electron Devices,1992,39(6):1514-1520.

[14]蒲石,郝跃.一种P沟VDMOS器件的研究与实现[J].西安电子科技大学学报,2013,40(6):58-61. Pu Shi,Hao Yue.The Development and Realization of P-channel VDMOS[J].Journal of Xidian University,2013,40 (6):58-61.

[15]Meng Q G,Li B Simulation and Analysis on Transient Performance of VDMOS[C]//Proceedings of 2nd International Conference on Measurement,Information and Control.Washington:IEEE Computer Society,2013:1307-1310.

[16]Zheng S G,Zhang J,Zeng X H,et al.Design and Progress Simulation on High Voltage VDMOS[C]//Advances in Intelligent and Soft Computing.Heidelberg:Springer Verlag,2011:155-163.

[17]Jiang W.Statical Simulation and Analysis on 650V VDMOS Tubes[C]//Proceedings of 2nd International Conference on Measurement,Information and Control.Washington:IEEE Computer Society,2013:1311-1314.

(编辑:齐淑娟)

Novel combined edge termination for P-channel VDMOS

PU Shi,DU Lin,ZHANG Dexi

(Ministry of Education Key Lab.of Wide Band-Gap Semiconductor Materials and Devices,Xidian Univ.,Xi’an 710071,China)

This paper is focused on the improvement of the breakdown voltage for P-channel Vertical Doublediffuse MOSFET(VDMOS),mainly on the structure that is combined with the field limiting ring and the field plate.Based on their basic theories,this paper presents a novel junction termination for P-channel VDMOS with a structure of an N+offset region field limiting ring and two multistep field plates.Simulation results have proved its effective improvement on the electric field distribution at the edge of the main junction.With these achievements,an-80 V P-channel VDMOS is designed and fabricated using this structure.The test for the breakdown voltage of the manufactured sample devices has been conducted and experimental results turn out to be in good accord with the simulation results,demonstrating the validity of the design.

P-channel vertical double-diffuse MOSFET;edge termination;field limiting ring;N+offset region;multi-step field plate

TN432

A

1001-2400(2015)06-0070-05

10.3969/j.issn.1001-2400.2015.06.013

2014-06-17

时间:2015-03-13

国家重大科技专项资助项目(2008ZX01002-002);国家自然科学基金资助项目(61106106);中央高校基本科研业务费专项资金资助项目(K50511250008,K5051325002)

蒲 石(1981-),男,西安电子科技大学博士研究生,E-mail:victor.pu1981@gmail.com.

http://www.cnki.net/kcms/detail/61.1076.TN.20150313.1719.013.html