CPCIe X1适配卡的关键技术

2015-12-20刘亚斌

秦 涛,周 强,刘亚斌

(北京航空航天大学 自动化科学与电气工程学院,北京100191)

0 引 言

PCI Express(PCIe)总线是继传统PCI总线后新兴的第三代I/O 总线标准,其单个收发通道的传输速率可高达2.5Gbps,未来可达到5.0Gbps。PCI Express总线的突出特点是以协议替代了传统的同步或异步时序逻辑总线接口,具有传输速率高、节省硬件资源、无串扰、无码间干扰、无信号偏移、无直流偏置等突出特点[1]。

CompactPCI Express(CPCIe)继承和保留了Compact-PCI的传统技术优势,采用了高可靠欧卡结构,改善了散热,提高了抗振动和耐冲击能力。同时,CPCIe兼容PCI Express总线的全部接口协议,采用2mm 密度的高速针孔连接器替代PCI Express中的金手指式互连方式,进一步提高了可靠性[2],保持了高速差分信号完整性。

由于CPCIe采用了欧洲卡的结构规范,致使CPCIe功能卡在机箱中的布置非常紧凑,几乎无法方便地进行相关的测试、调试和开发工作。同时,CPCIe相关的控制器和机箱比较昂贵,构建一套CPCIe平台的成本高。

因此,非常有必要在PCIe环境下为各种CPCIe功能卡提供一个既符合接口协议、成本低廉,又便于测试、调试和开发的适配卡。

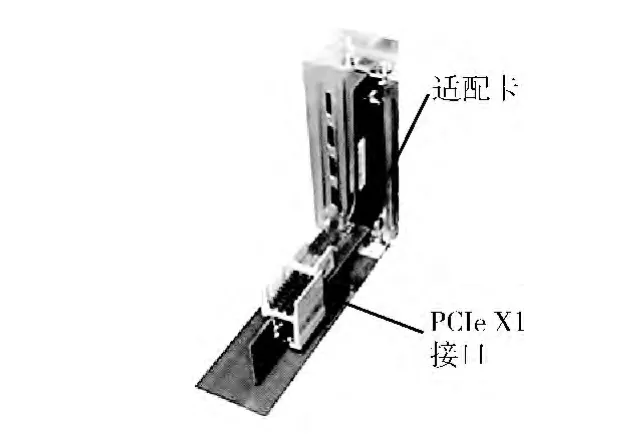

1 适配卡设计

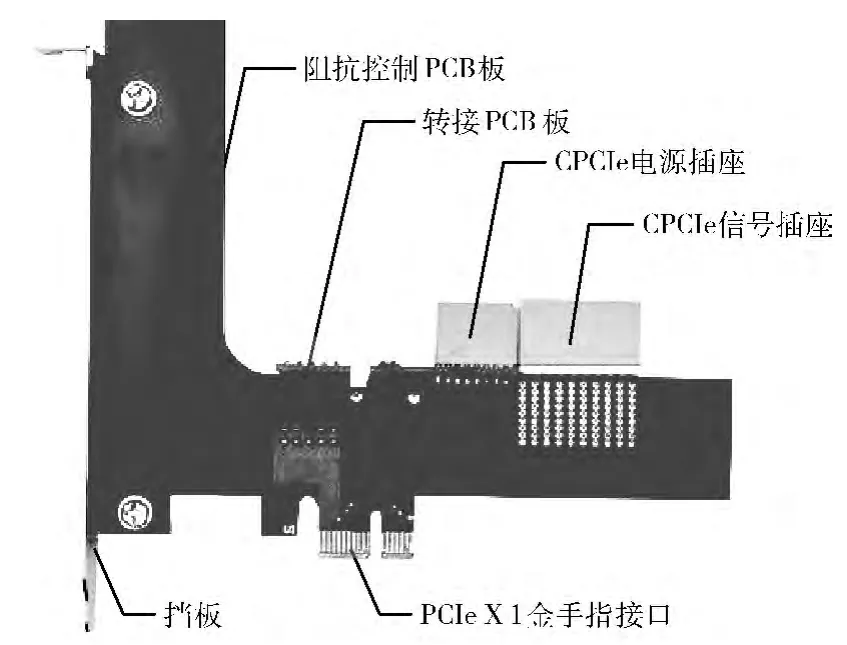

CPCIe X1适配卡结构如图1所示。利用该适配卡可以实现在工控机或台式机的PCI Express X1、X4、X8、X16总线扩展槽中对CPCIe X1 各种功能卡的测试、调试和开发。从而为CPCIe功能卡提供了一个既符合PCIe协议、成本低廉,又便于测试、调试和开发的环境。

图1 CPCIe X1至PCIe X1适配卡结构

该适配卡主要由以下6 部分组成:阻抗控制PCB 板、转接PCB板、CPCIe电源插座、CPCIe信号插座、PCIe X1金手指接口和挡板。CPCIe电源插座是一个弯针插座,实际上就相当于CPCI Express标准中的XJ4插座,而CPCIe信号插座是一个直针插座,实际上就相当于CPCIe标准中的XJ3插座。

阻抗控制PCB板设计成L 形,下部不只有PCIe X1金手指接口,左侧可以安装挡板,便于固定。阻抗控制PCB板L 形缺口位置恰好预留出空间可以插入CPCIe转接板,同时也有效缩短了转接过程中信号线的物理长度,降低了信号衰减。阻抗控制PCB 板其余尺寸规格均符合PCIe接口卡标准要求。

适配卡结构中设计有转接PCB 板,其主要原因是通用的CPCIe电源插座只有直针形式,尚无弯针形式。因此,只能采用一个转接PCB板将直针CPCIe电源插座和L 形的阻抗控制PCB板进行电气和机械连接。

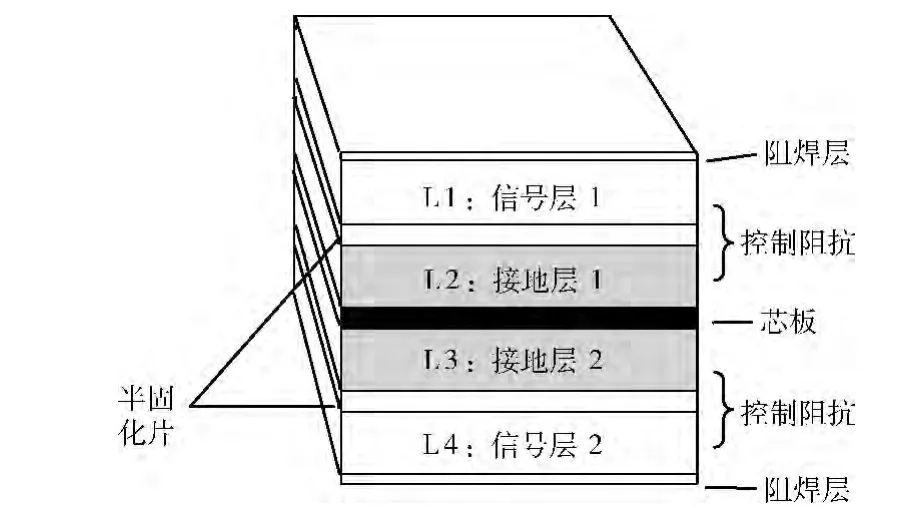

PCIe X1金手指接口位于阻抗控制PCB板的下部边缘,用于与PCIe X1插槽进行物理连接,传递信号和电源。CPCIe信号插座位于阻抗控制PCB板的上部边缘,采用2mm密度的高速针孔连接器,用于与CPCIe X1 中的XP3 信号插头进行物理连接,传递信号。CPCIe电源插座安装在转接PCB板上,用于与CPCIe X1中的XP4电源插头进行物理连接,传递电源。阻抗控制PCB 板是一个典型的4层阻抗控制电路板,用以高速、低损耗、短距离地传输PCI Express X1金手指接口中的低摆幅差分信号 (典型的如LVDS信号)至CPCIe信号插座。阻抗控制PCB板叠层设计如图2所示。

由于PCIe总线采用了高速低摆幅差分信号,理论传输速率高达2.5 Gb/s。因此,为了实现适配卡不影响PCIe X1至CPCIe X1中高速差分信号的传输质量,保证其信号完整性,需要在设计之前对适配卡电气特性提出相应要求,在PCB布局布线设计后通过HyperLynx BoardSim 仿真对特性阻抗控制电路板进行信号完整性分析,PCB 板加工生产后对关键信号线的特性阻抗进行测量,最后再通过大量在线测试实验验证该设计是否可行。

图2 阻抗控制PCB板叠层设计

2 电气特性研究

PCIe X1总线采用了双通道串行传输模式,每通道由两对LVDS差分线对构成,分别为发送TX 和接收RX,单向的数据传输速率可达2.5Gb/s。PCIe电气规范定义了发送器和接收器驱动特性,主要包括时钟、阻抗和终结、DC共模电压、ESD 保护、短路支持、差动峰值电压、差动峰值到峰值电压、AC耦合、相位偏移等特性。从信号完整性的角度看,最为关键的是收发差分链路的特性阻抗和线路损耗。

2.1 特性阻抗

对于适配卡相关的高速差分信号,若不能做好阻抗匹配设计,必定会引起传输线上信号的反射。要做到抑制反射干扰,要求在设计PCB时综合考虑布局和布线,对于线型、线长、线宽、线距需要做精细的设计。尽可能做到始端、负 载 阻 抗 和 终 端 的 阻 抗 匹 配[3-5]。

CPCIe规范要求高速差分信号线的差分特性阻抗为100 Ω±10Ω,信号线对参考地的单端特性阻抗为50Ω±10Ω。信号线的特性阻抗与PCB 板材、板层结构、线宽、线距等密切相关。适配卡设计中选用了常用的FR-4材料,以求降低成本。由于PCB板采用了4层叠层结构,只有顶层和底层用于布线,中间两层为接地层,因此高速差分信号线均采用了微带线 (micro strip line)。微带线特性阻抗计算公式如下

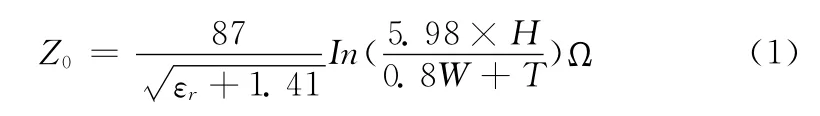

式 中:Z0——传 输 线 为 阻 抗,εr——材 料 的 介 电 常 数,H——参考层间距,W——走线宽度,T——走线高度。

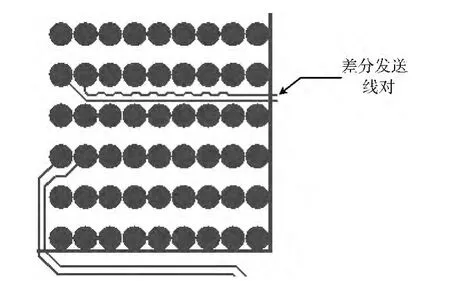

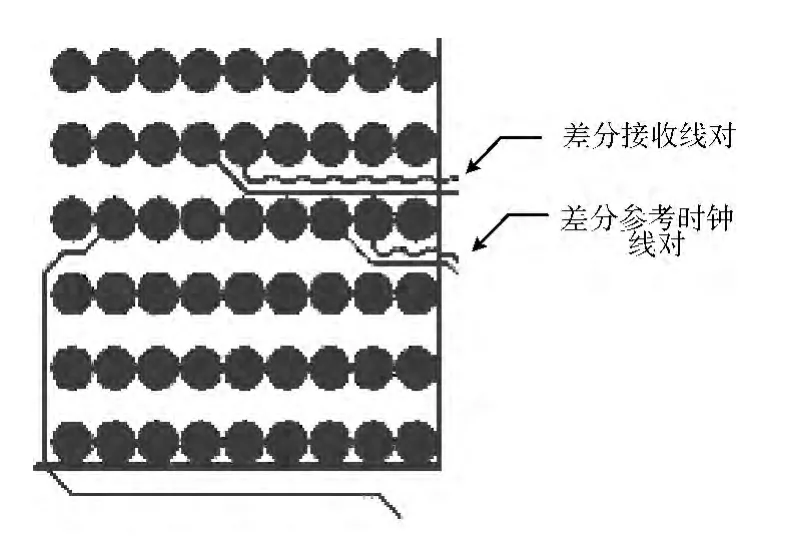

为了能够使阻抗控制PCB 板满足特性阻抗要求,PCB布线设计中差分信号线线宽设计成5mil,差分信号线对中的两条信号线的之间的间距设计为7mil,不同的差分信号线对之间的距离设计成至少大于20mil[6]。同时,设计中采用了蛇形走线方式实现差分信号线对的完全对称 (等长),典型蛇形走线方式如图3、图4所示。通过特性阻抗仿真计算软件SI9000计算,可得到差分信号线的差分阻抗为101.8 Ω,单端阻抗为51.78Ω,可以满足特性阻抗设计要求。

图3 顶层差分信号线对蛇形走线设计

图4 底层差分信号线对蛇形走线设计

2.2 线路损耗控制

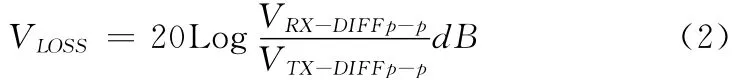

CPCIe X1总线规范要求由发送器所驱动的差动峰值到峰值电压VTX-DIFFp-p在800mV (最低)到1200mV (最高)之间;而接收器通过使用差动接收器放大器来检测差分链路上的电压差值,接收器可检测的差动峰值到峰值电压VRX-DIFFp-p在175mV (最低)到1200mV (最高)之间。

CPCIe X1总线链路的线路损耗可由发送器驱动电压和接收器接收电压确定。发送器驱动一个最低的800 mV 差动峰值到峰值电压VTX-DIFFp-p,接收器的灵敏度被设计成最低可检测175mV 的差动峰值到峰值电压VRX-DIFFp-p,则允许的损耗VLOSS可用下式进行计算

也就是允许的最大损耗为-13.2dB。

为了尽可能的降低线路损耗,CPCIe信号插座设计选用了ERNI 公司的专用2 mm 高速差分插座 (型号:204781)。该型号插座有30 个差分信号对,允许最高传输速率可达3.0Gb/s。而且其插入损耗小于1dB,差分信号接插件差分特性阻抗为100Ω。

同时,最为有效的降低线路损耗的方法是尽量减少适配卡中接收、发送高速差分线的布线长度。阻抗控制PCB板中,PCI Express X1 金手指接口的位置由PCIe规范限定,因此CPCIe信号插座的设计位置直接影响到接收、发送高速差分线的布线长度[7]。一方面,CPCIe信号插座应尽量靠近PCIe X1金手指接口,也要保证阻抗控制PCB板具有一定的机械强度;另一方面,CPCIe电源插座和转接PCB板也都制约了CPCIe信号插座的位置。设计中给出的CPCIe信号插座的位置,综合考虑了上述因素,PCB 布线中也尽量缩短高速差分线的长度。经实际测量,发送差分线长度约为2.44Inch (62.0 mm),接收差分线长度约为2.22Inch (56.4mm)。

3 仿真分析

仿真分析是对适配卡设计进行验证的有效手段之一,可以消除设计隐患,提高设计成功率。设计中选用Hyper-Lynx软件作为适配卡高速PCB仿真工具[8-10]。

3.1 仿真模型与流程

仿真分析参考选用了XIO2001的IBIS模型作为仿真模型,XIO2001是一种单功能PCI Express X1至PCI的桥芯片,其中PCI Express X1 接 口 完 全 符 合PCI Express基 本规范修订版2.0。

BoardSim 用于布线后快速地分析设计中的信号完整性问题,利用HyperLynx进行PCB板高速信号仿真的一般流程为:

(1)将*.HYP 文 件 调 入HyperLynx 创 建 工 作 文 件*.HYP;

(2)检查调入PCB文件的叠层信息,如有必要可进行修改;

(3)选择需要的高速信号进行仿真;

(4)选择该信号的IBIS模型;

(5)将仿真示波器的探头连接到信号线上,打开仿真示波器,开始对该信号进行仿真。

3.2 损耗仿真

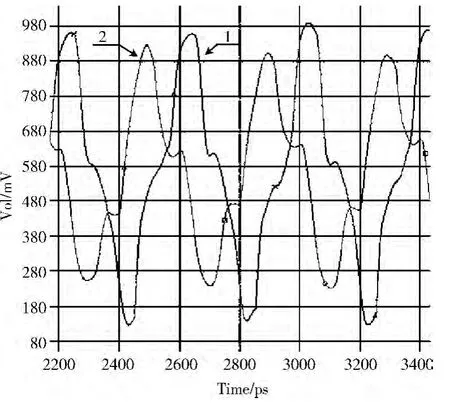

通过以上仿真步骤,将XIO2001中PCI Express X1的IBIS模型加载到适配卡阻抗控制PCB 板的差分信号对上,发送端和接收端信号仿真结果如图5所示。

图5 发送端和接收端信号波形

图5中线1为发送端信号波形,线2为接收端信号波形。通过观察示波器可知发送器差动峰值到峰值电压VTX-DIFFp-p=830mV,接收器差动峰值到峰值电压VRX-DIFFp-p=660mV,衰减损耗为-1.99dB,即链路具有1.99dB的损耗,满足设计要求。

4 测试验证

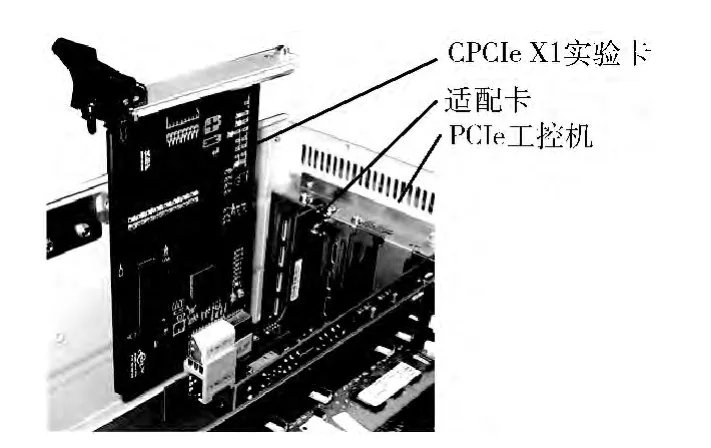

在测试验证中,选用了具有CPCIe X1接口功能的实验卡,该实验卡采用Altera Cyclone IV 系列IP硬核实现PCIe X1总线接口功能。测试中先将适配卡插入工控机的PCIe X1接口中固定牢固 (如图6所示),而后将CPCIe X1接口的实验卡再插入适配卡中。也就是通过适配卡将具有CPCIe X1接口的实验卡转换为PCIe X1接口后插入具有PCI Express X1接口的工控机中进行实验。具体实验配置如图7所示。

图6 适配卡插入PCIe X1接口

图7 CPCIe X1实验卡和转接卡的连接

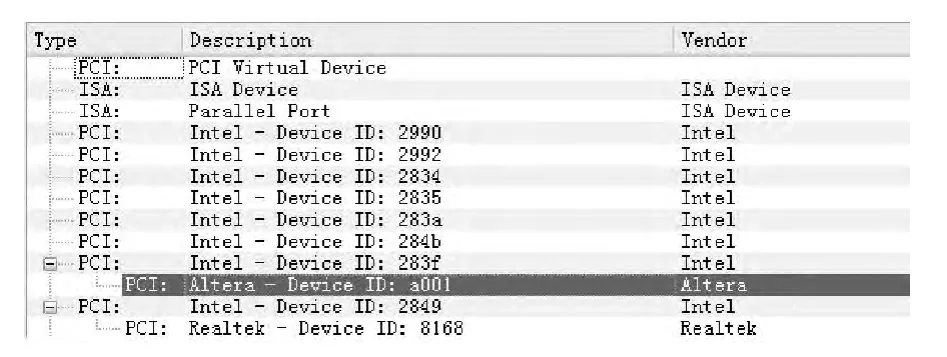

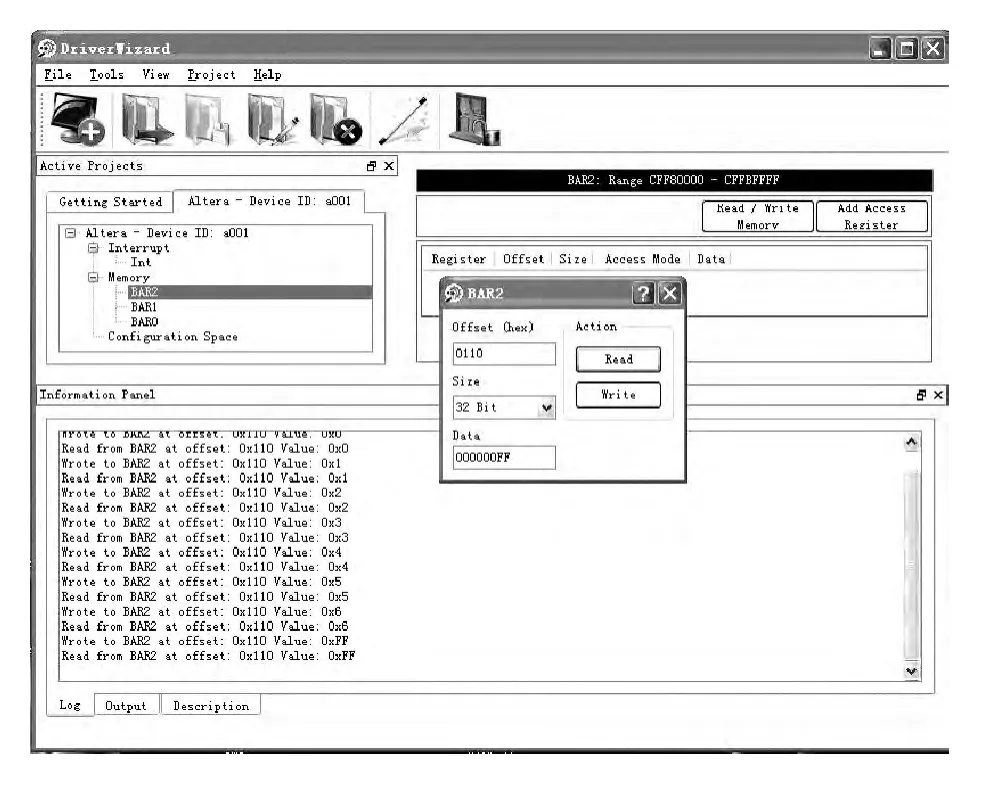

将CPCIe X1实验卡、适配卡和工控机连接好后,工控机启动后能够正常发现设备 (CPCIe X1 接口卡),如图8所示;上位机能够通过WinDriver对设备进行正常的读写寄存器以及数据发送和接收,如图9所示。

测试验证结果表明,设计的CPCIe X1至PCIe X1适配卡能够实现在PCI Express X1插槽中对CPCI/PXI Express X1实验卡的测试、调试和开发。

5 结束语

图8 CPCIe X1接口卡设备信息

图9 CPCIe X1数据发送和接收

本文设计、实现了一种CPCI Express X1 适配卡,通过HyperLynx BoardSim 进行了信号完整性分析和实际测试实验验证。仿真分析和实验结果均表明该适配卡具有以下特点:在不影响PCI Express X1和CPCIe X1信号的质量和功效的前提下,拓展了现有PCI Express X1插槽的应用范围,使其可以兼容CPCIe X1功能卡 (扩展卡),大幅度降低CPCIe X1功能卡 (扩展卡)开发、测试、调试的难度和成本,结构简单、使用非常方便,为CPCIe X1接口卡提供了一个既符合接口协议、成本低廉,又便于测试、调试和开发的环境。

[1]WANG Qi.Introduction to PCI express architecture [M].Beijing:Machinery Industry Press,2010 (in Chinese). [王齐.PCI Express体系结构导读 [M].北京:机械工业出版社,2010.]

[2]CHEN Lijie,ZHOU Weichao,GUO Shuai.High-speed data switch center design based on CPCIE [J].Optoelectronic Engineering,2011,38 (7):136-140 (in Chinese). [陈利杰,周维超,郭帅.基于CPCIE的高速数据交换中心的设计 [J].光电工程,2011,38 (7):136-140.]

[3]HU Jun,LI Jinwen,CAO Yuesheng.Gbps serial link signal integrity analysis and design [J].Computer Engineering and Science,2009,31 (7):102-105 (in Chinese).[胡军,李晋文,曹跃胜.Gbps串行链路信号完整性分析与设计 [J].计算机工程与科学,2009,31 (7):102-105.]

[4]Douglas Brooks.Signal integrity and PCB design [M].Beijing:Publishing House of Electronics Industry,2012 (in Chinese). [Douglas Brooks.信号完整性与PCB 设计 [M].北京:电子工业出版社,2012.]

[5]YAN Zhaowen.Signal integrity simulation analysis[M].Beijing:China Water Power Press,2011 (in Chinese).[阎照文.信号完整性仿真分析方法 [M].北京:中国水利水电出版社,2011.]

[6]Howard Johnson,Martin Graham.High speed digital design[M].Beijing:Publishing House of Electronics Industry,2010(in Chinese).[Howard Johnson,Martin Graham.高速数字设计 [M].北京:电子工业出版社,2010.]

[7]LI Muguo,HUANG Ying,LIU Yuzhi.PCIe bus speed data acquisition card design and implementation [J].Measurement and Control Technology,2013,32 (7):19-22 (in Chinese).[李木国,黄影,刘于之.基于PCIe总线的高速数据采集卡设计与实现 [J].测控技术,2013,32 (7):19-22.]

[8] ZHOU Runjing,JING Xiaosong, REN Guanzhong.PADS2007high-speed circuit board design and simulation [M].Beijing:Publishing House of Electronics Industry,2009 (in Chinese).[周润景,景晓松,任冠中.PADS2007 高速电路板设计与仿真 [M].北京:电子工业出版社,2009.]

[9]LI Keli.FPGA system HyperLynx signal integrity simulation analysis[J].Modern Electronics Technique,2011,34 (8):144-150 (in Chinese). [历 科 立.基 于HyperLynx 的FPGA系统信号完整性仿真分析 [J].现代电子技术,2011,34(8):144-150.]

[10]LIANG Xiaolin.Based on the PCB HyperLynx signal crosstalk analysis and simulation [J].Journal of Hechi University,2007,27 (2):34-37 (in Chinese). [梁晓琳.基于HyperLynx的PCB电路信号串扰分析与仿真 [J].河池学院学报,2007,27 (2):34-37.]