基于EDK的高速数据收发嵌入式用户IP核设计

2015-12-20范晓星席鹏飞

范晓星,席鹏飞,孟 琪

(西安电子科技大学电子信息攻防对抗与仿真技术教育部重点实验室,陕西西安 710071)

随着可编程逻辑器件的进步和发展,FPGA在嵌入式系统中发挥着重要作用。因此,众多FPGA厂商将专用的嵌入式处理器PowerPC、ARM等嵌入到FPGA芯片中。其集成了嵌入式处理器的FPGA芯片被定义为FPGA平台。这种基于FPGA嵌入式平台提供了一个灵活的解决方案,在该方案中,一个单FPGA芯片上提供了大量不同的IP软核和硬核资源,这些固件和硬件可随时升级。这种可编程的结构特点,大幅缩短了系统的开发时间,而同一平台能应用在多个领域,提高了平台的资源复用率[1]。

针对平台 FPGA设计,Xilinx公司推出了 EDK(Embedded Development Kit),专门用于FPGA内部嵌入式处理器、软硬件协同设计工具,包含了大量与PowerPC设计相关的IP核,使用EDK进行设计可以大幅简化设计步骤并缩短开发周期,但在EDK中的IP核并不能满足设计人员在设计中的使用。而Xilinx公司的另一硬件开发工具ISE(Integrated Software Environment)中具有众多EDK中没有的IP资源。因此,本文提供了一种调用ISE中的IP核构建在EDK环境下使用的IP核设计。该设计可完成FPGA与片外的高速串行通信,实现读写内存的功能。

1 IP整体结构

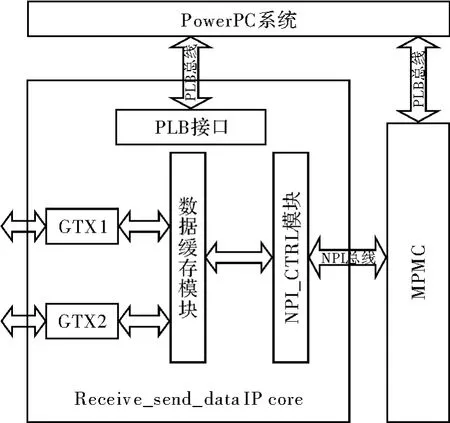

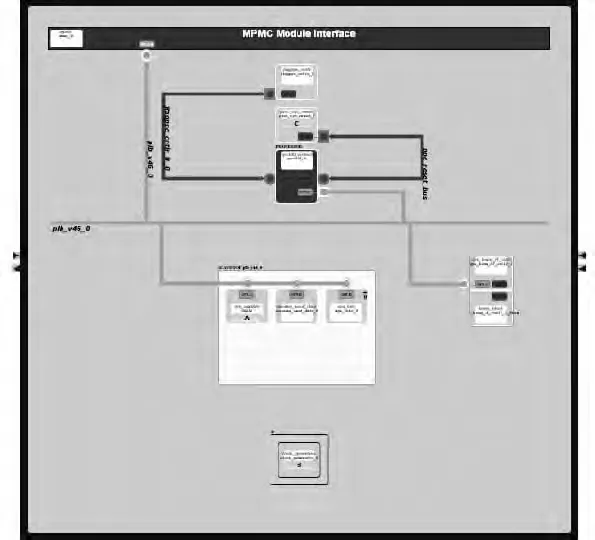

自定义用户IP核总体结构如图1所示。

图1 自定义用户IP结构图

如图1所示,IP核基于Xilinx公司Virtex-5 FX系列的PowerPC硬核嵌入式系统设计。用户IP核通过PLB总线连接在PowerPC系统中;通过两路GTX硬核收发数据,与FPGA外部进行串行通信,数据传输速率可达6.0 Gbit·s-1;数据通过缓存模块和NPI接口写入内存控制器 MPMC,或从 MPMC读出,并通过MPMC实现内存读写。

2 RocketIO GTX硬核

RocketIO GTX是Xilinx公司FPGA中的硬核,是一种具有通用性、易用性、低功耗、低成本的千兆位串行收发器。设计将使用此硬核完成与FPGA外部的高速串行通信功能。

设计采用Virtex-5 FXT系列FPGA,其GTX主要特性如下[2]:(1)高速全双工收发,每个通道支持750 Mbit·s-1~6.5 Gbit·s-1的数据传输速率。(2)内嵌了发送时钟生成和接收时钟恢复模块,减少了外部电路。(3)自同步时钟数据发送方式。(4)5级可调输出差分电压,提高了兼容性。(5)可编程的发射预加重、接收线性均衡器和判决反馈均衡器,提高信号的完整性。(6)支持直流和交流耦合。(7)可编程的片内差分终端50/75Ω电阻,减少了外接终端电阻。(8)支持内部的串行和并行回环测试模式,方便调试。(9)8b/10b编解码,可编程的边界对齐字符(COMMA)检测,方式灵活,支持多种串行通信协议。(10)具有用户动态重配置端口。

根据设计所需,在ISE中按照Xilinx官方GTX核例化向导指导[3]例化GTX核,测试收发数据性能。设计将 GTX 配置为150 MHz专用时钟,3.0 Gbit·s-1串行速率,采用8b/10b编码,内部16 bit数据,K字符选择K28.5。

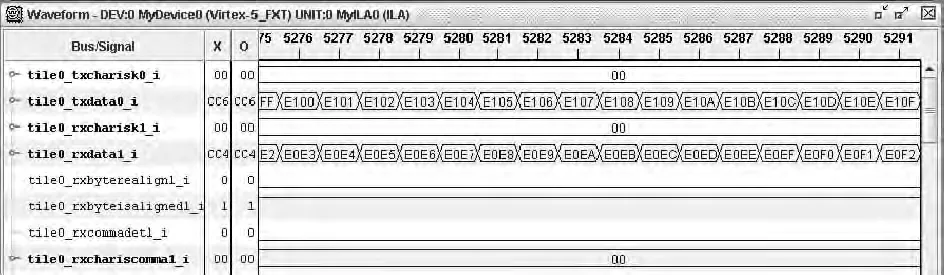

图2给出了使用一对GTX收发数据的时序,图2为用Chipscope抓取的时序图。

图2 GTX数据传输时序图

在Virtex-5 FPGA上例化出两通道一对GTX核tile0,在FPGA外部将tile0_0通道 GTX的发送端与tile0_1通道GTX的接收端相连,组成tile0_0通道发送数据,tile0_1通道接收数据的通信回路。通过发送递增码进行测试,如图2所示,tile0_1通道接收到的数据有30个周期的延时,这是消耗在链路上的时间。信号tile0_txcharisk0_i为“00”,说明 tile0_txdata0_i在链路上发送的是数据;信号tile0_rxcharisk1_i为“00”,说明tile0_rxdata1_i接收到的是数据,而不是控制字符;信号 tile0_rxbyteisaligned1_i为“1”,说明 tile0_rxdata1_i接收到的数据已经对齐[2]。

3 内存控制器MPMC及NPI总线

在接收数据时,将GTX接收端收到的数据通过高速数据总线NPI总线[4]写入内存进行缓存;在发送数据时,先将数据读入内存进行缓存,GTX发送端通过NPI总线从内存中取数据,然后发送出去。Xilinx公司在EDK开发工具里提供了内存控制器软核MPMC,对内存的读写操作通过调用MPMC完成,因此本高速数据收发用户IP需要NPI接口与MPMC进行数据传输。

3.1 MPMC

MPMC(Multi-Port Memory Controlletr)是一个全部支持双数据传输模式(DDR和DDR2)和单数据传输模式(SDRAM)的参数化内存控制器[4]。MPMC有8个相互独立的端口,每个端口都可以独立访问内存,MPMC的仲裁器会按一定的规则仲裁并决定其先后。同时,MPMC的每个端口均带有缓存,所以在写入数据时,数据是先写入缓存,等这个端口取得内存写入权后再从缓存写入内存。数据写入缓存再写入内存的过程对用户不可见。所以对用户的逻辑来说,只要将数据写入MPMC的端口即可。

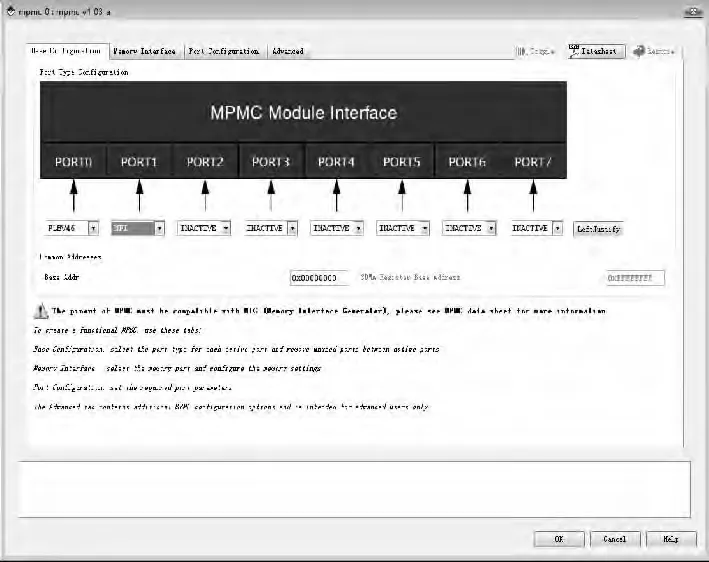

MPMC的每个端口都可配置成可以连接PowerPC处理器、MicroBlaze、CoreConnect和 MPMC NPI结构的个性接口模块(PIMs)。MPMC共提供 PLB、XCL、SDMA和NPI 4种接口。XCL主要在处理器的Cache从内存读取数据时使用;SDMA在外部数据要用DMA方式写入内存时使用,其支持SGDMP;PLB接口主要用于处理器通过PLB总线访问内存;NPI接口是让用户在设计中利用MPMC特性的接口。设计采用控制通道与数据通道分开的方式,不共用总线,提高性能。其中,采用PLB接口与处理器进行控制信息和状态信息的交换,采用NPI接口访问内存。图3为在EDK环境下将MPMC的端口配置出PLB和NPI接口。

图3 MPMC端口配置

3.2 NPI接口控制器

NPI接口有以下特性:(1)提供一个简单的内存接口以适应不同协议。(2)提供地址线、数据线和控制信号来进行内存操作。(3)允许同时通过FIFO进行数据的读/写。(4)可以配置成32位或64位的数据宽度以适应不同的系统需求[4]。

NPI接口控制器(NPI_CTRL)用于实现NPI接口协议,数据宽度为64位,支持 burst工作模式,一次burst读或写最多可以传输256 Byte数据,每次burst后硬件会自动更新地址,得到下一个 burst的起始地址。

发送数据时,NPI接口控制器(NPI_CTRL)根据命令和配置信息从内存中指定的起始地址处读取指定数量的数据到发送数据缓冲区(send_data_fifo),然后由GTX发送到FPGA外;接收数据时,GTX接收到的数据写入接收数据缓冲区(received_data_fifo),然后由NPI接口控制器(NPI_CTRL)根据命令和配置信息将数据写入内存中的指定起始地址处。

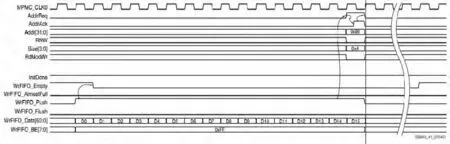

图4和图5分别是MPMC中64位NPI接口128 Byte长度burst读和写时序图[4]。图中,size表示 burst长度,addr表示起始地址。当要进行burst读操作时,先将size设为0x04,addr设为0x80,同时将 addrReq置为有效请求地址仲裁,当AddrAck有效时表示地址请求得到允许,约为25个时钟周期后,RdFIFO_Pop信号会有效表示数据已读出,经过1个、2个或3个时钟周期延迟后,起始地址0x80处的128 Byte数据就会依次出现在RdFIFO_Data端口。当要进行burst写操作时,将WrFIFO_Push置为有效,在WrFIFO_Push有效时写入32 word即128 Byte数据,WrFIFO_BE为0XFF表示每次写入的64位数据均有效,当写到32 word的最后一个时,给出写入的起始地址addr和burst长度size,同时将 addrReq置为有效并请求地址仲裁,当AddrAck有效时表示地址请求得到允许,随机MPMC控制器将WrFIFO的数据写入内存指定起始地址处,当WrFIFO的数据全部写入内存时WrFIFO_empty置为有效。

图5 64位NPI接口burst写

4 数据缓存模块

由于使用的不是单通道GTX,因此数据位宽不匹配。所以无论是从内存中取数据由GTX发出或将GTX接收到的数据写入内存,都需要进行缓存处理。

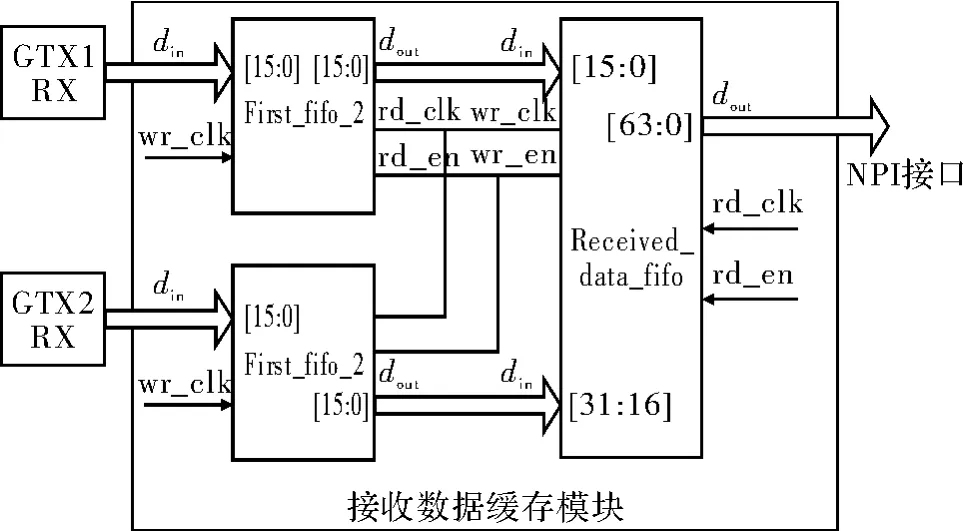

在接收数据时,单一通道GTX的数据位宽为16 bit,采用两通道进行数据传输,所以共32 bit数据。NPI接口采用的数据位宽是64 bit,所以需要进行位宽转换。但接收数据是被动的,因此两路GTX接收到的数据不一定在时间上同步,可能有先后到达的关系,因此利用异步FIFO构建两级缓存[5],解决位宽不匹配和时间不同步问题。具体接收数据缓存程序结构如图6所示。

图6 接收数据缓存模块结构图

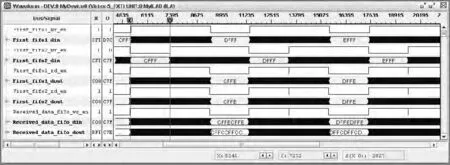

由图6可看到接收数据缓存模块由3个异步FIFO构成。其中First_fifo_1和First_fifo_2为16 bit输入16 bit输出,构成第一级缓存;Received_data_fifo为32 bit输入64 bit输出,为第二级缓存。通过两级缓存,将两路GTX接收到的32 bit不同步数据转为64 bit同步数据,再通过NPI接口写入内存。接收数据缓存模块的工作时序通过Chipscope抓取结果如图7所示。

图7 接收数据缓存模块时序图

图7中,两通道GTX发送的都是递增码,Fitrst_fifo_1写入数据比First_fifo_2写入数据早2 027个时钟周期。Received_data_fifo每次同时从Fitrst_fifo_1和Fitrst_fifo_2中读取固定值数据,并转为64 bit输出。通过一级缓存,成功解决了两路数据不同步的问题。通过二级缓存,数据转为64 bit进入NPI接口控制模块(NPI_CTRL),然后写入MPMC。

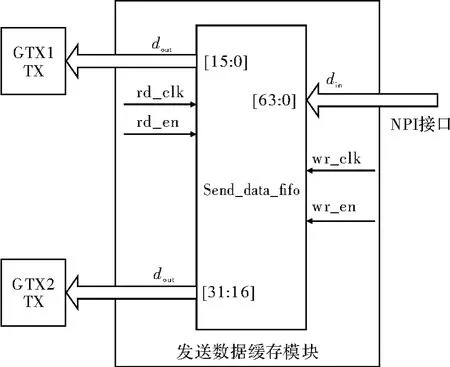

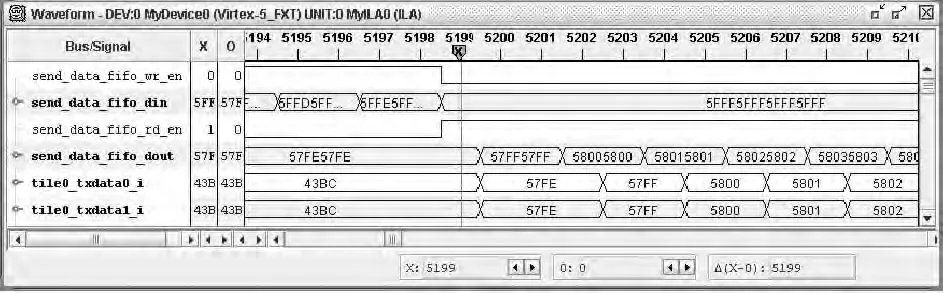

在发送数据时,通过NPI接口从内存中读取的数据为64 bit,两路GTX的数据位宽为32 bit,所以还是需要进行缓存以完成位宽转换。因为发送数据是主动的,所以不存在发送不同步的问题,因此只需利用异步FIFO构建一级缓存即可。具体发送数据缓存程序结构如图8所示。发送数据缓存模块工作时序由Chipscope抓取得到,如图9所示。

图8 发送数据模块结构图

图9 发送数据缓存模块时序图

如图9所示,Send_data_fifo将从NPI接口接收到的64 bit数据转换为32 bit,并传输给两路GTX的发送端 tile0_txdata0_i和 tile0_txdata1_i。

5 嵌入式用户IP核的封装

以上完成的各模块工作都只在ISE环境下完成逻辑开发,还并不能在EDK环境下直接作为嵌入式IP核使用,因此需要进行EDK用户IP核的封装。EDK为设计人员提供了自动化设计向导(Base System Builder,BSB),可以指引工程师快速完成设计过程[1]。通过此向导,建立基于PowerPC的简单嵌入式系统。其System Assembly View图,系统结构图分别如图10和图11所示。

图10 System Assembly View图

图11 系统结构图

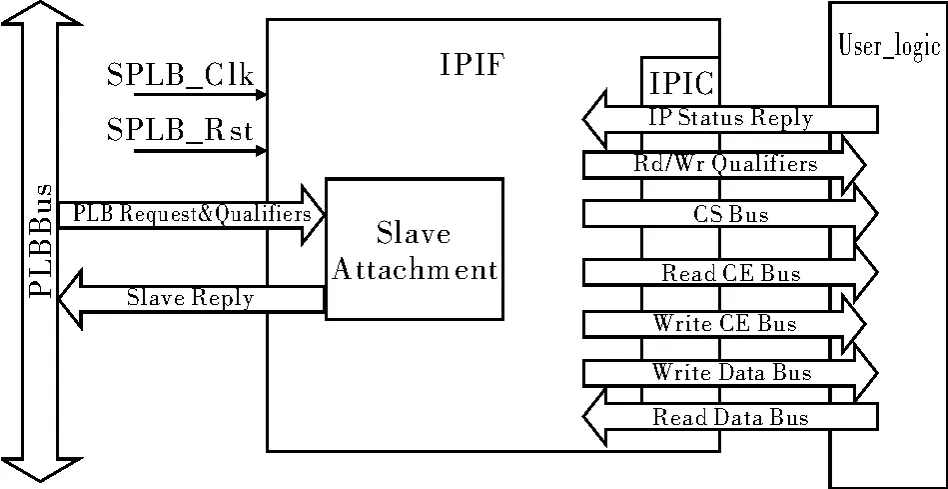

用户IP核通过PLB总线连接在PowerPC处理器上。PLB总线[6]是一种高带宽、低延迟、高性能的处理器总线,用于连接高性能CPU、高速存储器控制器、仲裁器、高速的DMA控制器等高性能、大带宽的片上设备。由于PLB总线协议信号多,较复杂,为使用户更方便地使用、加快开发进度,Xilinx公司为用户开发了添加用户IP核向导CIP(Create and Import Peripheral Wizard),添加用户自定义IP核[7]。该向导自动生成PLB总线与用户逻辑之间的接口,即IPIF(IPInterface)。利用IPIF解决PLB总线接口和用户逻辑接口之间的转换。在用户逻辑看来,PLB接口表现为简单的IPIC(IP Inter Connect)接口。用户使用该向导还可根据需要选择相应的模块和功能[8]。设计中PLB总线只用于传递少量的参数和状态信息,因此,PLB模块配制成了从设备。核心模块SLAVE Attachment提供了PLB从设备的基本功能,它在PLB总线和IPIC之间执行协议和时序的转换,PLB模块的结构如图12所示。

图12 PLBV46_SLAVE_SINGLE结构图

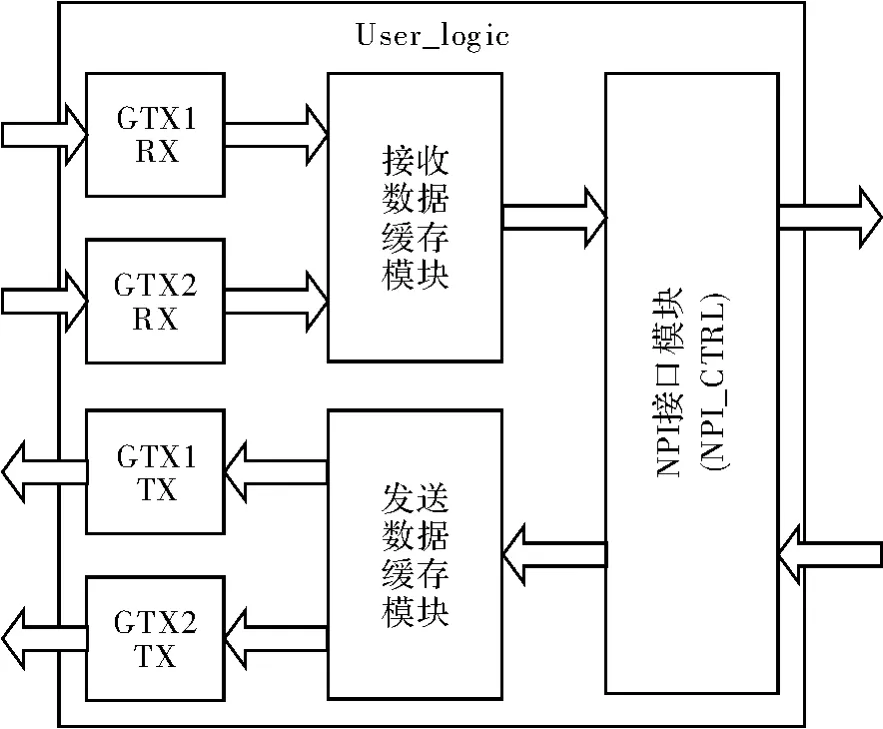

PLB模块中的User_logic为在ISE环境下开发的逻辑,组成如图13所示。将RocketIO模块,数据缓存模块,NPI接口(NPI_CTRL)控制模块做正确连接,用IPIC和IPIF连接起来,成为嵌入式IP核的逻辑。

图13 用户逻辑结构图

使用CIP生成的用户自定义IP核保存在EDK工程目录的pcore文件夹,用户IP核目录如图14所示。

图14 用户IP核目录结构图

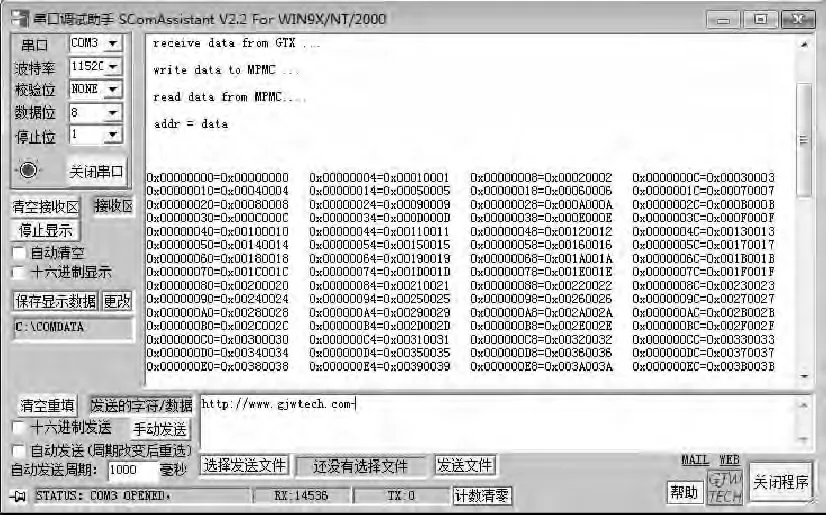

文件夹hdl用于存放用户IP的HDL代码,即.v或.vhd文件。设计使用VHDL语言[9],所以各模块的HDL代码文件都保存在vhdl文件夹下。文件夹netlist用于保存设计所用到的网表文件。本设计使用了ISE工具的IP核,RocketIO、FIFO、icon及 ila,其网表文件都保存在netlist文件夹下。文件夹data用于存放用户IP的配置文件[1]。MPD文件为微处理器外设规范(Microprocessor Peripheral Definition),定义了外设接口。在MPD文件中列出了总线接口端口和默认连接,列出了参数和默认值。PAO文件为外设分析命令文件(Peripheral Analyze Order),包含了hdl文件的列表,是综合和定义分析命令所需的。BBD文件黑盒定义(Black Box Definition)文件,管理被优化的硬件网标的文件位置,用于所设计外设的黑盒部分。运行PowerPC简单系统工程,接收FPGA外部数据,通过串口打印读出写进DDR2中的数据。由图15可以看到,递增码未出现错位与不同步问题,表明所设计达到了要求。

图15 串口打印从DDR2读出数据

6 结束语

介绍了一种用ISE逻辑开发工具中的IP核来构建嵌入式开发平台EDK中,用户自定义IP核的方法,并且本设计完成了高速数据收发通信的功能。此外,设计采用两路GTX,可通过增加GTX通道数,或者配置GTX为更高带宽,以增加系统带宽,具有良好的扩展性。设计在连接PowerPC处理器的系统下完成[10],只要采用PLB总线,此自定义IP可以直接移植到MicroBlaze处理器系统中,具有良好的移植性。

[1]何宾.片上可编程系统原理及应用[M].北京:清华大学出版社,2010.

[2]Xilinx.Virtex-5 FPGA GTX transceiver user guide[M].USA:Xilinx Conpration,2009.

[3]Xilinx.Virtex -5 FPGA RocketIOGTX transceiver wizard v1.5 getting started guide[M].USA:Xilinx Conpration,2008.

[4]Xilinx.Multi- port memory controller(MPMC)(v.4.03.a)[M].USA:Xilinx Conpration,2008.

[5]Xilinx.FIFO generator v4.4 user guide[M].USA:Xilinx Conpration,2008.

[6]Xilinx.PLB usage in Xilinx FPGAs[M].USA:Xilinx Conpration,2005.

[7]叶肇晋,张稀楠,马磊.基与Xilinx FPGA片上嵌入式用户IP核开发[M].西安:西安电子科技大学出版社,2008.

[8]Xilinx.PLBV46 slave single(v1.01a)[M].USA:Xilinx Conpration,2008.

[9]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1998.

[10]赵峰,马迪铭,孙炜,等.FPGA上的嵌入式系统设计实例[M].西安:西安电子科技大学出版社,2008.