基于DSP的频率特性分析仪设计

2015-12-18孙媛媛马泽伟

李 尧,孙媛媛,马泽伟

(西安电子科技大学电子工程学院,陕西西安 710071)

频率特性分析仪可以对被测网络的频率特性进行快速的动态测量,得出被测网络传输特性,并将测量结果以数据或图形的形式实时显示。传统的扫频仪大多结构复杂、体积庞大、价格昂贵且操作复杂。因此,具有低成本、数字化、智能化、高性能的频率特性分析仪的需求日益扩大[1]。一种基于DSP和DDS技术的新型数字合成扫频仪的设计被提出。

系统使用DDS技术设计高精度的扫频信号源,采用模拟检波和鉴相方法,实现幅频测量和相频测量;使用DSP作为数据处理和控制核心,完成测量控制、信号发送、数据采集和实时处理等任务;最后通过TFT LCD和VGA接口实时显示或输出测量结果,完成了一款低成本、高性能的频率特性分析仪设计。

1 频率特性分析仪的系统设计方案

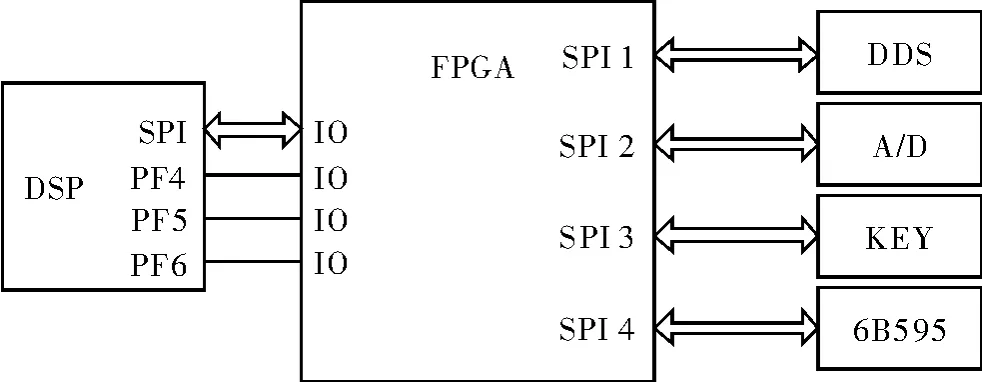

频率特性分析仪主要包括扫频信号源模块、幅度和相位检测模块、数据采集模块、数据处理及控制模块、图像显示与交互接口模块[2],系统总体框图如图1所示。

在系统中扫频信号源采用专用DDS器件实现,可以产生频率连续可变的正弦信号,满足系统的频率带宽及频率步进要求,同时配合外部的Π型衰减网络,实现大动态范围的连续幅度输出。幅度检测电路使用对数放大器实现,检波输出的模拟量由ADC转换为数字量,送入控制及处理电路进行数据处理;相位检测采用专用相位差检测芯片。直接将被测系统输入和输出信号的相位差转换为模拟量,经ADC转换为数字量送入控制和数据处理电路进行数据处理。

数据处理和控制电路由DSP+FPGA组成,主要完成系统主要器件的逻辑控制,数据处理,显示输出和交互接口控制,协调整个系统完成测量。显示输出及交互接口电路主要完成各种命令和数据输入和测量结果显示与输出。可输出的信号频率范围是20 Hz~150 kHz。

2 软件设计

ADI公司的VisualDSP++具有灵活的工程管理体系,为DSP处理器应用程序和项目的开发提供了一整套工具[3]。系统中DSP软件的主要功能是协调和控制系统完成测量功能,并进行数据处理。

图1 系统总体框图

通过中断方式由键盘获得各种设置参数和命令,并据此进行控制扫频信号源与数据采集电路,将采集到的数据进行相应的计算处理后送到液晶和VGA显示,系统正常测试程序流程如图2所示。

DDS控制程序包括AD9958初始化和输出通道控制,输出信号频率幅度相位控制。DDS在上电后首先进行主复位,然后依次写寄存器 CSR和 FR1,设置AD9958输出通道,接口模式为1位串行模式(2线),设置内部锁相环参数使系统时钟为500 MHz。

接描述文件(LDF)定义系统的配置、存储器的分配、链接器的分配,它描述了输入段到输出段及其真实物理地址的映射[4-5]。在系统中由于扩展了SDRAM,将显示数据放在外部存储器SDRAM中,同时将字模和一部分程序放在外部Flash中,因此需要对上述LDF文件进行修改。

由于 ADSP-BF532[6]内部 RAM 有限,系统所有程序不可能全部在内部RAM中执行,因此将按键处理等不常用程序写入Flash中,需要执行时再从Flash中取指令运行,函数定义时与字模相同[7]。

3 FPGA逻辑设计

3.1 SPI收发逻辑

系统中控制板与模拟板之间使用SPI接口进行命令和数据的传送,需要控制的对象包括包括 DDS、AD7655、键盘和6B595,结构框图如图3所示。

图3 SPI接口逻辑关系

DSP发送命令或数据给FPGA,FPGA根据相应PF引脚的状态判断接收对象并进行转发,当需要读取A/D数据时将DSP与AD直连。

通过逻辑分析仪观察Blackfin DSP的SPI接口发现,当设置为8位模式,自动控制片选信号。当最后一个8位数据中的第一个送出时,片选自动复位。在系统中为了使用片选判断DSP是否在收发数据,并能完整接收DSP发送的数据,使用手动方式控制SPI片选信号状态,在发送完数据后延时一段时间片选信号再复位。

3.2 DDS控制逻辑

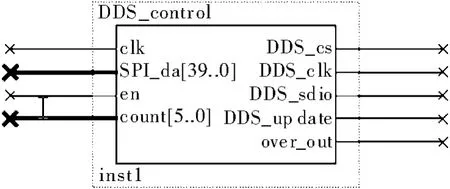

系统中为简化设计和控制,对DDS芯片只写不读,控制信号输出的通道,输出信号频率和幅度、相位,由于不同的寄存器位长不同,DSP在发送数据或命令时多发送1 Byte,表示后续的有效数据长度,DDS控制逻辑根据此参数控制状态机将接下来的数据转发给DDS,最后送出UPDATE信号,使设置生效。图4为DDS控制逻辑框图。

图4 DDS控制逻辑框图

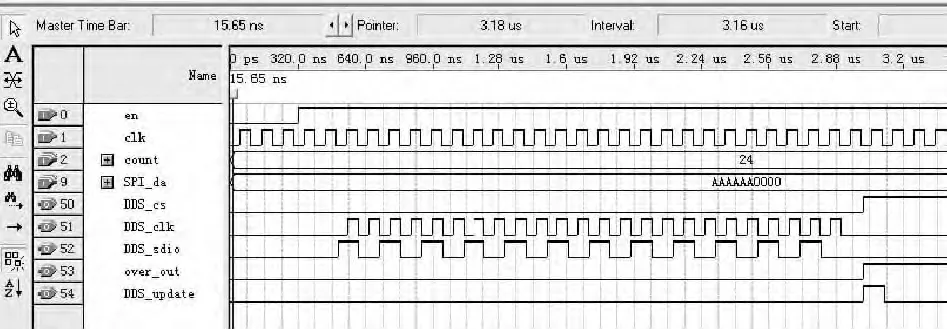

写24位数据时的时序仿真如图5所示。

图5 DDS寄存器操作时序仿真

3.3 继电器控制逻辑

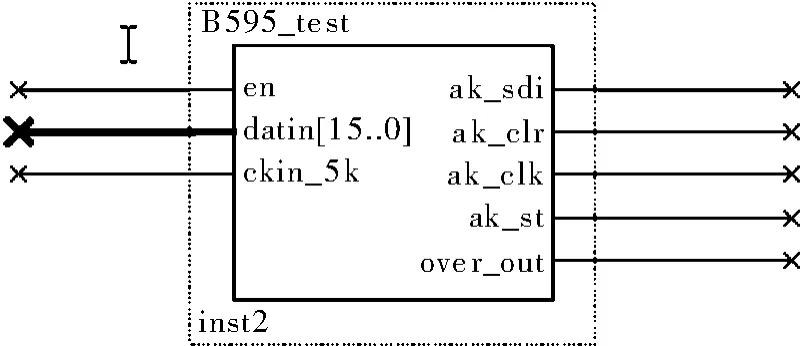

继电器的控制由串并转换芯片TPIC6B595实现,FPGA逻辑将相应的串行控制字送入TPIC6B595芯片,并打开输出使能。TPIC6B595输入时钟不能过高,因此需将主时钟分频后输出,图6为TPIC6B595控制逻辑框图。

图6 TPIC6B595控制逻辑框图

图7 TPIC6B595控制逻辑时序仿真

从波形图可以看出,使能信号每一次高电平,在转换时钟上升沿的控制下并行数据就串行输出一次,转换完成后,时钟信号保持为低电平,同时并行输出信号出现一次上升沿,将数据并行输出从而控制相应的继电器工作;使能信号为低时,数据线和时钟线均维持上一状态,为下一次转换做准备。

4 幅频特性测试

幅频测试时根据设置参数依次修改频率和幅度控制字,延时等待输出稳定后开始A/D采集,处理并将结果送显示,完成一个测试点,依次扫描频带内的每个频率点,完成一次扫频测试。以低通滤波器为例进行测试。

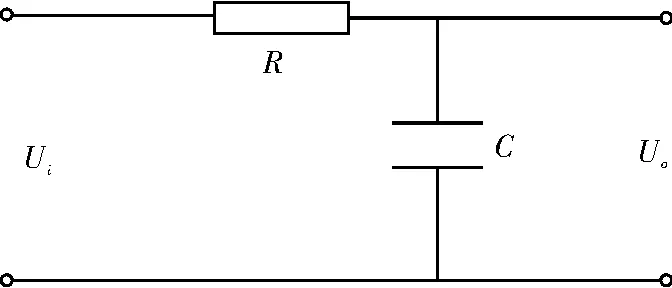

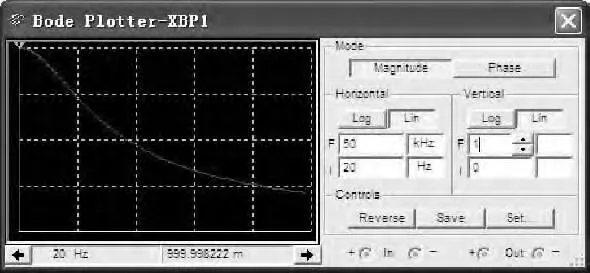

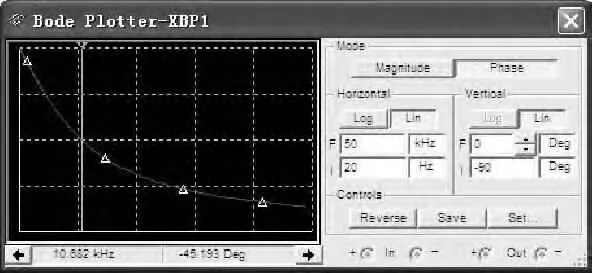

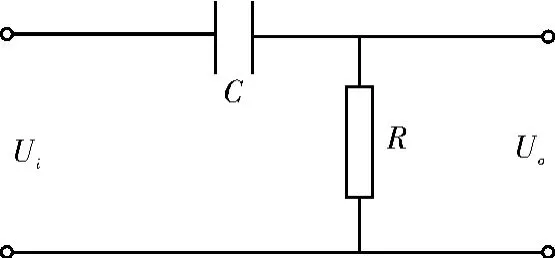

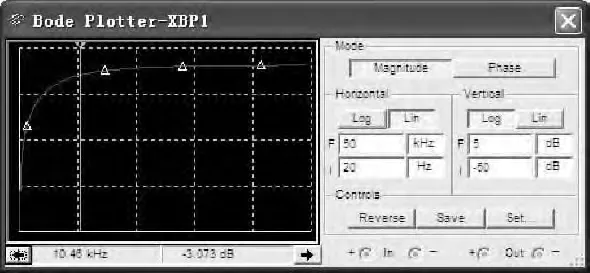

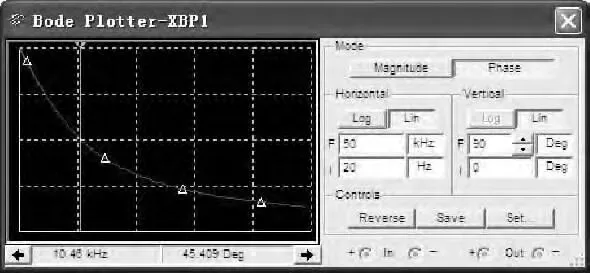

相频测试时同时使能两个通道,并设置通道1相位滞后通道0~90°,频率与幅度设置相同。图8所示为一阶RC低通滤波器,其中R=1.5 kΩ,C=10 nF,使用Multisim进行仿真,理想频率特性幅频特性如图9所示,相频特性如图10所示。

图8 一阶RC低通滤波器

图9 一阶RC低通滤波器幅频特性仿真图

图10 一阶RC低通滤波器相频特性仿真图

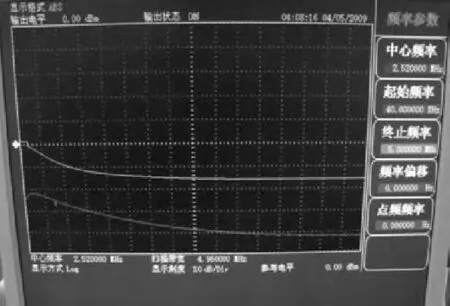

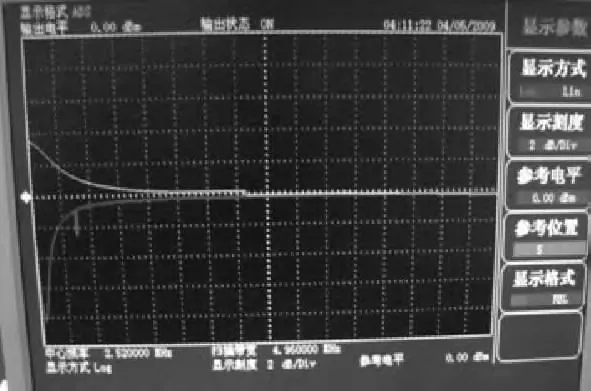

使用频率特性分析仪对一阶RC低通滤波器进行扫描测试,幅频和相频测试结果如图11所示。

图11 仪器测试结果

图12所示为一阶RC高通滤波器,其中R=1.5 kΩ,C=10 nF,使用Multisim进行仿真,理想频率特性幅频特性如图13所示,相频特性如图14所示。

图12 一阶RC高通滤波器

图13 一阶RC高通滤波器幅频特性仿真图

图14 一阶RC高通滤波器相频特性仿真图

使用频率特性分析仪对一阶RC高通滤波器进行扫描测试,幅频和相频测试结果如图15所示。

图15 仪器测试结果

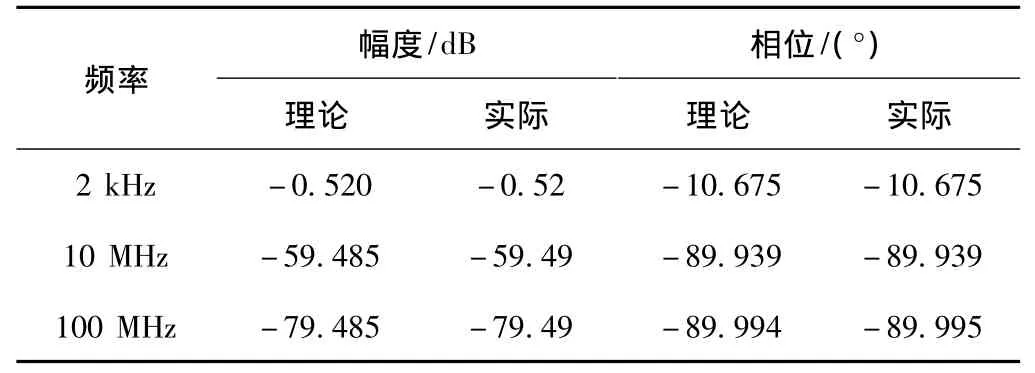

对一阶低通和一阶高通滤波器进行测量,分别取3组不同频率测量数据,如表1和表2所示。

表1 一阶低通滤波器测量

由测试与仿真结果对比可知,仪器可以较准确地测出幅频和相频特性曲线,证明了系统设计的正确性。

5 结束语

在现代频率合成技术的基础上,采用ADI公司的Blanckfin 532作为控制和数据处理核心,实现了对模拟部分的精确控制和系统功能的控制与管理。设计了系统的人机交互接口,实现了幅频和相频测量功能,输出测量结果正确。

[1]王晓元.扫频仪的原理与维修[M].北京:人民邮电出版社,1993.

[2]毛长根.低频扫频仪的设计与制作[J].电子工程师,2002,28(3):37 -40.

[3]Analog Devices Inc.EE -239_running programs from Flash on ADSP - BF533 blackfin processors[M].USA:Analog Devices Inc,2013.

[4]陈峰.Blackfin系列DSP原理与系统设计[M].北京:电子工业出版社,2004.

[5]Analog Devices Inc.EE -68_analog devices JTAG emulation technical reference[M].USA:Analog Devices Inc,2012.

[6]Analog Devices Inc.ADSP - BF531/ADSP - BF532/ADSP-533 embedded processor data sheet[M].USA:Analog Devices Inc,2007.

[7]Analog Devices Inc.EE -240_ADSP-BF533 blackfin booting process[M].USA:Analog Devices Inc,2008.