北斗导航接收机的硬件设计与实现*

2015-12-05李荣冰刘建业尚斌斌

薛 涛 赵 伟 李荣冰 刘建业 尚斌斌

南京航空航天大学导航研究中心,南京210016

北斗卫星导航系统无论在军事战略还是日常生活中都具有重大意义,但在北斗ICD 文件未公布之前北斗终端的研制局限于取得授权的少数国内用户,这使得北斗导航接收机民用服务系统前期建设速度缓慢,进入市场较迟[1-2]。

随着北斗ICD 文件公布,北斗相关技术不断发展与进步,成本逐渐降低,依靠强大的国内市场需求及政府部门的支持,北斗导航系统的客户终端将向通用化、开放化、高速和网络化方向发展,北斗民用应用开发将迎热潮[3]。

在此背景下,通过对北斗导航系统定位过程的分析,研究设计了一种以射频模块、FPGA 和DSP 为构架的民用北斗导航接收机方案。将主控芯片集成在一起,降低了设计和调试难度,提高了系统的实时性能。充分分析了射频模块对天线信号处理的精准性,FPGA 丰富的IO 资源和DSP 快速运算的优势,完成北斗导航接收机的硬件系统设计,并对接收机进行静态及动态测试,最终达到民用接收机的预期性能指标[4]。

1 北斗导航接收机硬件总体方案设计

为了实现定位、定速和定时的要求,接收机首先需要对卫星信号进行下变频及采样,使北斗信号变为调制在中频载波之上的数字信号,方便后级处理北斗信号。同GPS 接收机类似,北斗接收机需要对北斗信号进行捕获跟踪,准确的剥离载波,解调出伪码、导航电文等信息,进而解算出用户的位置、时间和速度等信息,并输出到上位机。整个过程需要在很短的时间内完成,以保证接收机的实时性。根据以上分析,北斗导航接收机的总体设计方案如图1 所示。

图1 北斗接收机的总体设计方案图

2 接收机硬件设计

根据接收机处理北斗信号的工作流程,该接收机主要分为3个部分:射频前端、基带信号处理模块和定位解算模块。要实现接收机的精准定位功能,必须确定各个模块的核心器件的型号及类型,以及充分利用这3个模块的各种资源[5]。

2.1 核心芯片的选择

北斗B1 信号的测距码以2.046Mcps 的码速率调制在1561.098MHz 的载波信号上,到达天线的卫星信号功率最低为-163dBW,深埋于热噪声电平之下,因此射频前端需采用二级或多级下变频,输出的中频信号的质量将直接影响到接收机的定位精度[6]。除接收北斗卫星信号外,射频电路还需要对噪声信号进行抑制[7]。对于射频前端的研制,市场上有专用的射频板及射频芯片,射频板虽然价格低廉,但由于与基带处理部分距离较远,造成的噪声干扰相对较大,实时性低。射频芯片可直接焊接在基带板中,虽价格稍贵,但实时性等性能较射频板有很大提升。为进一步提高接收机的性能,选用中电某所生产的射频芯片SFM。该芯片将低噪声放大器、下变频器及带通滤波器等模块集成在一起,并用屏蔽罩与外界隔离,它的面积只有20 mm × 20mm,满足了小体积和抗干扰能力强的要求。

基带信号处理模块需要产生本地载波和本地复制码,与数字中频信号进行载波和码相关,需要多个信号通道,有较快的数据处理速度、丰富的I/O 资源以及适当数量的PLL 模块。经上述分析,本设计选用Alter 公司的Cyclone II 系列的FPGA 为基带信号处理部分的主控芯片。该芯片配置的IO 口数量可达到四百多,内部集成4个PLL 模块,核心频率可以达到几百兆,完全满足各通信接口的时钟要求;该芯片的内部程序可以并行运行,保证了数据的实时通信,提高了系统的工作效率[8]。

由于接收机要求实时性比较高,这就要求定位解算模块能够在较短的时间内处理大量的数据,可靠性高,主频时钟范围比较大。因此本系统选用TI公司的32 位高速浮点型DSP TMS320C6713B 作为北斗接收机的定位解算部分的主控芯片。它采用了VLIW 的体系结构及流水线技术,具有两级cache 缓存结构,自身运算速度快,精度高,其最高主频可达300MHz,内部有PLL 模块,提供的32 位EMIF 总线可与FLASH,SDRAM 等外部储存器实现无缝连接,同时其自身也带有多个外部中断引脚,方便外部中断的使用。

2.2 射频前端设计

SFM 可接收有源天线或无源天线信号输入,内部集成由低噪声放大器(LNA)、射频混频器(RT Mixer)、中频可变增益放大器(IF VGA)、中频混频器(IF Mixer)、中频滤波器(IF Filter)、自动增益控制电路(AGC)和2个独立的频率合成器((PLL)等功能单元。可输出能驱动50Ω 负载的模拟46M 中频信号和供基带部分使用的62MHz 低相噪时钟信号。SFM 功能框图如图2 所示。

图2 SFM 功能框图

模拟46M 中频信号需要通过AD 转换为数字信号后,再传向接收机基带部分。模拟中频信号输入带宽为4M,这要求AD 不仅要有高速的采样率,还应具有足够大的带宽。根据以上性能指标,选用了Analog Devices 公司的AD9288 作为采样芯片,它是一种高速,低功耗,双通道8 位转换精度、最高采样率为100M 的A/D 转换器。双通道可采用采样时钟相位相差180°采样,可实现对一组数据的2 倍采样,在采样率方面可以满足接收机的需求。

2.3 基带信号处理模块设计

接收机能否产生精确、同步的时钟信号是其能否精确定位的关键。普通的晶振容易受温度等环境状况影响,因而系统采用了温补晶振为接收机提供时间基准,它可以修正由温度变化引起的谐振频率的变化。FPGA 输入时钟有2个:1)射频前端传过来的62M 低相噪时钟信号;2)来自10M 温补晶振,并且FPGA 内部集成锁相环,可以将外部时钟倍频及分频,核心频率可以达到几百兆,可满足AD 采样及各种通信接口对时钟的要求。

本文采用信号通道的形式去处理不同可见卫星的信号,所以必需根据接收机所允许配置的硬件资源实行资源分配策略。充分考虑到FPGA 丰富的硬件资源,每一个通道可以独立占用一条硬件通道,而不同的硬件通道可同时高速运行,这样极大的提升了基带的处理速度及实时性[9-10]。

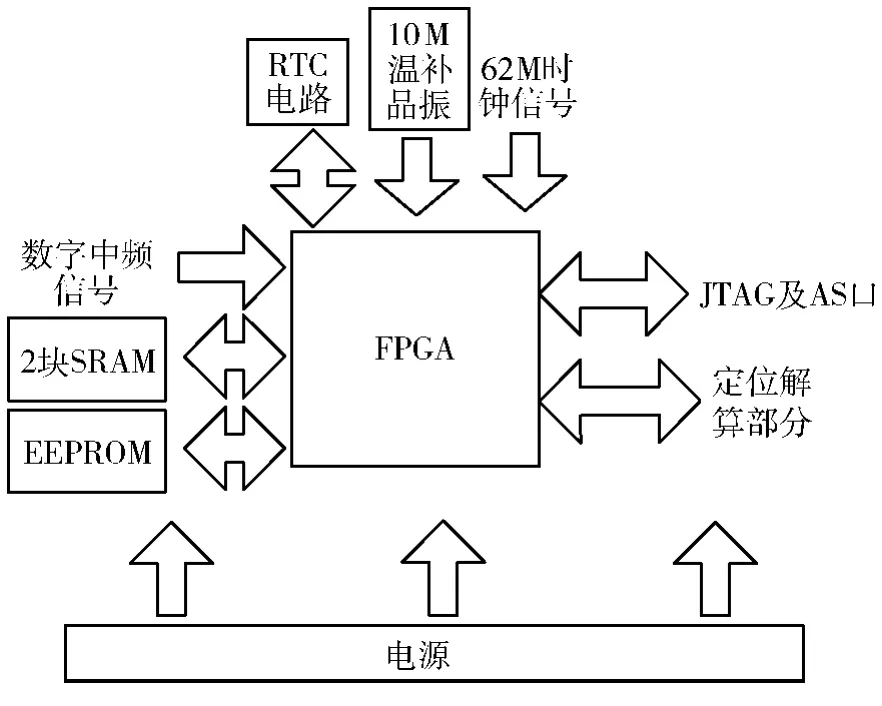

基带信号处理模块硬件电路主要包括系统主时钟电路、RTC 电路和AD 采样数据存储电路设计等,其硬件结构框图如图3 所示。

2.4 定位解算模块设计

图3 基带信号处理模块硬件结构框图

由于数据量较大,以及DSP 自身启动需要外部存储器的配合,因此,DSP 可通过其外部存储器接口(EMIF)与外存储器进行无缝连接。DSP 的CE1 空间外接FLASH,主要用于存储DSP 运行代码和大量用户非易失性数据。DSP 的CE0 空间外接SDRAM,主要用于扩展DSP 外部存储器资源,同时FPGA 也与EMIF 总线相连,配置在DSP 的CE2 空间,方便与DSP 之间进行通信。这样就保证了数据实时高速传输给DSP 进行解算。与上位机的通讯主要是通过DSP 片上的2个MCBSP(多通道缓冲串行接口)扩展配置而成的RS232 串口进行的。

定位解算模块硬件电路主要包括DSP 复位、串口输出和数据存储电路等。其硬件结构框图如图4 所示。

图4 定位解算模块硬件结构框图

3 接收机底层硬件驱动设计

接收机底层硬件驱动设计主要包含以下3个方面:1)二级引导程序设计;2)FLASH 烧写程序设计;3)DSP 的驱动程序设计。

为了获得较高的运行速度,通常要把低速FLASH 中的代码传送到高速RAM 中执行,但大部分应用程序都要超出1KB,显然上述的FLASH 引导过程不能满足全部程序传输的需要,这就需要编写一段“二级引导程序”来完成剩下的传输工作,并通过与FLASH 烧写程序的配合,实现程序的快速烧写与运行[11]。

北斗接收机快速烧写及运行程序流程如图5 所示。

图5 北斗接收机快速烧写及运行程序流程图

此外,还要编写DSP 驱动程序,实现DSP 与FPGA 的实时通信,并将解算的临时数据存到SDRAM里,并利用EDMA 的方式,快速将解算得到的数据输出到上位机。利用TI 官方提供的例程可快速完成驱动程序的开发。

4 测试结果

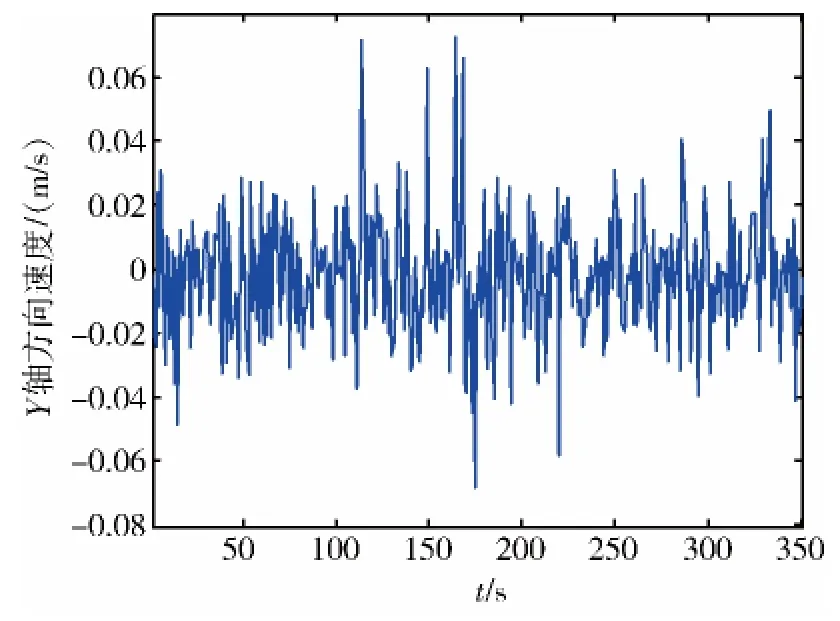

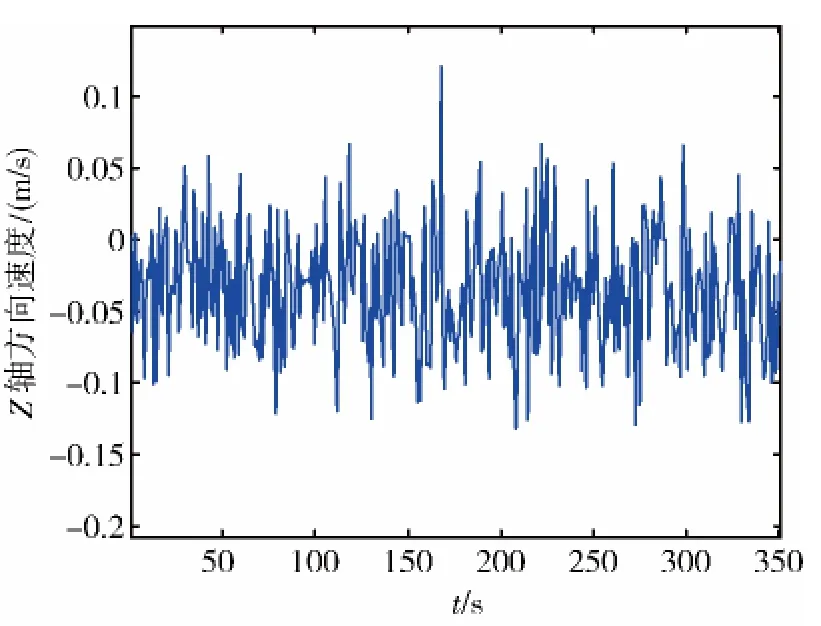

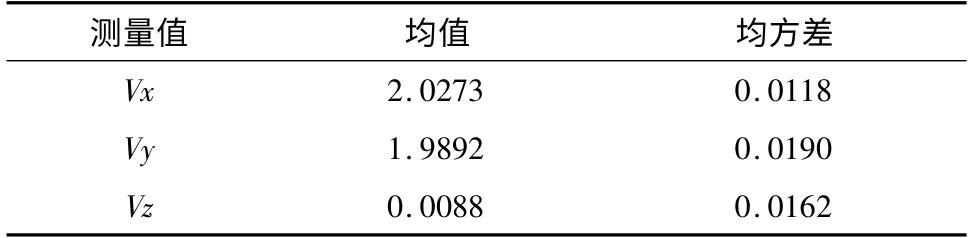

为验证本系统的可行性以及软硬件设计的正确性,将系统各部分调试完成后,采用北斗B1 信号,与接收机软件配合进行静态性能测试、低动态性能测试(Vx=2m/s,Vy =2m/s,Vz =0 m/s)、高动态性能测试(Vx =100m/s,Vy =100m/s,Vz =0 m/s),实验结果如下。

图6 X 轴方向速度静态测试图

图7 Y 轴方向速度静态测试图

图8 Z 轴方向速度静态测试图

表1 静态性能测试数据均值及方差

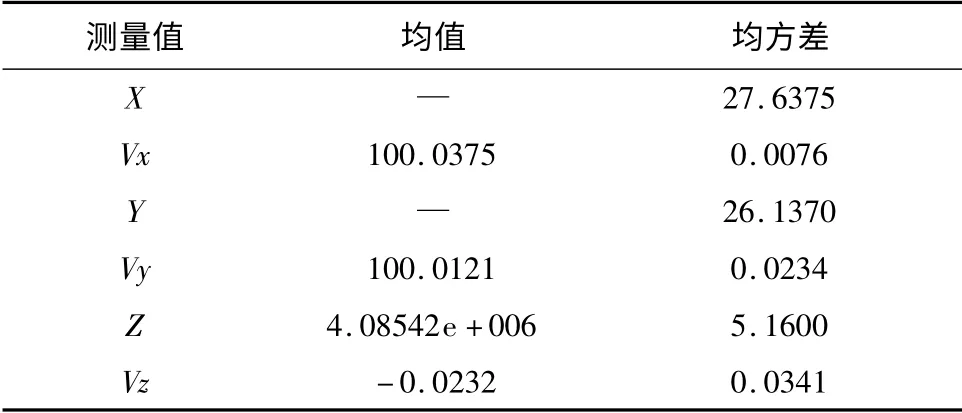

表2 低动态性能测试数据均值及方差

表3 高动态性能测试数据均值及方差

实验结果表明,所研制的北斗接收机可以完成对北斗卫星信号的采集、转换及定位解算,将位置和速度输出。在静态、低动态及高动态情况下,接收机可实现定位定速,能满足实时性高等预期的性能指标要求。

5 结论

提出了一种北斗导航接收机的设计方案,并由此完成了北斗接收机硬件及底层硬件驱动程序的设计和实现工作。经多次测试,该接收机设计正确无误,与接收机软件配合,能为用户提供准确的位置和速度等参数输出,能达到预期的性能指标。本文设计的北斗导航接收机在交通工具导航系统、地球信息系统(GISS)等方面均具有良好的发展前景。

[1]葛榜军,贠敏.发展北斗导航产业的思考[J].卫星应用,2014(6):29-30.(GE Bangjun,YUN Min. Thoughts on the Development of Beidou navigation industry[J].Satellite Application,2014(6):29-30.)

[2]李树洲,王党卫.卫星导航接收机技术发展趋势分析[J]. 现 代 导 航,2014,37 (5):1-5. (LI Shuzhou,WANG Dangwei. Analysis of the Development Trend of Technology of Satellite Navigation Reciver[J]. Modern Navigation,2014,37(5):1-5.)

[3]陈洪卿.北斗系统与中国PNT 应用平台[J].电子测量与仪器学报,2010,24(12):1075-1078. (CHEN Hongqing. Beidou System and PNT Application Platform of China [J]. Journal of Electronic Measurement and Instrument,2010,24(12):1075-1078.)

[4]彭宇.基于DSP 和FPGA 的通用数字信号处理系统设计[J]. 国外电子测量技术,2013,32(1):17-20.(PENG Yu. Design of General Digital Signal Processing System Based on DSP and FPGA[J]. Foreign Electronic Measurement Technology,2013,32(1):17-20.)

[5]戴陈靓,赵伟,刘建业. 导航计算机测试系统的研究与实现[J]. 电子测量技术,2014,37(5):42-45.(DAI Chenliang,ZHAO Wei,LIU Jianye.Research and Implementation of Navigation Computer Test System[J]. Electronic Measurement Technology,2014,37(5):42-45.)

[6]邓艾,葛利嘉,徐自玲,等.一种用于软件无线电的接收机射频前端电路设计与实现[J]. 现代电子技术,2010,15:38-40. (DENG Ai,GE Lijia,XU Ziling,et al. A Method for the Design and Implementation of the RF Front-end Circuit of the Software Radio Receiver[J]. Modern Electronic Technology,2010,15:38-40.)

[7]周超,吕健,邓浩. 嵌入式系统电磁兼容设计研究[J].软件导刊,2011,10(1):21-23.(ZHOU Chao,LV Jian,DENG Hao. Research and Design on the Electromagnetic Compatibility of Embedded System[J]. Software Guide,2011,10(1):21-23.)

[8]刘竞超,邓中亮.基于ARM +FPGA 北斗接收机设计[J]. 软 件,2012,33(12):38-40. (LIU Jingchao,DENG Zhongliang. Beidou Receiver Design Based on ARM+FPGA[J]. Software,2012,33(12):38-40.)

[9]李荣冰. 大气辅助的SINS_GPS 组合导航系统研究[J]. 仪器仪表学报,2012,33(9):1962-1964. (LI Rongbing. Research on SINS/GPS integrated navigation system with air data system[J]. Chinese Journal of Scientific Instrument,2012,33(9):1962-1964.)

[10]袁俊刚,范胜林,刘建业.INS 辅助的GPS 接收机快速捕获技术研究[J]. 弹箭与指导学报,2011,31(1):49-51. (YUAN Jungang,FAN Shenglin,LIU Jianye.The Research on GPS Signal Fast Acquisition Technique Aided by INS [J]. Journal of Projectiles,Rockets,Missiles and Guidance,2011,31(1):49-51.)

[11]毛文安,张海峰. 基于TMS320 DM642 的Flash 头文件烧写法的DSP 二级BootLoader 开发[J]. 机电工程,2014,31(3):400-403. (MAO Wenan,ZHANG Haifeng. DSP second-level Bootloader developing based on Flash header file burning of TMS320DM642 [J].Journal of Mechanical&Electrical Engineering,2014,31(3):400-403.)