一款高性能时钟驱动器电路的设计

2015-12-05欧阳雪

欧阳雪

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着半导体工艺速度和集成度的提高,以及模拟集成电路设计能力的提升,时钟器件芯片的产品形态越来越丰富,大大提升了系统时钟方案设计的灵活性,同时降低了系统时钟方案总成本。目前,时钟器件芯片已被广泛应用于无线通信、数据网络、消费电子、医疗设备和安防监控等领域,可以实现通信网定时同步、时钟产生、时钟恢复和抖动滤除、频率合成和转换、时钟分发和驱动等功能。本文所述为一款高性能时钟驱动器电路的设计实现。在系统设计中,选用好的时钟驱动芯片,可以省去系统时钟树设计,既节省空间,又提高系统性能。

2 时钟驱动器概述

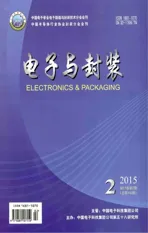

本文所设计的电路是仿制美国TI公司出品的CDCV304型PCI-X兼容时钟驱动器。该器件提供1∶4的输出扇出比,是一种来自单一输入的大扇出比电路,该电路减小了前级驱动器的负载并能提供一种有效的时钟缓冲网络。当OE使能端无效时,该电路输出恒定为低电平,使得该驱动器的平均功耗大大降低。图1是该电路的功能结构设计要求。

图1 时钟驱动器的功能框图

3 时钟驱动器的设计

3.1 功能设计

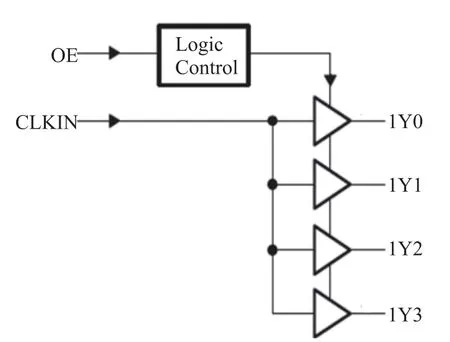

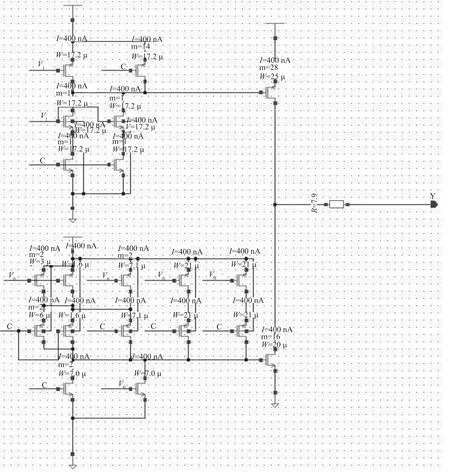

图2 时钟驱动器的逻辑设计架构图

图2是根据设计要求制作的最简时钟驱动器的逻辑设计架构图,可以看到主要部件分为输入保护及控制、内核驱动、输出控制及输出驱动三大部分。

3.2 性能实现

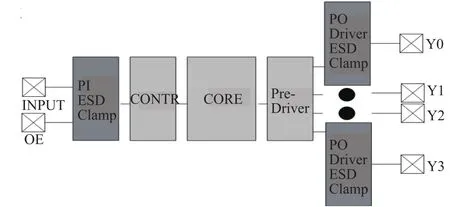

3.2.1 低传播延时设计

如图3所示,包含作为ESD保护用的限流电阻和NMOS管。由于限流电阻阻值远大于NMOS管的导通内阻,防止ESD放电过程中对MOS器件栅极的冲击。输入信号经过两级反相器加入到内部,第一级反相器起缓冲作用,第二级作为驱动级。输入压焊块端的信号可能会不稳定,不是正常的高(VDD)低(0)电平,经过第一级缓冲作用,使电平匹配,也即对波形进行整形。这样经过第一级的波形是确定和稳定的,而后驱动第二级,第二级是直接驱动内部电路的管子,所以第二级的W/L大于第一级的W/L,同时第二级也可以进一步整形。

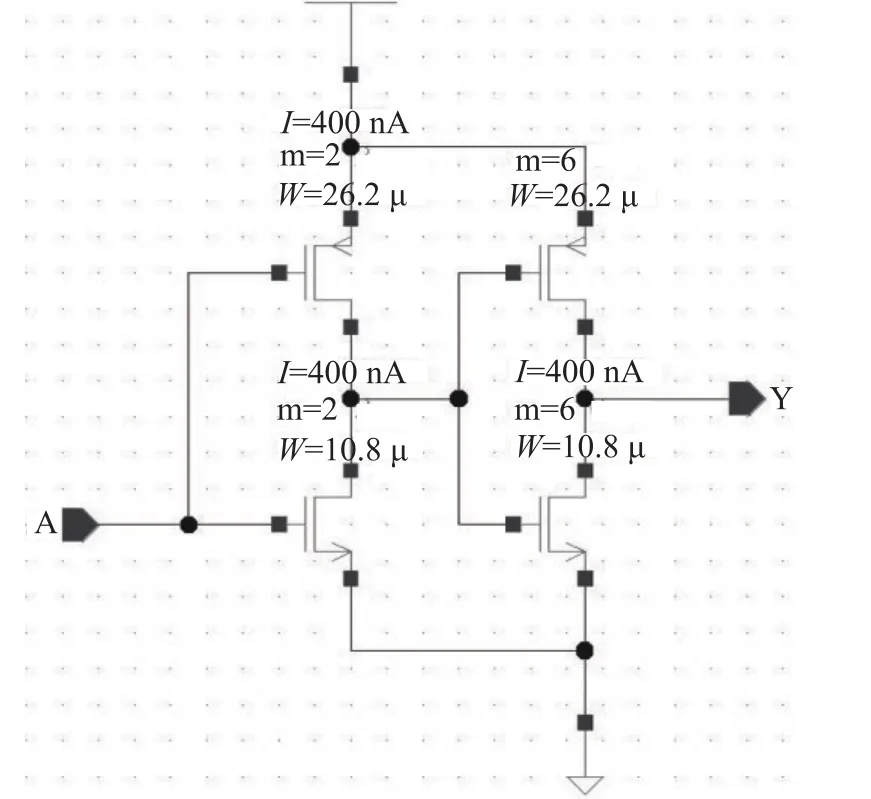

如图4所示,内核电路为两级反相器,在设计时为了使电路充、放电速度相等、波形对称,并且保证各种条件下电路的稳定性,并根据工艺厂商的标准PCM参数设计,取(W/L)P=2~3(W/L)N。

输出控制及输出驱动部分电路设计如图5所示,输出电路是该电路中一个比较重要的模块。该部分在原理上并不复杂,主要是满足输出驱动能力及速度的要求。采用分时错开控制输出大驱动NMOS、PMOS管,由与非门控制输出高电平的PMOS管,或非门控制输出低电平的NMOS管。驱动管宽长比设置接近样品尺寸,以保证输出驱动能力与样品相当。

图3 输入保护及控制电路设计

图4 内核驱动电路设计

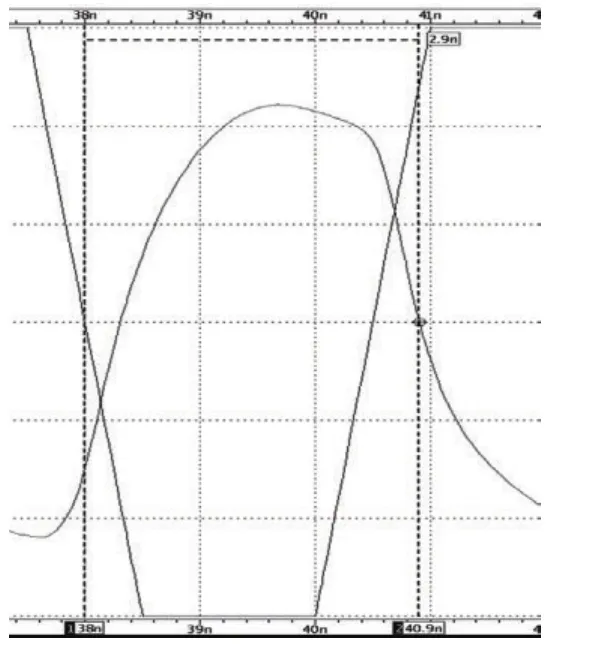

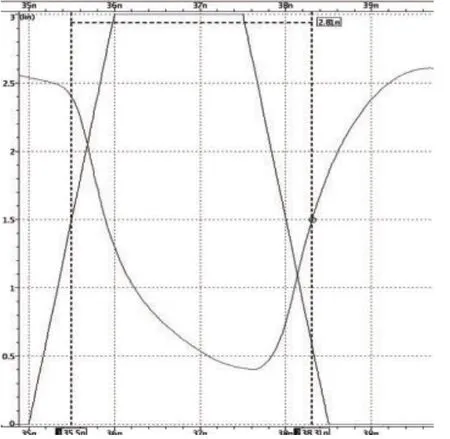

该电路采用以上设计,在保证波形质量的前提下以最少的倒相器级数完成电路设计,保证了3.3 V电源工作条件下电路的传播延时值小于3 ns。实际仿真图形如图6、图7所示,在SS模型、125 ℃、外带10 pF负载情况下,tPLH为2.81 ns ,tPHL为2.9 ns,均小于规范要求的3 ns时间。

3.2.2 低输出偏斜设计

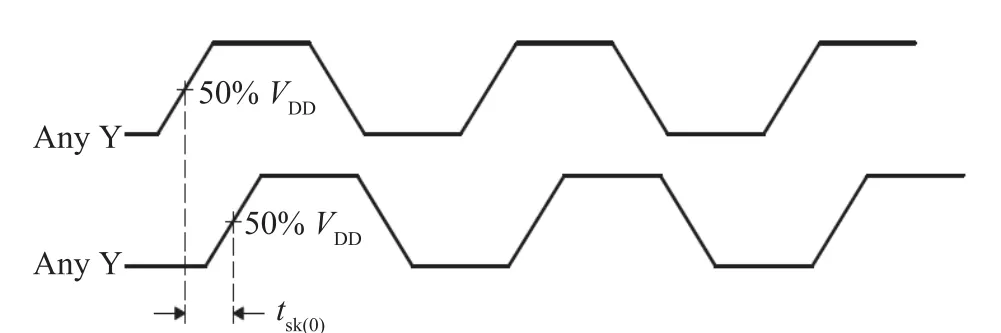

图8定义了该时钟驱动器4个输出端口的波形偏斜图,并要求其值小于100 ps。该项要求主要通过版图布局实现。在版图布局时4个输出端口距离内核驱动电路的绝对路径必须基本无差别。布线时4条路线的走线长度也要做到基本接近,4个输出端口到管壳压焊指的位置也要精心挑选设计,才能满足该项要求。

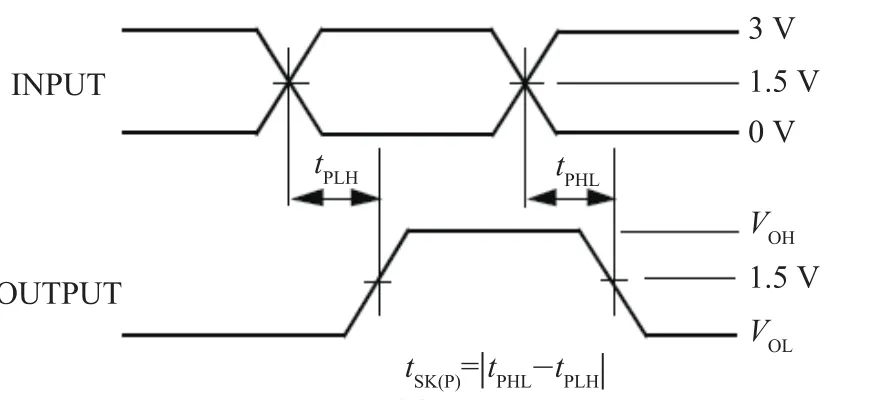

图9定义的是时钟驱动器1个输出端口上升延时及下降延时的偏斜波形图,并要求其值小于150 ps。该项要求主要通过电路设计时对输出模块的输出驱动电路的宽长比设计来满足。在仔细查阅工艺厂商提供的标准PCM参数文件后,计算出最佳的PMOS及NMOS驱动管的匹配宽长比值,并进行全温、多种PVT条件的版图参数提取后仿真,最终确定为图5所 示宽长比值,满足设计要求。

图5 输出控制及输出驱动部分电路设计

图6 tPHL,IN to Y仿真波形

3.2.3 低抖动设计实现

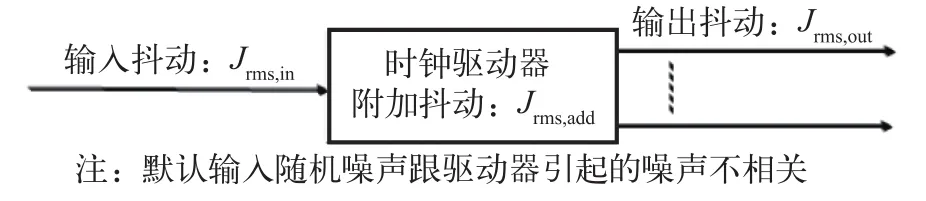

时钟驱动器的主要功能为时钟信号分发和增强驱动能力,表征抖动性能通常采用的是附加抖动指标,如图10所示,附加抖动被定义为:Jrms,add=。为了准确表征驱动器本身引入的抖动指标,必须要求输入均值抖动小于器件本身的附加抖动。该电路要求在12 kHz~20 MHz积分带宽内,在125 MHz偏置频率驱动器对应的附加抖动指标典型值为56 fs,该项要求仿真无法实现,通过采取电路抗干扰设计措施,使得电路的测试结果满足设计要求。

图7 tPLH,IN to Y仿真波形

图8 不同输出端口偏斜图

图9 同一输出端口上升下降偏斜

图10 时钟驱动器噪声分布图

3.2.4 降低电磁干扰设计

在高速数字系统中,固定频率的时钟是主要的电磁干扰源。这些时钟总是在一个固定的频率下工作,这将使能量增加到更高的级别。随着更高的数据速率要求更快的时钟频率,信号的边沿率(即上升下降时间)也随之提高。较快的边沿率将使辐射信号的能量级别增加更多。另外,在电路设计中,时钟线路的阻抗不匹配将会导致线路信号出现正向或负向过冲,在这种情况下辐射能量将会增加。降低电磁干扰的方法有3种:屏蔽、滤波和降低功耗,后两种方法在本电路设计中有应用,使该电路具有较好的抗干扰能力。

3.2.5 抗ESD能力设计

端口保护电路是该电路中一个比较特殊的模块。该设计采用PMOS管控制泄放大电流通路的NMOS保护管。此外,该结构还能在电源误接低电压时对端口起保护作用。端口保护电路图如图11所示。

图11 端口电路ESD保护电路图

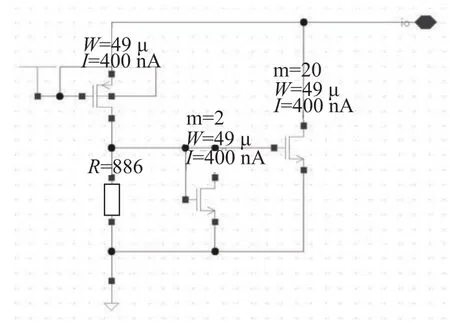

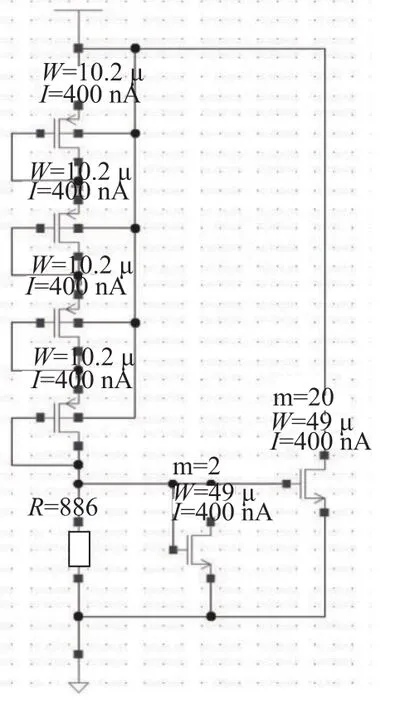

电源保护电路是该电路中一个比较特殊的模块。该设计采用4个PMOS管串联控制泄放大电流通路的NMOS保护管,该结构的电阻选取合适的电阻值以保证电源能稳定工作在10 V以下,保证电路在电源偶有波动时能稳定正常地工作。电源保护电路图如图12所示。仿真结果表明电源电压在7~8 V之间才能产生大电流通路,保证电路在3.3 V的工作电压下稳定工作,裕量较大。

图12 电源电路ESD保护电路图

4 时钟驱动器的实现

按照上述设计,笔者设计的时钟驱动器电路的工作时钟为200 MHz。工艺制作后采用陶瓷管壳封装,通过系统测试,该时钟驱动器性能指标达到了设计要求,输出时钟工作频率大于200 MHz,传播延时时间小于3 ns,输出偏斜值达到50 ps,满足小于100 ps的要求,抗ESD能力大于4 000 V。

5 结束语

本文介绍了一款高性能时钟驱动器集成电路的设计,用该方法设计的时钟驱动器经过国内工艺厂商中芯国际制版流片、中微高科公司封装、58所检测中心检测,该电路满足设计要求,完成国产鉴定,并向用户供货,取得较好的效益。

[1] 正确理解时钟器件的抖动性能:Application Report,ZHCA492 – JAN, 2013.

[2] Jan M Rabaey Anantha Chandrakasan Borivoje Nikolic著,周润德,等译. 数字集成电路——电路、系统与设计[M]. 北京:电子工业出版社,2004.