一种基于串行通信接口的采样速率测试方法

2015-12-05杨萌兮

张 继,杨萌兮,谢 达

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

在工业控制领域,绝大部分DSP/MCU系列产品都包含用于通信的串行接口电路(Serial Communications Interface,SCI),以满足工业控制高度集成、高性能解决方案的严格要求。本文提出了一种将串口收/发送器速率与串口接收器采样速率配置成一定配比关系,可以实现用于测试串口接收器的任意帧结构数据的方法,以验证串行通信接口相应功能的正确性,提高芯片测试的良品率。

2 SCI控制器

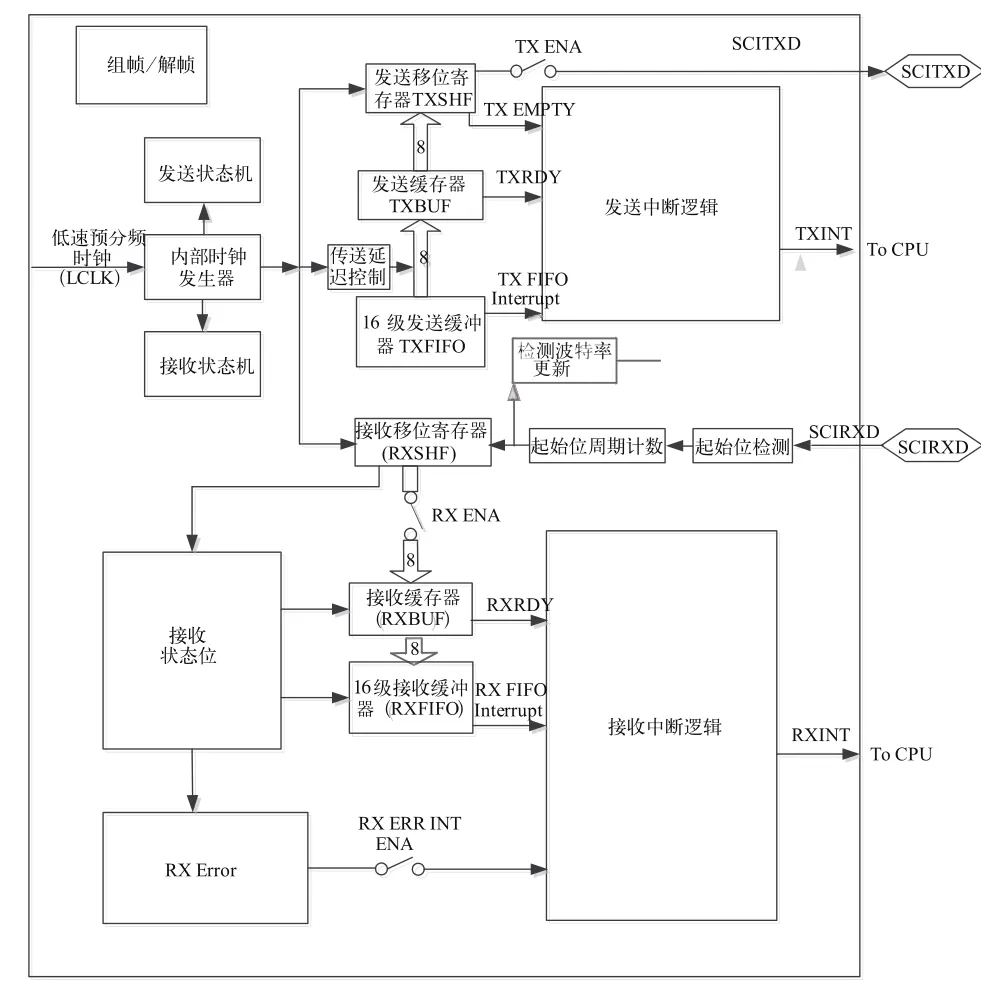

一般DSP芯片都包含至少一个SCI接口,用于支持CPU与其他异步外设之间使用标准非归零码(NRZ)格式的数字通信。通常每个SCI包含一个波特率发生器、数据发送器、数据接收器以及数据存储映射控制和状态寄存器,如图1所示。

2.1 SCI通信原理

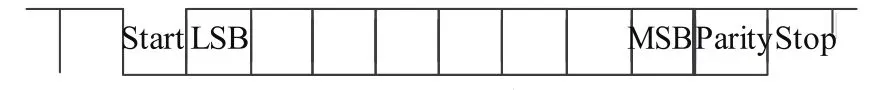

由于SCI是串行异步通信方式,因此在通信过程中每次只能传输1位(bit),若干位组成一个数据帧(frame),帧是通信中最基本的单元,它主要包括起始位、数据位、校验位(如果使能了数据校验,要包括校验位)和停止位,帧结构如图2所示。

图1 SCI内部结构

图2 SCI数据帧格式

SCI在通信之前要在发送端和接收端约定好帧结构,也就是约定好传输数据帧格式:

(1)起始位:必须包含在数据帧中,表示一个帧的开始;(2)数据位:可选的1~8位,该位长度可由编程人员指定;(3)校验位:如果在使能了数据校验时,该位必须指定;(4)停止位:可选的1~2位,该位长度可由编程人员指定。

为了确保数据完整性,SCI在中断检测错误位(BRKDT)、奇偶校验错误位(PE)、过载错误位(OE)和组帧错误位(FE)方面对接收到的数据进行检查。

2.2 SCI数据通信速率

SCI数据通信速率指设备在一秒钟内发送(或接收)了多少比特的数据,即传输时的波特率。通信双方在约定好帧格式后,通过指定一个16位波特率选择寄存器的值(BR),可将波特率设定为65536个不同的速度。波特率的计算公式如下:

Baud rate =LCLK/[(BR+1)×8],when BR≠0;

Baud rate =LCLK/16,when BR=0。

指定同一波特率,数据通信的双方便可以进行数据传输了。

2.3 SCI接收采样速率[1]

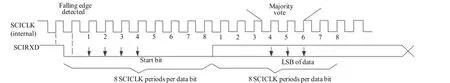

在数据通信时,每一位的信号占用N个SCI内部生成的串行时钟(SCLK)周期,该内部时钟SCLK的频率可以通过波特率寄存器(BR)来控制,一般计算公式为:SCLK =LCLK/(BR+1)。SCLK与起始位以及其他数据位间的关系如图3所示。

图3 SCI接收器信号采样

如图3所示,有效的起始位判别为在串行通信总线拉低后满足连续采样到4个SCLK周期的0位信号,如果有任何一位不为0,则处理器将重新开始寻找其他的起始位。在识别了起始位后,后续的数据位采样采用多数仲裁机制:采样判决信号为采样数据信号的4、5、6位上,且其中满足有2个或3个为逻辑1,则该位的采样值判定为逻辑1; 若其中有2个或3个为逻辑0,则该位的采样值判定为逻辑0。

3 SCI的功能验证设计

通过一个功能正确的SCI可以设计验证另一个SCI的功能正确性,并且可以量化生产测试,从而提高测试自动化效率。本文的设计假设在SCI采样信号为8个。SCI模块的功能验证主要包括:数据帧格式验证、通信速率(即波特率)验证、数据发送和接收深度验证、数据有效性检测逻辑验证以及SCI中断响应验证等方面。

以上需要验证的方面,只有通信速率(即波特率)需要实际测算波特率配置,其他都可以通过设计好的两两间相互通信的数据来验证。这些验证方面的设计分为通信速率的计算和通信格式的配置。

3.1 SCI功能验证通信速率计算

SCI功能验证数据格式的设计本质上是要实现输入特定的测试数据,通过检测对应的逻辑功能是否工作(即检测响应数据)。利用SCI来构造满足要求的测试数据,需要克服SCI通信格式上的束缚,即测试数据的格式能够向下兼容SCI的通信数据格式。

在图3所示的例子中,接收器1位采样占用8个SCI内部时钟周期,由此可推断出:只要满足发送器的发送速率Baud rate TX是接收器的接收速率Baud rate RX的8倍,即可满足测试数据的格式能够向下兼容SCI的通信数据格式,即Baud rate TX = 8×Baud rate RX;又由Baud rate公式可知,发送器的BR TX和接收器BR RX间满足BR TX+1=(BR RX+1)/8。

3.2 SCI功能验证通信格式设计[2]

如前文所述,SCI的数据通信格式包括起始位、数据位、空闲线模式/地址位模式位、校验位(如果使能了数据校验,要包括校验位)和停止位。考虑到校验位的值与数据位以及校验模式有关,为了简化设计,发送器采用如下设计的帧格式:1个起始位为逻辑0,6个数据位为逻辑0或逻辑1,不使能校验位,以及一个停止位为逻辑1。

发送需要针对3种类型的数据位进行设计约束(也即对发送数据的有效数据位进行设计):起始位配置、接收器逻辑0配置以及接收器逻辑1配置。

3.2.1 起始位配置

在图3所示的例子中,接收器的起始位判决逻辑在第1、2、3、4位采样信号上,因此发送数据的第5、6、7、8位对采样信号的判决没有影响。且接收器的起始位是逻辑0,因此发送器的8位数据可以配置为:1个起始位为逻辑0,6个数据位为逻辑0,不使能校验位,以及一个停止位为逻辑1,也即配置寄存器SCITXBUF = 0x01。

3.2.2 接收器逻辑0配置

在图3所示的例子中,接收器的数据位判决逻辑在第4、5、6位采样信号上,因此发送数据的第1、2、3位以及第7、8位对采样信号的判决没有影响。发送端的8位数据配置可以配置为:1个起始位为逻辑0, 6个数据位为逻辑0,不使能校验位,以及一个停止位为逻辑1,也即配置寄存器SCITXBUF = 0x00。

3.2.3 接收器逻辑1配置

在图3所示的例子中,接收器的数据位判决逻辑在第4、5、6位采样信号上,因此发送数据的第1、2、3位以及第7、8位对采样信号的判决没有影响。发送端的8位数据配置可以配置为:1个起始位为逻辑0, 6个数据位为逻辑1,不使能校验位,以及一个停止位为逻辑1,也即配置寄存器SCITXBUF= 0x3F。

综上所述,发送器发送起始位数据和逻辑0数据可以统一采用发送数据SCITXBUF = 0x01。TI针对小数据量多机通信而设计的地址/数据识别也只是在接收器端完成的,利用设计的8倍速率进行数据传输,同样可以实现相关逻辑的验证,只要配置发送器的第7位为相应的状态即可。

4 SCI功能验证的仿真

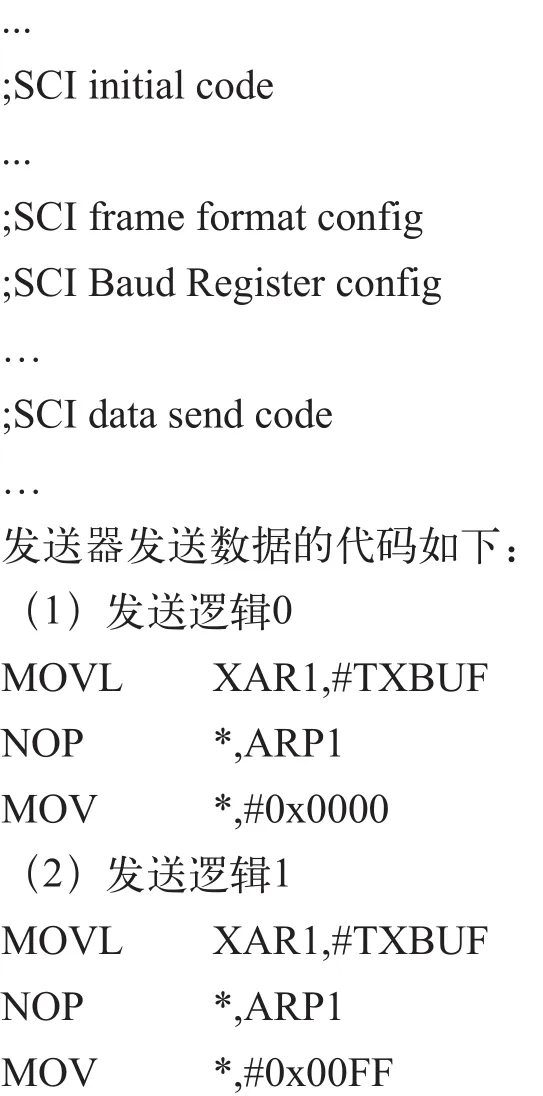

在Linux环境下,利用Candence的NC-Verilog软件对某款DSP芯片进行仿真。配置好仿真参数后,加载采用了基于8倍通信速率设计的测试代码,对SCI通信模块进行仿真验证。设计实现仿真用的主要配置的伪代码如下[3]:

在上面的代码中,前面初始化部分包括SCI的LCLK时钟配置,GPIO引脚功能复用配置以及SCI模块使能等;之后便是配置SCI收发数据的双方配置为所设计的帧格式以及相应的波特率配置,最重要的配置为帧格式配置寄存器和波特率寄存器的配置,发送器的波特率配置为1,接收器的波特率配置为15(即0xF),从而满足公式:BR TX+1 =(BR RX+1)/8。发送数据的高两位(第7、8位)不会发送,可以为任意值,代码中统一配置为1或者0。

配置好软硬件环境和代码后进行仿真,得到仿真实验结果如图4所示。从仿真结果可以看到,SCI接口A发送数据速率是SCI接口B接收速率的8倍,SCI接口A每发送8个数据,对应完成SCI接口B接收到的1位数据;SCI接口A每发送8位数据,SCI接口B接收到完整的1帧数据。

图4 仿真实验结果

5 结束语

本文重在如何简化并快速进行串口模块的功能验证,在研究了模块自身功能特性的基础上,提出了一种具有一定通用性的设计思想,即利用通信速率和采样速率之间的关系,将串口收/发送器速率与串口接收器采样速率配置成一定配比关系,从而实现用于测试串口接收器的任意帧结构数据。

本文的设计方法的主要思路是:首先,依据设计的帧格式应该能够向下兼容SCI的通信格式,即要实现发送器发送数据可以实现任意所需要接收端测试数据,从而设计了通信速率上8倍的关系;其次,根据接收器采样信号的判决位置,设计了长度为8个位的发送器数据帧结构,并选择了最简的位配置,定义了用于确定接收器起始位、逻辑0和逻辑1的发送数据。利用所设计的帧格式配置进行仿真验证,证明该设计方法确实可以实现满足任意要求的测试数据,并完成了接收数据正确性检验标识(OE、PE、FE、BRKDT)、多处理器通信地址位模式、SCI中断控制以及16级数据缓冲等相关功能的验证。

利用该方法,可以简化对DSP芯片中SCI接口功能的测试设备要求,从而提高测试自动化效率。

[1] Texas Instruments.TMS320F28335 Digital Signal Controllers (DSCs) Data Manual[P]. 2007.

[2] 张雄伟,等. DSP芯片的原理与开发应用(第二版)[M].北京:电子工业出版社,2000.

[3] 汪安民,程昱. DSP应用开发实用子程序[M]. 北京:清华大学出版社,2009.