基于FPGA的信号源的设计

2015-11-30徐红丽

徐红丽

(湖南信息职业技术学院,湖南长沙,410200)

基于FPGA的信号源的设计

徐红丽

(湖南信息职业技术学院,湖南长沙,410200)

在电子信息技术快速发展的条件下,可编程逻辑器件(FPGA)与直接频率合成技术(DDS)也在不断更新。同时,人们在社会生产生活中对其应用条件也提出了更高的要求。基于此,本文本着降低设计成本、提升设计质量的原则,设计了基于FPGA的DDS信号源。

FPGA;DDS;信号源

0 引言

信号发生器也叫作信号源,它在人们的生产生活中应用十分广泛。尤其是在电子信息技术不断进步的大趋势下,基于DDS技术的信号源以其频率分辨率、可编程的相位输出等优势得到社会各界广泛认可。而利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器,可以实现操作更加灵活,并能够满足预定指标的多波形输出目标。因此,本文主要通过对可编程逻辑器件(FPGA)与直接频率合成技术(DDS)的分析,设计了基于FPGA的DDS信号源,大大提升了操作的灵活性,运行的可靠性,满足预定指标的多波形输出。

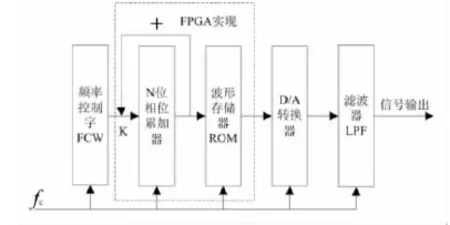

图1 FPGA内部模块结构

1 可编程逻辑器件(FPGA)

可编程逻辑器件(FPGA) 是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,是基于PAL、GAL、CPLD等可编程器件的发展而逐渐成熟起来的,它不仅克服了定制电路存在的不足,同时也很好地解决了可编程器件门路数限制问题。FPGA内部模块结构如图1所示:

FPGA 内的一切数据由上位机通过 USB传送而来,传输的数据根据不同的地址传送到 FPGA 芯片内部不同的寄存器,然后由 FPGA 内部的控制通信控制程序将数据写入不同的模块。另外,还完成了监控数据经过FPGA 传输到上位机的功能,该监视数据发送到了上位机接收测试信号的模块。

本研究选择的是深圳同创国芯电子有限公司自主研发的Titan系列可编程逻辑器件,Titan系列高性能FPGA有两大特点,一是Titan系列它是中国第一款千万门级FPGA; 二是采用了先进的40nm制程。该产品规模为3万至32万个可编程基本逻辑单元,带有DDR3和PCIe接口。Titan系列产品包含创新的可配置逻辑单元(CLM)、专用存储单元(DRM)、算术处理单元(APM)、多功能高性能I/O以及丰富的片上时钟资源等模块,每个CLM包含6个寄存器,每个DRM内嵌两个18*18单元,可实现27*27运算,基于Bank的IO分组,VCCIO支持1.2V、1.5V、1.8V、2.5V及3.3V,支持多种输入输出标准,时钟频率可达500MHz。Titan系列可编程逻辑器件是一款能够提供高性能,大容量,差异化应用的FPGA产品。

2 直接频率合成技术(DDS)

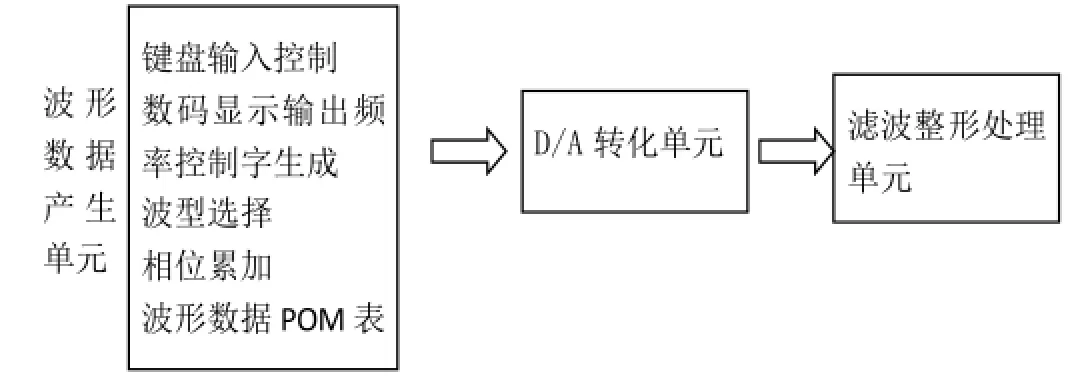

根据采用定理,DDS对需要产生的波形进行采样,并在对采样值数字化处理后,在存储器中将处理后的采样值进行存储,同时将其作为查找表以读取数据,继而通过D/A转换器将其转换为模拟量,最后重新合成出波形。DDS基本原理如图2所示。

图2 DDS基本原理图

其工作过程是,在全局时钟的驱动下,相位累加器对频率控制字不断的做累加运算,根据奈奎斯特定理知道参考时钟的频率一般为DDS输出信号最高频的2倍。将得到的输出信号以波形存储器地址形式进行输入后,波形存储器的数字信号输出借助于D/A转换器转换为模拟信号,最后借助于低通滤波器即可实现模拟信号中高频分量的滤除,并得到纯净的输出信号。

3 系统总体方案设计

该系统在设计过程中,以FPGA为开发平台,通过ROM存储各波形幅值/相位量化数据,根据设定频率,以相应频率控制字k为步进实现相位累加,借助于累加相位值为地址码对存储器内的波形数据进行读取,并通过D/A转换、滤波及幅度控制得到最终波形。本研究中的波形发生器采用了数字化结构,实现了频率的调节与直观显示,硬件描述语言为Verilog 语言。系统总体设计如图3所示。

图3 系统总体设计图

系统中主要有三个单元,即D/A转化单元、波形数据产生单元、滤波整形处理单元。D/A转换单元的主要功能主要是从ROM表里读取的波形数据进行D/A转换。在实际操作中,D/A转换器件的选择要注意建立时间、转换时间、转化误差与位数四点;波形数据产生单元的功能主要包括频率设置与输出的显示,以及波形数据的输出。滤波整形处理单元的主要功能是对D/A转换的模拟波进行平滑,对幅度损失与频带损耗进行相应补偿,同时解决杂波和高频干扰问题,最终输出高质量、低误差的波形,以满足实验需求。

4 系统功能单元实现

4.1 波形数据产生单元

该单元是信号源设计的主体,基于FPGA的DDS信号源设计可以实现正弦、三角和方波三种波形数据的产生,根据控制信号还可实现选定波形指定频率的输出。该单元还可分成相位累加器模块、频率控制字生成模块、波形数据ROM表模块。其中,相位累加器模块的主要功能是进行所选波形的相位寻址,设计中为了提高相位累加器的运算速度,相位累加器往往要采用超前进位加法器等方法来实现;频率控制字生成模块可根据输入产生指定频率字,同时显示输入频率数字;波形数据ROM表模块通过地址选择相应波形的数据,存放三种波形的幅值/相位量化值。

系统输入控制运用的是4*4键盘,各键功能为:“确定”键用于波形信号设置的确认;“清零”键可将频率数字快速全部清零;“↑”键用于步进增大控制;“←”键用于修改设置的频率,可以用其执行已输入信号频率数字最后一位的删除命令;“↓”键用于步进减小控制;“0~9”数字键用于设定信号频率。

4.2 D/A转换单元

D/A 转换器的作用是把合成的信号波形数字量转化成模拟量,且波形精度的高低随D/A 转换器分辨率高低变化。在本研究中,信号源技术指标要求输出信号幅值的精度达到0.0625%,一般情况下选择14位分辨率的DAC即可实现该精度目标,但是因为考虑到DAC电路本身产生的误差,本文选择了16位分辨率的高精度AD768AR。

4.3 滤波处理单元

滤波器是一种用来消除干扰杂讯的器件,将输入或输出经过过滤而得到纯净的直流电。DAC输出的信号是模拟的阶梯信号,在其输出频率与Nyquist带宽的高端接近时,采样点数也相应减少,其输出的杂散干扰相应增加。因此,有必要通过滤波器排除干扰,低通滤波器可以有效滤除杂散,所以为了有效降低 DAC 输出模拟信号的噪声,本研究考虑在DAC后加一个低通滤波器。低通滤波器的实现有两种基本方案,一是采用低通芯片LTC1560-1,该方案的优势在于实现简单,缺点是不利于精确滤除除所需信号频谱外的噪声;二是采用数控低通滤波器,该方案的优势在于能够比较准确的滤除除所需信号频谱外的噪声,缺点是结构较更复杂。结合本系统设计需要,本文选择第一种方案。

5 实验验证

由上位机可设置信号源波形为正弦波、矩形波、三角波和锯齿波,且可设置其频率、幅值。实验信号源输出波形如图4所示。

Design of signal source based on FPGA

Xu Hongli

(Hunan College of information,Hunan Changsha,410200)

Based on the condition of rapid development of electronic information technology, the programmable logic device (FPGA) and direct frequency synthesis (DDS) are also constantly updated. At the same time, people also put forward higher requirements on the application conditions in social production and life. Based on this, this text is to reduce the design cost, improve the design quality of the principle, design a DDS based FPGA signal source.

FPGA;DDS;signal source

TN74

A