基于6Gbps速率光纤传输系统设计

2015-11-23王皓奎

唐 宽 王皓奎

(广西瀚特信息产业股份有限公司,广西 桂林 541004)

基于6Gbps速率光纤传输系统设计

唐 宽 王皓奎

(广西瀚特信息产业股份有限公司,广西 桂林 541004)

随着 3G技术的发展以及多模系统的应用,传输带宽要求越来越宽,载波数要求越来越多,这就要求在传输链路上有更高的速率,因此6Gbps速率光纤传输技术要求越来越紧迫,为了实现6G光纤传输技术应用于产品,对6Gbps速率光纤传输技术涉及的并行数据到串行数据转换,数据同步,串行数据收发,时钟恢复等做了测试,设计了FPGA程序并下载到FPGA芯片中进行了验证。实现了高数据速率下光纤的数据互联。

FPGA;串行收发器;光纤传输;误码率

随着3G技术的发展以及多模系统的应用,传输带宽要求越来越宽,载波数要求越来越多,这就要求在传输链路上有更高的速率,因此6Gbps光纤传输技术要求越来越紧迫,为了降低6Gbps光纤传输技术直接在产品中应用所带来的研发风险,迫切需要提前对6Gbps光纤传输技术进行技术研究。据此,本文设计6Gbps光纤传输系统,满足了市面上射频拉远单元在多模系统中的应用,并且可配置性强,便于灵活组网使用。

1 系统总体设计框图

该系统设计了TD-SCDMA多模系统中的GSM近端数字模块和GSM+TD-SCDMA的远端数字模块。近端和远端的FPGA芯片采用支持6Gbps数据传输的单FPGA芯片,这样硬件相对简单,同时也满足了系统要求。

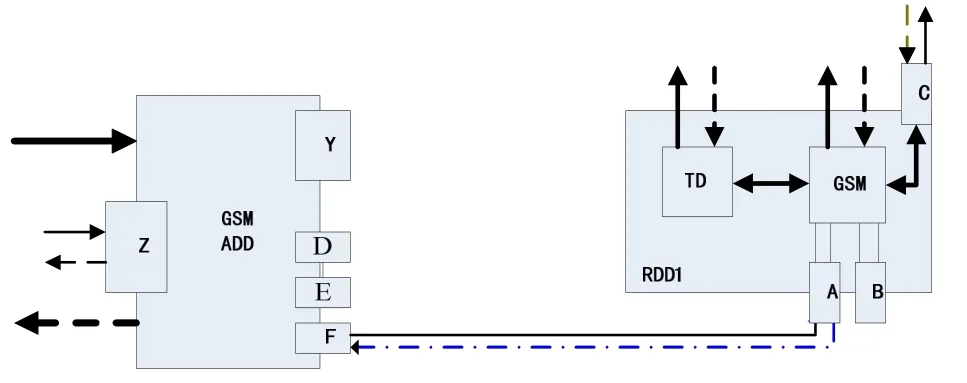

系统总体设计框图如下图1所示:

图1 系统总体设计框图

预计设计系统的工作方式如图 1所示,近端为GSM_ADD,其中,D、E、F为业务光口,功能对等。Y用于近端机之间内部交互光口,用于传递TD、 GSM及WLAN数据。Z为WLAN端口,用于与WLAN专用模块相连。远端机C为WLAN端口。测试只用上图1-1中GSM通道,从近端机输入GSM信号,在远端机射频口输出GSM信号到频谱仪,来验证整个6G光纤传输的可用性。

2 系统回环测试程序设计

系统回环测试是验证测试程序和硬件设备正常的常用方法之一。根据图1所示,可分别在GSM ADD和RDD1设备进行多种系统回环测试,比如GSM ADD自己的光纤发送口直接回环到光纤接收口,也可以使用GSM ADD自己的光纤发送口发送到RDD1的接收口,然后在RDD1中进行数据回环,再通过A口送回到F口的接收端。回环测试框图如图2所示:

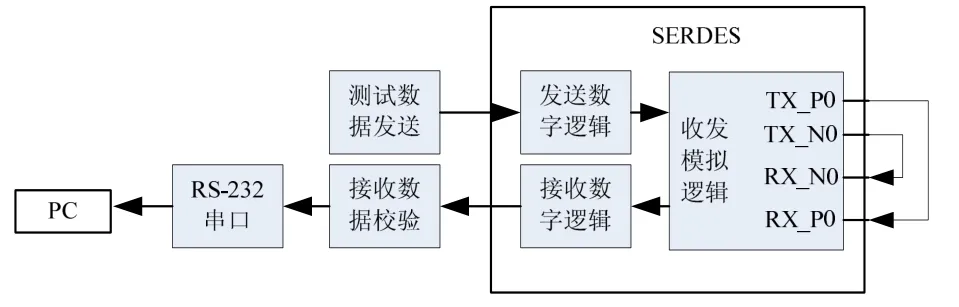

图2 回环测试框图

如上图4所示,首先在FPGA内部编写测试数据发送代码,发送固定格式的测试数据,如K28.5,帧号,1,2,…,255,K28.5,帧号+1,1,2…数据序列,这种数据序列可以防止整帧丢失的情况。通过SERDES的发送逻辑发送到TX差分端,外部采用两根50Ω阻抗线回环到RX差分端,再经过SERDES的接收逻辑解码输出到接收数据校验模块,该检验模块按照发送模块的固定数据序列进行检验,同时把检验结果通过RS-232端口发送到PC机串口上进行打印。

3 光纤传输的实现

该节阐述了6Gbps速率下光纤传输的具体实现过程。

3.1 SERDES接口实现

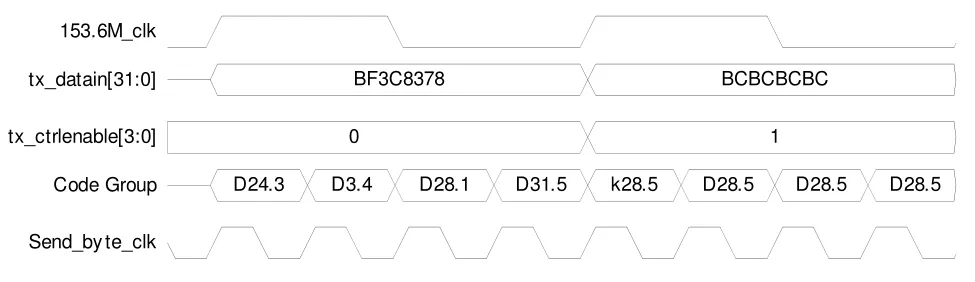

去自SERDES接口包括153.6M的发送时钟,32位宽的数据,4位宽的控制字选择是发送控制字还是数据,同时注意SERDES发送数据是从最低位开始发送的。SERDES接口时序如图3所示。

图3 SERDES接口时序

153.6M的发送时钟由SERDES给出,发送数据与该时钟要对齐。8B/10B编码规则为一个字节的最高3bit为一组,值范围为0~7;其它5bit为一组,值范围为0~31;当对应字节的控制位为低时发送正常数据为DX.Y,当对应字节的控制位为高时发送K码为KX.Y。

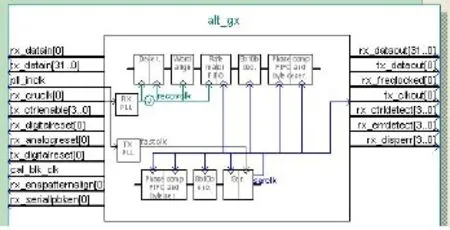

3.2 SERDES硬核对外接口

用altera的MegaWizard产生的6G SERDES硬核如图4所示,由于Arria II GX这一类器件目前还不支持6G速率,所以在这选用了Stratix II GX这一类器件才能在deserializer宽度上选择32位。

图4 SERDES硬核对外接口

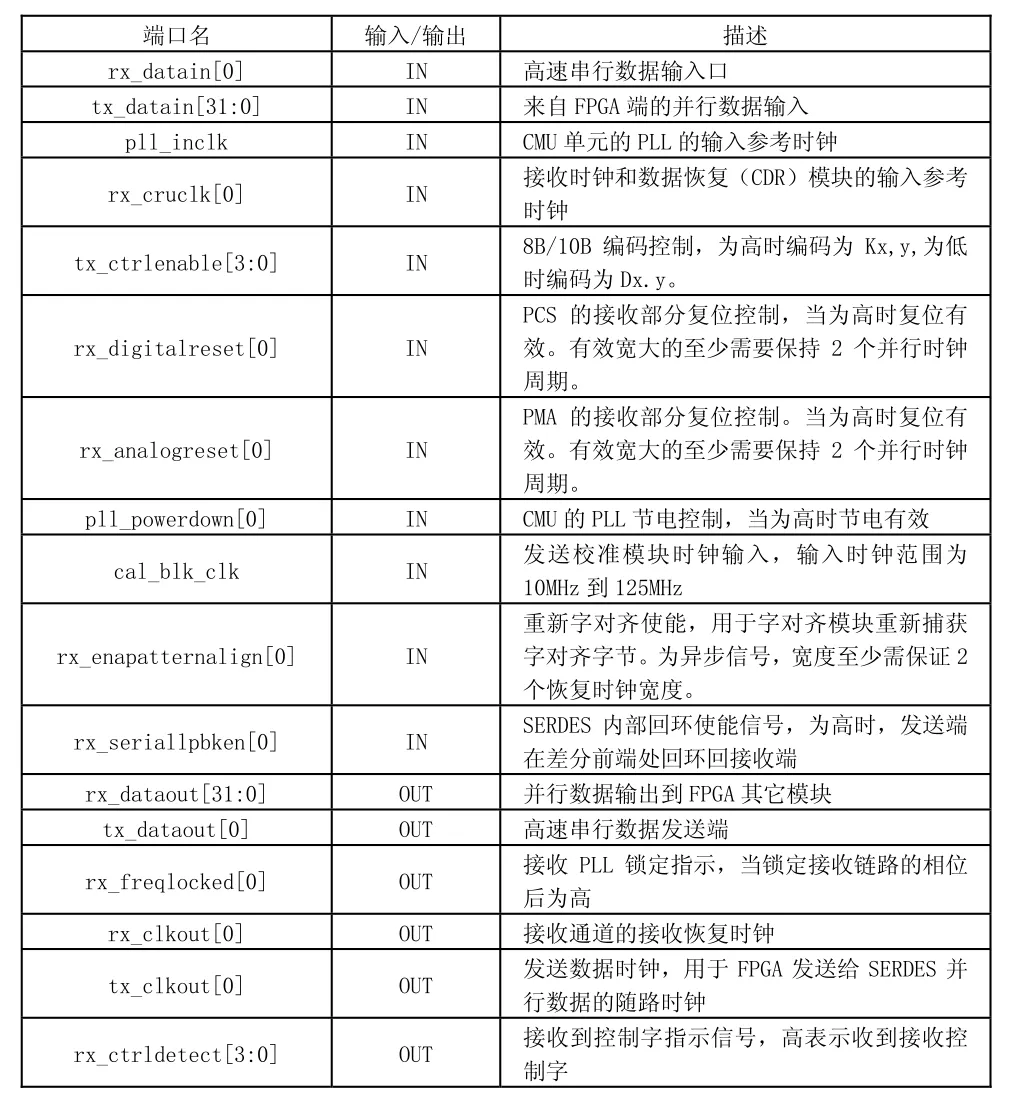

SERDES 硬核对外接口详细端口定义如表1 所示。

表1 SERDES硬核详细端口定义

3.3 6Gbps传输测试框图仿真

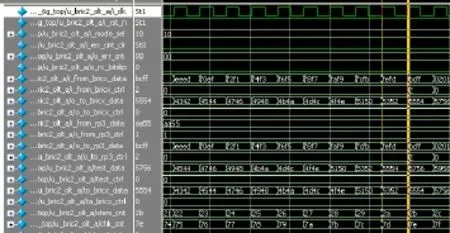

用对于图2所示框图搭建modelsim仿真平台,对FPGA代码和6G serdes进行仿真,仿真结果如图5所示。

图5 SERDES硬核对外接口

在图5中,FPGA收发时钟为307.2MHz,给到SERDES的参考时钟也是为307.2MHz,其中i_from_bricx_data为收到来自 SERDES的 16bit数据,i_from_bricx_ctrl为收到来自SERDES的 2bit控制信号指示,o_to_bricx_data为发送到SERDES的16bit数据,o_to_bricx_ctrl为发送到SERDES的2bit控制信号指示。o_err_cnt为校验结果错误计数器。由上图可知,代码按照预定的发送数据格式进行发送数据,同时SERDES接收到的数据也是与发送数据相同,仿真正确。

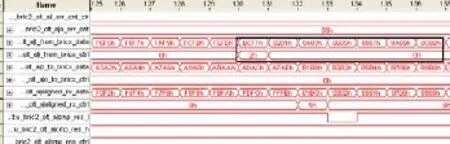

3.4 6Gbps传输数据发送

如图6所示,图6中的o_to_bricx_data为16位发送数据到SERDES,o_to_bricx_ctrl为2位发送控制到SERDES,从图 6中发送的数据可以看出,发送数据满足方案中测试数据格式。

图6 测试数据发送

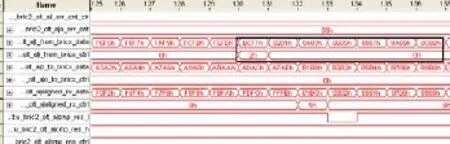

3.5 6Gbps传输数据接收

如下图7所示,图7中的i_from_bricx_data为16位接收数据来自 SERDES,i_from_bricx_ctrl为 2位接收控制来自SERDES,通过与发送数据对应的接收数据进行比较,可以看出接收数据正确。 而K码出现的在高字节,发送K码是固定出现在低字节的,所以,程序里面需要做K码自动调整。

图7 SERDES硬核对外接口

3.6 6Gbps传输数据误码测试

在对接收数据进行位置调整后,与发送数据进行比较,如出现不匹配,则误码计数器o_err_cnt会加1,从图6中和图7中可以看出误码计数器一直保持了0,即没有误码。同时,对误码计数器o_err_cnt作为触发条件,对主近端接收的数据进行校验,对系统进行了 145分钟测试,没有校验到一个误码。

根据误码计算公式,1RT=1(6X109*145*60)=1.9e-14,即误码率小于e-14量级。

4 结束语

本文阐述了一种新型的6Gbps速率光纤传输系统设计方法。该系统已经应用到TD-SCDMA和GSM多模RRU系统中。系统在应用了6Gbps速率光纤传输系统,射频拉远数在原来基础上提高 1倍。设计好的代码作为程序模块可以方便的移植到多种应用平台上,一定程度上降低了开发的难度,为大系统程序提供了更为方便的接口,也在很大程度上提高了光纤传输的效率。

[1] 苏翼凯.高速光纤传输系统[M].上海:上海交通大学出版社,2009.

[2] 毛幼菊,朱继光.光纤通信新技术[M].重庆:光通信研究所,2004.

[3] 徐晓庚.高速光纤通信系统传输特征的研究[D].武汉:华中科技大学,2006.

[4] 夏宇文.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2005.

[5] 陈玮玮.高速光纤通信系统中码型技术的研究[D].南京:南京邮电大学,2005.

Design of 6Gbps data rate fiber transmission system

With the development of 3GPP technology research and development, the 2G technology GSM and the TD-SCDMA combine system are research and development. the transmission baud rate want more and more, the carrier numbers want more and more. So in transmit link should have high data rate, use fiber as transmission media, the limitations is the parallel data translate to serial data, data synchronization, serial data receive and transmit, clock recover, in this paper write the FPGA code and download to the FPGA chip ,research the upwards technology, and test all the parameter. Get the highest data rate in fiber interconnecting result.

FPGA; SERDES; fiber transmit; bit error rate

TP393

A

1008-1151(2015)02-0010-03

2015-01-13

唐宽(1983-),男,广西全州人,供职于广西瀚特信息产业股份有限公司;王皓奎(1974-),男,广西桂林人,供职于广西瀚特信息产业股份有限公司。