基于FPGA的SDRAM控制器

2015-10-24惠为君

惠为君

摘要:介绍了SDRAM的结构、原理和时序。在此基础上,基于FPGA实现了SDRAM控制器设计,给出了设计的代码结构。在MODELSIM平台上完成了设计的仿真。结果表明,该设计是成功的。

关键词:SDRAM; VERILOG; FPGA; 控制器

中图分类号:TN911 文献标识码: A 文章编号:1009-3044(2015)05-0241-03

The SDRAM Controller Based of FPGA

HUI Wei-jun

(Yan Cheng Institute of Technology, Yancheng 224051, China)

Abstract: The structure, principle and time sequence of SDRAM are introduced in this paper. Based on this, the design of SDRAM controller based on FPGA is realized, the code structure of the design is given as well as. The simulation of the design is completed on the MODELSIM platform. The results shows that the design is successful.

Key words: SDRAM; VERILOG; FPGA ; Controller

SDRAM即同步动态随机存储器,其价格低、容量大、体积小,是计算机系统的主要组成部分。在实时图像采集处理系统中,考虑到成本性能等因素,主要用SDRAM作为存储设备。SDRAM的控制逻辑复杂,对于不同的存储要求,为了充分利用SDRAM的性能,有必要设计专用的控制器。

1 SDRAM的结构

SDRAM内部是若干个存储阵列,这样就比较容易做到顺序访问和随机访问。

这样的一个阵列叫一个L_BANK。一般的SDRAM芯片取4个这样的L_BANK.。访问存储单元的步骤是:先访问L_BANK,再访问行,最后访问列。以本文使用的hynix的

HY56V641260为例,其行地址12BIT,列地址8BIT,存储单元的宽度为16BIT,L_BANK数为4。HY56V641260的容量为4* 1M * 16BIT。

2 SDRAM的引脚

主要的控制引脚决定了SDRAM的主要操作,这对设计SDRAM的控制器十分重要。如表1所示,为SDRAM引脚名称及引脚组合决定的功能。其中,CS#-为片选信号,RAS#为行选通,CAS#为列选通,WE#写信号。以上信号都是低电平有效,它们的不同组合实现SDRAM的不同功能 。在读写的时候,WE#为低为写,为高位读。

功能号表示为:1、无操作;2、选定行;3和4、选定列(同时读/写);5、突发传输终止;6、预充电;7、刷新;8、模式寄存器加载。

3 SDRAM的时序

SDRAM的时序分为初始化时序和读写时序,时序的不同阶段对应SDRAM的不同操作。

如图2所示,初始化分四个阶段:200us的输入稳定期,4个L-BANK预充电(操作6),8个刷新周期(操作7),模式寄存器加载(操作8)。 其中模式寄存器加载确定SDRAM的读写工作方式。

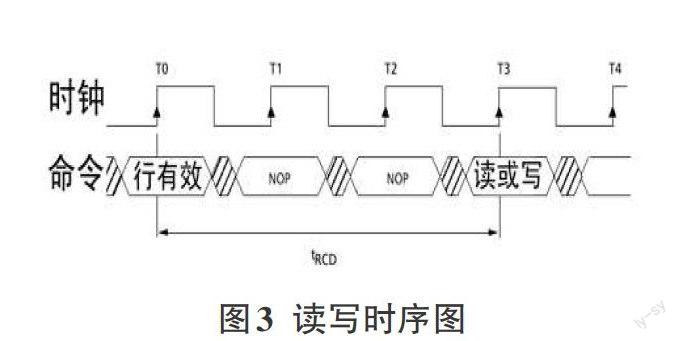

如图3为读写时序图,首先选定行(操作2),过时间tRCD以后,就可以读/写操作(操作4)了,当然,其时要选定列,同时使行无效。

由上述时序可以得到,SDRAM控制器主要控制SDRAM实现以下动作:

a. 200us的稳定期,执行空操作。

b. 所以BANK预充电

c. 8个刷新周期

d. 寄存器模式加载

e. 正常读写

4 SDRAM控制器的Verilog实现

根据时序,控制器的实现部分主要就分为初始化和读写部分。

If (RESET_N==0) begin

SA <= 0; //地址线

BA <= 0; //段地址

CS_N <= 1; //片选

RAS_N <= 1; //行选通

CAS_N <= 1; //列选通

WE_N <= 1; //写使能

CKE <= 0; end //时钟使能。

以上控制信号除了CKE都是低电平有效,所以复位后,控制信号都取高电平,等待初始化指令。接受到初始化指令后,行列都不选通,写使能取高电平,此时初始化开始。

系统时钟取125MHZ,初始化时序的四个阶段,由计数器计数控制。第一个阶段为250us的稳定期,对应的计数值为25000,第二个阶段为预充电阶段,需要20个时钟周期,第三个阶段为8个刷新周期对,每个刷新周期为20个时钟周期,最后对应的就是寄存器模式加载。

#define INT_INT_PER 18d25000

if (init_counter < (INIT_PER+201))

init_counter <= init_counter + 16d1;

else if (init_counter < INIT_PER)

begin

REFRESH <=0;

PRECHARGE <=0;

LOAD_MODE <=0;

INIT_REQ <=1; //200us稳定期

end

else if(init_counter == (INIT_PER+20)) //20个时钟周期的预充电

begin

REFRESH <=0;

PRECHARGE <=1;

LOAD_MODE <=0;

INIT_REQ <=0;

end

else if( (init_counter=(INIT_PER+40)) || ….)

begin

REFRESH <=1;

PRECHARGE <=0;

LOAD_MODE <=0;

INIT_REQ <=0;

end

else if(init_counter == (INIT_PER+200)) begin

REFRESH <=0;

PRECHARGE <=0;

LOAD_MODE <=1;

INIT_REQ <=0;

end

INIT_REQ取值为1表示200us稳定期,PRECHARGE取值为1表示预充电,余类推。模式寄存器加载成功之后,就可以对SDRAM进行读写操作。

If ((READA == 1) & (do_reada == 0)) begin

do_reada <= 1;

ex_read <= 1;

end else

do_reada <= 0;

end

在收到读取的命令之后,首先行选通,使行选通脉冲取值为0,列选通脉冲取值为1。

If (do_reada == 1 | do_writea == 1) begin RAS_N <= 0;

CAS_N <= 1;

WE_N <= 1; end

行选通到列选通之间,需要一定的时间延迟,这个时间称为行选通周期,一般用t_RCD表示。不同厂家的SDRAM,行选通周期取值不同,一般取2到3个时钟周期。

If (RESET_N == 0)begin

rw_shift <= 0;

do_rw <= 0; end

else if ((do_reada == 1) | (do_writea == 1)) begin

if (t_RCD == 3)

rw_shift <= 2; end

else begin

rw_shift <= (rw_shift>>1);

do_rw <= rw_shift[0];

end

用移位寄存器的移位动作实现延时,当读写动作标记do_rw的值由0跳变到1时候,说明延时完成,可以进行读写动作。

If (do_rw==1) begin RAS_N <= 1;

CAS_N <= 0;

WE_N <= rw_flag; end

行选通脉冲取高电平,同时列选通脉冲取低电平,此时进行读写动作。 具体读或者写动作由读写标记寄存器rw_flag标记。此时,如果是读取数据的话,经过一个数据潜伏期CL,数据将出现在数据总线上。

5 仿真

SDRAM的型号取hynix的hy57v641620,其结构是分为4个BANK, 每个BANK取12BIT的行地址,8BIT的列地址,容量是1M*16BIT。仿真的时候,取编码是11的BANK,CKE为高电平,CSN为低电平。同时需要设计一个仿真数据文件,为SDRAM提供写入的数据。

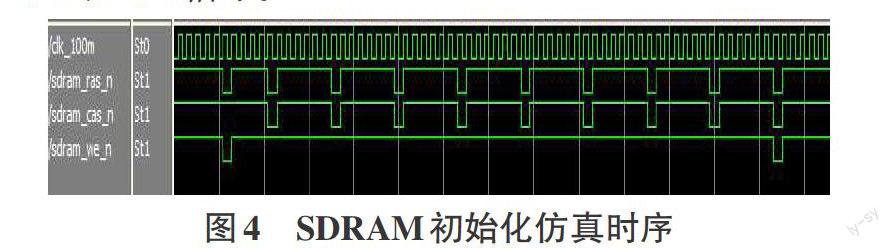

初始化仿真时序如图-4所示。为了简单起见,截图是去除了CKE和CSN信号。

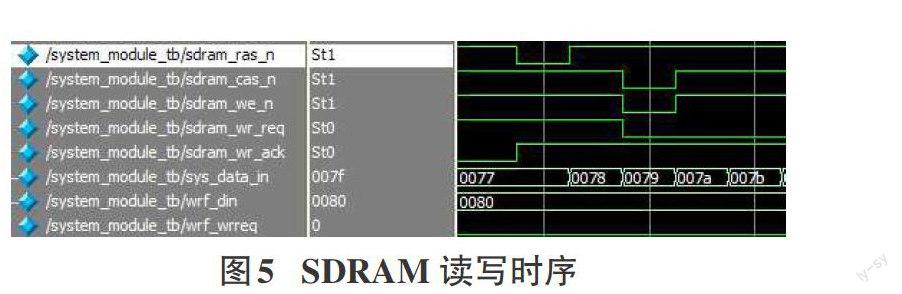

如图-5为读写时序。在模式寄存器加载之后,进入到SDRAM读写时序。由时序图可知,先选定行,行选择信号为低,然后选择列,列现在信号为低,同时WE_N信号有效。此时,写入数据。

6 结束语

该控制器的设计是用于控制SDRAM存储CMOS摄像头实时采集的图像。在实际应用中,还需要设计读写缓存器,用于暂存摄像头的数据流。SDARM的数据来源于读写缓存器,此时,读写缓存器取代仿真时所用的数据文件。

参考文献:

[1] 段然, 樊晓桠. 基于状态机的SDRAM 控制器的设计与实现[J].计算机工程与应用,2005, 42(17) : 110-112.

[2] 夏宇闻. Verilog 数字系统设计教程[M]. 北京航空航天大学出版社, 2008.

[3] 朱文斌,刘春平,黄振.基于FPGA 的高可靠性SDRAM 控制器设计与实现[J]. 电讯技术,2011,51(10) : 113-116。

[4] 赵欣博,陈星.DDR SDRAM 与 FPGA 的高速接口设计[J].电子测量技术, 2008,31(11):182-183.