基于FPGA的TPC编译码器设计与实现

2015-10-17李超

李 超

(中国电子科技集团公司第20研究所 通信部,陕西 西安 710068)

基于FPGA的TPC编译码器设计与实现

李 超

(中国电子科技集团公司第20研究所 通信部,陕西 西安 710068)

介绍了Turbo乘积码(TPC)的编译码原理,并对TPC码字结构进行了分析。在高斯信道下给出了子码为扩展汉明码(64,57,4)的TPC码的误码率性能,并对编译码器的模块设计进行说明,同时采用Altera公司的EP2S180芯片完成了方案验证。结果表明,在系统时钟为100 MHz的情况下,译码时延约为44 μs,可较好地满足实时性需求。

Turbo乘积码;迭代译码;FPGA实现

信道编码广泛应用于各种通信系统,通过增加效验信息,它可以有效降低有扰信道对信息序列所产生的干扰。1993年Berrou提出了Turbo码,这是一种误码性能极为接近香农限的好码。1994年P.Ryndian等人在乘积码的基础上,将线性分组码的迭代软译码理论引入Chase算法中,从而形成了Turbo乘积码[1]。TPC码具有良好的纠错性能,具有译码处理时延小、不存在错误平层以及编码后数据不需要再进行交织等优点[2],因此TPC码已广泛应用于卫星通信、光纤通信等领域,是目前纠错码领域的研究热点。

1 TPC编译码原理

1.1 TPC编码

由于Turbo乘积码中选用子码类型的不同,其又可分为Reed Solomon乘积码和BCH乘积码两类。通过采用不同长度与类型的子码进行编码,TPC码可轻易地构造出具有不同码率和纠错能力的编码矩阵[3],完成编码后的TPC矩阵如图1所示。

编码过程:(1)构造一个k1×k2的矩阵,并将待编码信息依次填入其中。(2)用(n2,k2)系统分组码对矩阵每行进行编码,其中n2和k2分别代表码字长度和信息字长度,从而完成行编码。(3)用(n1,k1)系统分组码对矩阵每列进行编码,从而完成列编码得到TPC码的编码矩阵。

图1 完成编码后的TPC矩阵

1.2 TPC迭代译码

作为一种低复杂度软判决译码算法,ChaseⅡ算法可得到近似的最大似然译码结果[4]。其基本原理是根据接收序列的软信息找出可靠度最低的码元,并只考虑dn/2个错误位置,然后由译码器产生2(dn/2)个测试图样并进行代数译码,最后根据译码后结果和接收序列间的欧式距离,得到最优的判决结果[5]。ChaseⅡ译码算法是行译码和列译码的核心算法,TPC码采用行列交替独立译码的工作模式,同时译码后生成外信息在行列译码过程中进行传递以完成迭代处理。ChaseⅡ译码算法步骤如下:

(1)接收信号判决。对接收序列R进行硬判决得到序列Z,根据绝对值大小赋予一个置信值,其中符号的置信度大小由绝对值决定。

(2)生成测试图样Tq。从接收序列中挑选p个可靠度最小的位置,并将可靠性最小位置表示为1,其余表示为0,该序列称为错误样本E,由错误样本E经排列组合可生成测试图样Tq。

(3)构造试探序列。将测试图样Tq与接收序列Z按位异或生成一组新的试探序列Zq。

(4)生成接收候选码字集。对试探序列Zq进行代数译码得到输出码字Cq,并将其加入到候选码字集合Ω中。

(5)挑选最优判决码字。计算集合Ω中所有候选序列与接收信号R之间的欧式距离,判决码字D为其中欧式距离最小的码字。

ChaseⅡ译码算法外信息的计算:作为最大似然译码的一种次优算法[6],若要找到更好的判决码字D,必须扩大竞争码字C的搜索范围。然而随着不可靠位码字个数p的增加,会导致候选码字Cq数量呈指数增长,这在工程实现中难以实现。

外信息wj为

(1)

迭代译码的结构框图如图2所示,图中[R]为接收向量矩阵,[α(m)]为每次迭代的权重系数,[W(m)]为译码输出的软信息矩阵,[R(m)]为译码输入的软信息矩阵。

[R(m)]的计算如下

[R(m)]=[R]+α(m)[W(m)]

(2)

[W(m)]矩阵的wj为软输出值减去软输入值,其计算如下

(3)

图2 迭代译码结构框图

2 性能仿真

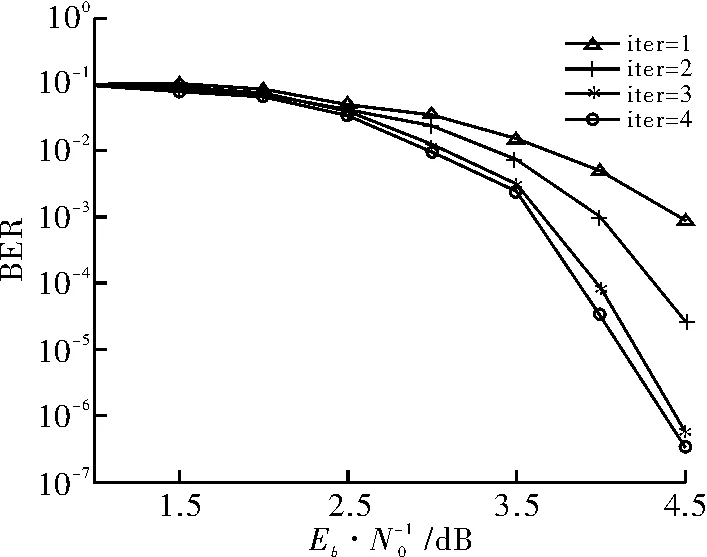

仿真采用扩展汉明码(64,57,4)作为TPC的子码进行仿真,TPC的编码效率为0.793,AWGN信道,BPSK调制。仿真在Matlab环境下进行,不同迭代次数的误码率曲线如图3所示。

图3 不同迭代次数的误码率曲线

从图中可看出,随着迭代次数的增加,误码率性能不断得到提高。但由于选用的TPC码率较高,所以继续增加迭代次数对译码性能的改善会越来越小[7],同时增加迭代次数会导致译码时延增大。当迭代次数为4次时,Eb/N0=4.5dB时误码率可达10-6。

3 硬件实现

为减少硬件资源的使用,同时降低译码器处理时延,译码器接收数据采用了6bit量化的软信息,译码迭代次数为4次。编译码器实现的原理框图如图4所示。在编码工作状态下,未编码数据首先全部写入缓存FIFO中,随后编码控制模块控制读出FIFO数据进行行编码并存入下级缓存RAM,由控制模块计算RAM读地址用来完成行列交织功能,最后将数据送入列编码模块完成整个编码流程。在译码工作状态下,量化后的译码输入数据存入缓存FIFO中,数据接收完毕后译码控制模块控制读出FIFO数据进行列译码,同时将输入的软信息存入RAM中,列译码后的外部信息存入RAM中等待行译码器调用。为减少时延同时兼顾逻辑资源的使用规模,列译码器中一共设置了8个单码字译码器,采用半并行译码方式处理[8]。行译码器工作流程与列译码器工作流程一致,继续完成行译码后一次迭代译码流程结束,最后由译码控制模块确定是否完成迭代。当完成4次迭代后,硬判决模块将软信息进行硬判决并存放于输出缓存FIFO中,从而完成整个译码流程。

行列译码器工作流程基本一致,均采用ChaseⅡ译码算法,这也是译码器的核心模块。其中主要模块包括接收信号判决、生成测试图样、构造试探序列、生成候选码字、挑选最优判决码字、计算外部信息等模块。由于子码采用扩展汉明码(64,57,4),所以接收信号判决模块是将输入的64个量化软数据取绝对值以找到置信度最低的两个。生成测试图样模块和构造试探序列模块是将置信度最低的两个数分别取0和1,共产生4组测试图样,同时将测试图样与经过硬判决的接收序列异或操作,从而生成共4组试探序列。生成候选码字模块也叫代数译码模块,根据扩展汉明码(64,57,4)译码规则进行代数译码。挑选最优判决码字模块主要是进行最小欧式距离计算,具有最小欧式距离的序列就是判决码字。计算外部信息模块主要用来计算译码后的外部信息,外部信息被存入RAM中待下次迭代译码调用。

图4 TPC编译码器原理框图

在Quartus9.0环境下,采用Altera公司StratixII系列的EP2S180F1020I4芯片进行TPC编译码的程序设计与硬件实现,资源占用情况如表1所示。

表1 编译码模块占用资源表

通过编译报告可看出,编码模块最高时钟速率为300MHz,译码模块最高时钟速率为137MHz。本设计系统时钟采用100MHz,编码时延约为28μs,迭代4次的译码时延约为44μs。

4 结束语

本文从TPC码的编码结构与译码算法上进行了理论分析与研究,给出了高斯信道下子码为扩展汉明码(64,57,4)的TPC码误码率性能,同时采用Altera公司的EP2S180芯片进行了硬件实现。

[1]PyndiahRM.Near-optimumdecodingofproductcodes:blockturbocodes[J].IEEETransactionsonCommunications,1998,46(8):1003-1010.

[2]BerrouC,GlavieuxA.Nearoptimumerrorcorrectingcodinganddecoding:turbo-codes[J].IEEETransactionsonCommunications,1996,44(10):1261-1271.

[3] 张申如,邓晓燕.性能接近Turbo卷积码的Turbo三维乘积码[J].电波科学学报,2002,17(6):666-669.

[4] 罗霞,王晓波,孙甲琦,等.Turbo乘积码编译码算法研究[J].飞行器测控学报,2006,25(6):27-30.

[5] 董政,巩克现,葛临东,等.低复杂度和低译码时延TPC迭代译码算法[J].四川大学学报,2012,44(2):122-129.

[6] 何业军,朱光喜,刘文明,等.基于Turbo乘积码的MIMO-OFDM系统在IMT2000信道下的性能研究[J].通信学报,2005,26(8):107-112.

[7] 何业军,朱光喜,张碧军,等.Turbo乘积码与空时分组码的结合研究[J].华中科技大学学报:自然科学版,2005(5):33-35.

[8] 卢磊.TPC编译码的技术研究及其实现[D].哈尔滨:哈尔滨工业大学,2011.

Design and Realization of TPC Coding Based on FPGA

LI Chao

(Communications Division,20th Research Institute of CETC,Xi’an 710068,China)

This paper introduces the principle of encoding and decoding on Turbo Product Code (TPC),and analyzes the structure of TPC coding.Taking Sub-code (64,57,4) extended Hamming code in Gauss channel,this paper presents the performance of signal to noise ratio,and introduces the design of the module for TPC coding.Finally the Altera EP2S180 chip is used to verify the scheme.Results show that when the system clock is 100 MHz,the decoding delay is approximately 44 μs,which can meet the requirement of real-timeness.

turbo product code;iterative decoding;FPGA realization

2015- 03- 13

李超(1983—),男,硕士,工程师。研究方向:通信与信号处理。E-mail:27314437@qq.com

10.16180/j.cnki.issn1007-7820.2015.05.035

TN911.22

A

1007-7820(2015)05-121-03