Pin-cap和NDW对延迟计算精度的影响

2015-10-17庞征斌

孙 旭,庞征斌,黎 渊

(1.国防科学技术大学 计算机学院,湖南 长沙 410073;2.国防科技大学 并行与分布式计算重点实验室,湖南 长沙 410073)

Pin-cap和NDW对延迟计算精度的影响

孙 旭1,庞征斌2,黎 渊1

(1.国防科学技术大学 计算机学院,湖南 长沙 410073;2.国防科技大学 并行与分布式计算重点实验室,湖南 长沙 410073)

由于仿真工具本身及外部一些因素的限制,在特征化时序库时不可能产生出与理想器件完全一致的时序库延时计算模型。为了建立更为精确的延时计算模型,cadence将多输入引脚电容模型与规范化驱动波形的概念引入到有效电流源模型。文中通过使用时序分析工具对时序库进行关键路径仿真,并将分析结果与Spectre仿真结果进行对比,研究在ECSM中标准单元的接收端建立多输入引脚电容模型所带来的时序差异,以及NDW对延迟计算精度的影响。研究表明,ECSM库若同时结合pin-cap与NDW的使用,将会更有利于延迟的精确计算,从而得到更为实际的时序分析结果。

有效电流源模型;引脚电容模型;规范化的驱动波形;等价波模型

研究基于Cadence公司的ECSM时序库,在SMIC公司65 nm以下的某个工艺节点下运用Cadence公司相关后端设计与仿真工具(EDI,ETS,Spectre)进行。其中EDI用于布局布线和RC抽取,ETS用于时序分析,Spectre用来做路径仿真。

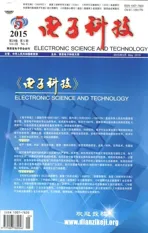

Lib视图是利用Spice网表和器件模型,通过外部仿真器进行晶体管级仿真所产生的一种延时计算模型[1-2]。为验证时序库的精确度,通常需要用ETS工具对其进行时序分析,并将分析结果与基于Spice网表的路径仿真结果进行对比[1],来分析时序库的精度和时序分析工具的性能。将ETS的时序报告与Spectre延迟报告的差值用百分比表示,理想的结果是二者的差值为0%。差值越大,说明时序库精度越低。整个过程称为Timing Correlation或Timing QA。ECSM 模型进行Timing Correlation的精度一般会限制在3%以内[2]。ETS工具内置有对电路关键路径进行Timing Correlation的功能,具体流程如图1所示。

图1 时序库分析流程

1 pin-cap对延迟精度的影响

在基于参数的时序库模型中,输出电容值是输入信号斜率和输出负载的函数,该模型比传统的仅基于输入的模型拥有更高的精度[3]。基于参数的pin-cap在时序库中的定义如图2所示。其中一个ecsm_capacitance称为pin-cap 模型,pin-cap中的threshold_pct值根据pin-cap的数量在特征化时序库进行单元表征时指定[4]。pin-cap越多,ECSM 对capacitance的模拟越精细,分析的结果也越准确,当然pin-cap不可以无穷多,它需要根据实际情况,由工艺、电压、温度(PVT)等因素共同确定。

图2 时序库中pin-cap的定义

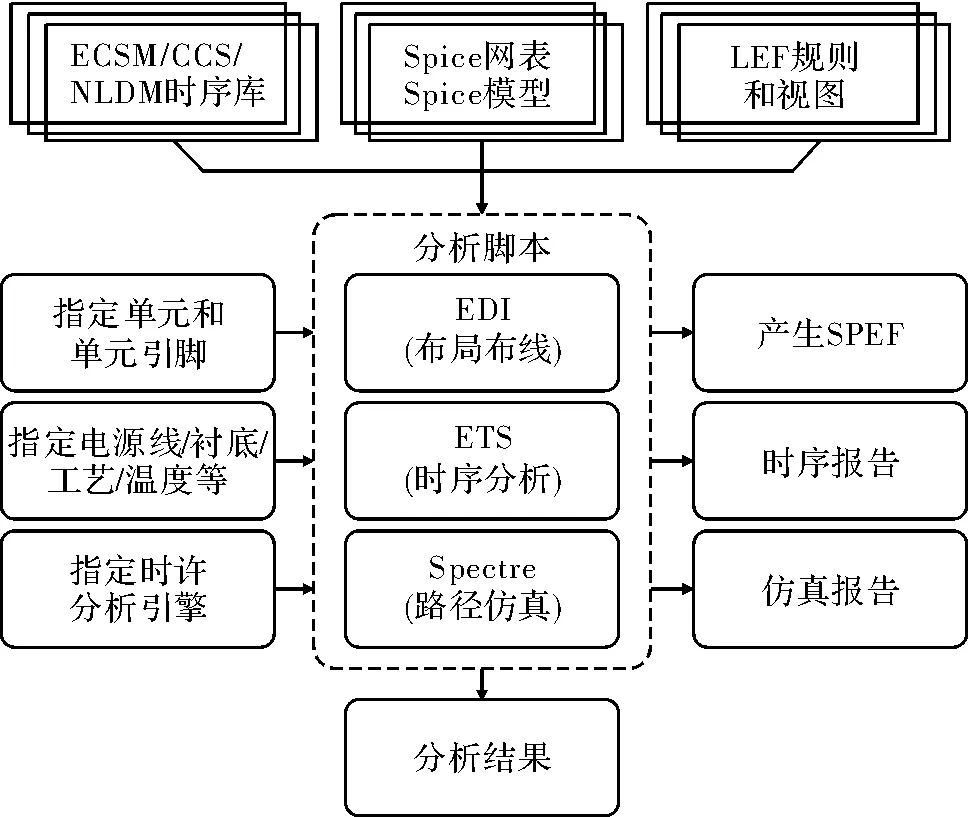

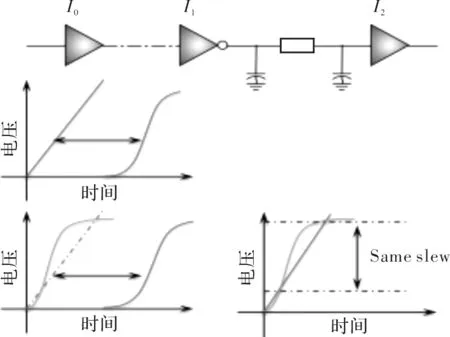

1.1 3pin-cap模型的波形传递

对于40 nm/28 nm及以下工艺,3个pin-cap模型的ECSM库在接收端捕获米勒效应所产生波形时缺乏灵活性,从而导致其延迟计算结果与真实值之间存在较大差异[5]。如图3所示,反相器I1的接受端ETS仿真波形因3pin-cap ECSM模型的不灵活而发生畸变,这种畸变通过反相器的相对放大,在其驱动端体现为与Spice的仿真结果存在较大偏差,这会对路径的时延分析带来较大影响。

图3 3pin-cap模型波形传递

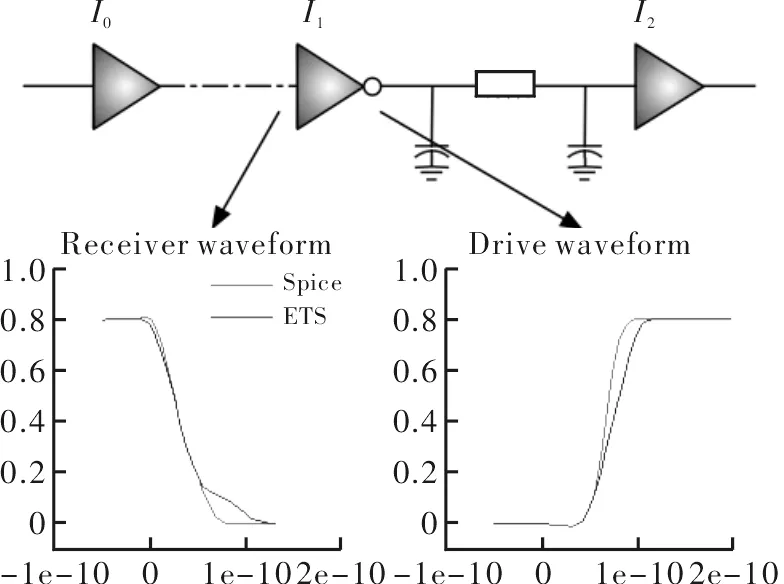

1.2 8pin-cap模型的波形传递

如图4所示,8 pin-cap的ECSM模型的时序仿真波形与spice相比,差异较小。这主要得益于ECSM对输入端电容更为精细化的模拟[6]。从3个pin-cap增大到8个pin-cap,ECSM对单元延时的模拟更加灵活,延迟计算工具在进行延迟计算时可以根据实际电路的RC参数,更准确地选择对应的pin-cap模型进行延迟模拟。

图4 8pin-cap模型波形传递

1.3 8pin-cap库与3pin-cap库仿真对比

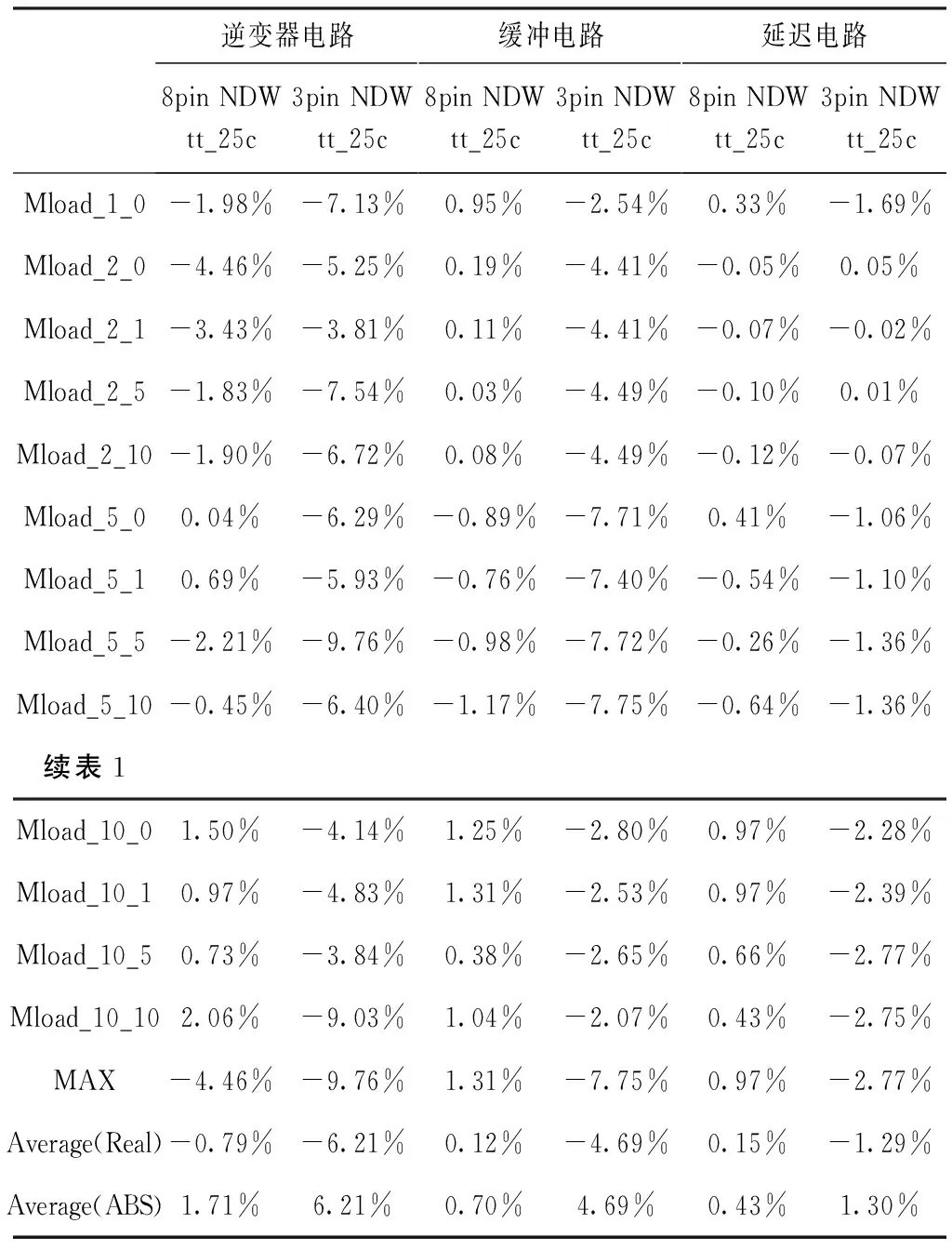

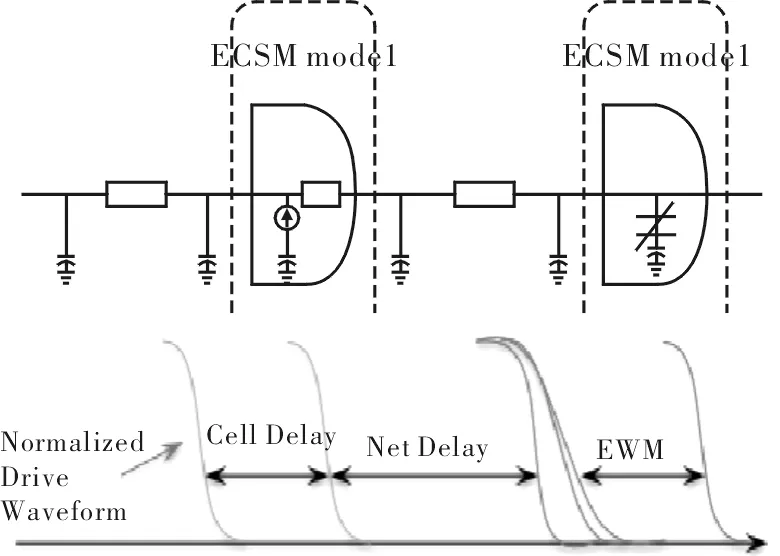

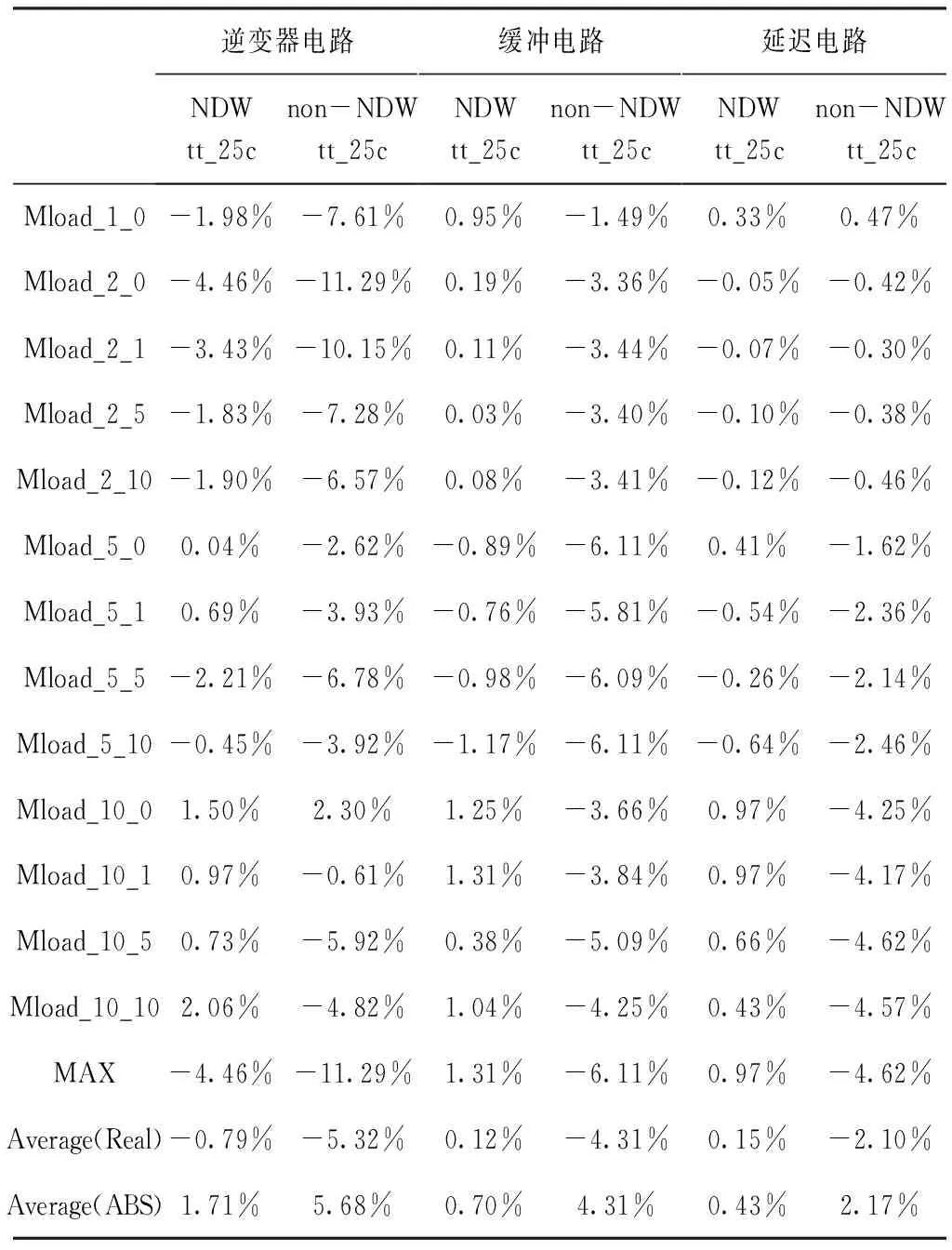

表1是分别用ETS和Spectre工具对8pin-cap和3pin-cap ECSM库进行timing correlation的分析结果。表中数据均以Spectre仿真结果作为基准,将静态时序分析结果与之做比对,若结果为正,说明ETS仿真延时>Spectre仿真延时;反之,则说明ETS仿真延时 表1给出了TT 端脚,T=25 ℃,V=0.95 V条件下,3种典型电路的Timing Correlation结果。从表中可以看出,对于3种典型电路,8pin-cap-NDW的ECSM库都具有更好时序分析结果,其ETS和Spectre的仿真结果之间的延时差值基本都控制在±3%以内。且8pin-cap最差的Correlation结果均远低于3pin-cap。 表1 3种电路Timing Correlation 结果(TT,T=25 ℃,V=0.95 V) 为说明3pin-cap和8pin-cap对延时计算的差异,以Buffer电路为例,将其Correlation波形用曲线图直观的展现出来,如图5所示。 图5 Buffer Cell Mload电路的Correlation波形(TT,T=25 ℃,V=0.95 V) 传统的延迟计算工具根据信号的输入斜率和输出负载来计算延迟[6],然而,随着工艺的不断进步,这种方法已难以满足先进工艺对计算精度的需求。 波形对延迟的影响系数很大。传统意义上,延迟计算工具都是在单元的输入端加载一个具有特定斜率的规范化驱动波形来计算单元输出端的响应,如图6所示。当实际电路中驱动器的驱动特征与特征化时序库单元的输入波形不一致时,这种方法就有可能会引起功能性错误。这是因为不同的波形很有可能具有相同的斜率,而延时精度是输入波形的函数。因此,即使波形的斜率相同,不同的波形也可能会计算出不同的延迟值。 图6 传统的延时计算方法 2.1 预驱动波型对波型传递的影响 如图7所示,以预驱动单元BUFX16和BUFX2特征化出来的两个库为例。设二者波形不同,但具有相同的输入斜率,将BUFX16作为预驱动单元的库,所有被BUFX16驱动的门的延时精度将明显高于其他驱动单元所驱动的门的延时。在此例中,实例I4的延时计算更为精确,因其由BUFX16驱动,输入波形与预驱动波形一致。而其他单元则因实际驱动单元的输入波形与预驱动单元波形不一致,从而对延时产生较大的影响。 图7 预驱动波型对波型传递的影响 为提高延迟计算精度,有必要将波形及其传递作为延迟计算的一个考虑因素。如图8所示,等价波模型(Equivalent Waveform Model,EWM)根据各接收端的输入波形来计算等价响应,并调节互联线延迟[7]。这种调节补偿了下一级因没有真实的波形信息而引起不精确的延迟计算。如果将Spectre的仿真延迟作为参考基准,那么EWM能够在很大程度上缩小与之相比的延迟误差。 图8 规范化的驱动波型对波型传递的影响 等价波形传递(Equivalent Waveform Propagation,EWP)是在每个单元的输入端存储实际波形而不是波形的斜率,这就使得实际波形能够在路径上传递,并用于后一级时序分析,从而解决上述问题。EWP在EWM的基础上进一步提高了延迟的计算精度,在28 nm及更先进的工艺中,时序库中定义的NDW对EWM/EWP来说是其先决条件。因此预驱动单元的选取以及NDW的精度直接决定着EWM/EWP对时序的好坏。 2.2 NDW库与非NDW库的时序仿真结果比对 通过表格来总体上了解二者的差异。温度为25 ℃时,TT 端脚下的3种典型电路结构的Correlation结果如表2所示。以Buffer电路为例,带有NDW的 ECSM库的Correlation绝对均值为0.70%,最差Correlation结果出现在mload_10_1节点,其值为1.31%。而不带NDW库的绝对均值则为4.31%,最大Correlation值则高达-6.11%。二者的差值显著,这也说明NDW对时序的影响较大。 表2 NDW与non-NDW的ECSM库correlation结果(TT,T=25 ℃,V=0.95 V) 图9为Buffer电路结构的Correlation结果分布图。可以看出,不带NDW的库具有明显的设计缺陷。无论何种电路结构,其Correlation都远不如带有NDW的库。 图9 Buffer Cell Mload电路Correlation波形(TT,T=25 ℃,V=0.95 V) 从分析可知,ECSM 库若同时结合NDW与pin-cap的使用,将会更有利于延迟的精确计算,从而得到更为实际的时序分析结果。推荐使用8个以上的pin-cap。其中,至少要有3个pin-cap分别代表上升/下降斜率的高/低门限值,以及延迟计算测量点(50%)。其余5个pin-cap值则需要能够精确反应驱动波形。因此,建议在ECSM 时序库中同时引入规范化的驱动波形和多个输入引脚电容模型。 [1] Christoph Knoth,Veit B Kleeberger,Petra Nordholz,et al.Fast and waveform independent characterization of current source models[C].Behavioral Modeling and Simulation Workshop (BMAS),IEEE,2009:90-95. [2] Amit Goel,Sarma Vrudhula.Current source based standard cell model for accurate signal integrity and timing analysis[C].Design,Automation and Test in Europe,2008:574-579. [3] Cadence.Spice correlation made easy by encounter timing system [EB/OL].(2012-10-10)[2014-10-22]http://community.cadence.com/cadence_blogs_8/b/di/archive. [4] Peter Feldman,Soroush Abbaspour,Debjit Sinha,et al.Driver Waveform computation for timing analysis with multiple voltage threshold driver models[C].Design Automation Conference (DAC),45th ACM/IEEE,2008:425-428. [5] Cadence.Effective current source model[EB/OL].(2008-07-12)[2014-10-22]http://www.cadence.com/Alliances/languages/Pages/ecsm.aspx. [6] Amin C,Kashyap C,Menezes N,et al.A multi-port current source model for multiple-input switching effects in CMOS library cells[C].In DAC,43rd ACM/IEEE,2006:247-252. [7] Li P,Feng Z,Acar E.Characterizing multistage nonlinear drivers and variability for accurate timing and noise analysis[J].IEEE Transactions on VLSI Systems,2007,15(11):1205-1214. Effects of Pin-cap and NDW on Delay Calculation Precision SUN Xu1,PANG Zhengbin2,LI Yuan1 (1.School of Computer science,National University of Defense Technology,Changsha 410073,China;2.Key Laboratory of Parallel and Distributed Computing,National University of Defense Technology,Changsha 410073,China) Due to the constraints from the simulation tool and some external factors,it is impossible to create a liberty delay calculation model which is fully consistent with the actual device when characterizing timing library.In order to build a more accurate delay calculation model,the concept of Multiple Input Pin Cap Model (pin-cap) and normalized driver waveform (NDW) is introduced into the Effective Current Source Model (ECSM) by Cadence.This paper is intended to study the difference between timing correlation results caused by the multiple input pin-cap model and the NDW in ECSM,by means of performing accurate comparison of STA timing results with Spice path based simulation.Research shows that the ECSM library,if combined with pin-cap and NDW,will be more conducive to the accurate calculation of delay,thus getting more credible timing analysis results. ECSM;pin-cap model;NDW;EWM 2014- 10- 23 国家高技术研究发展计划基金资助项目(863计划)(2013AA014301) 孙旭(1988—),男,硕士研究生。研究方向:数字集成电路。E-mail:bigbengua@icloud.com。庞征斌(1972—),男,研究员。研究方向:计算机系统结构和高性能结点机。黎渊(1984—),男,研究员。研究方向:FPGA的硬件加速系统,芯片验证技术。 10.16180/j.cnki.issn1007-7820.2015.05.002 TN A

2 NDW对延迟精度的影响

3 结束语