基于FPGA实现的PCI-I2S接口转换电路

2015-10-17王丹宇孙万蓉魏雪松

王丹宇,孙万蓉,成 龙,魏雪松

(西安电子科技大学 电子工程学院,陕西 西安 710071)

基于FPGA实现的PCI-I2S接口转换电路

王丹宇,孙万蓉,成 龙,魏雪松

(西安电子科技大学 电子工程学院,陕西 西安 710071)

提出了一种基于FPGA实现的PCI-I2S音频系统方法。通过在FPGA中将PCI软核、FIFO以及设计的接口电路等相结合,在FPGA上实现了PCI、I2C、I2S等多种总线,并且结合音频解码器实现了不同采样频率语音数据的传输以及播放功能。系统充分利用FPGA的片上资源及其可编程特性,减少了硬件电路的复杂度。

PCI总线;FPGA;I2S;音频

I2S总线是一种用于音频设备间传输数据的串行总线标准,该总线采用独立的时钟线与数据线,避免了时差诱发的失真。随着多媒体的广泛应用,该总线已被应用于越来越多的数字系统中。

PCI总线是一种高性能的32/64位局部总线,理论最大传输速率可达132 Mbit·s-1,可支持多组外设,已经被各类主流处理器做为总线标注,是目前应用最广泛的外围总线。如今大部分处理器并没有集成I2S接口,但在嵌入式系统中CPU经常使用PCI总线与外围设备进行交互,故需设计一种PCI-I2S接口转换电路,从而实现CPU与外围音频设备进行通信。目前实现此种接口转换电路主要通过PCI接口芯片与音频接口芯片等专用集成电路芯片在板级电路进行组合从而实现基于PCI的音频播放设备。此种电路虽然成熟可靠,但电路设计复杂、灵活性小而且需要占用大量的电路板空间[1]。

随着数字通信技术的发展,由于FPGA的灵活性与其较短的开发周期,在接口电路设计中的应用已经越来越广泛。本文提出一种使用FPGA实现PIC-I2S的接口转换电路,不仅可以避免使用协议转换芯片,节省电路板上的空间,而且还大幅加强了系统的灵活性,方便维护升级。

1 系统的硬件设计

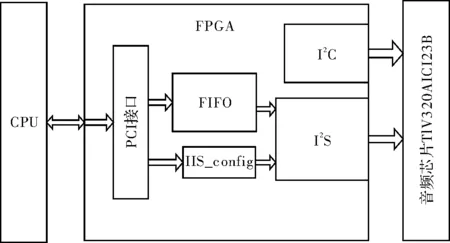

音频播放系统主要由立体声音频编解码器TLV320AIC23B,FPGA器件XC6SLX75以及处理器PowerPC8270组成。系统框图如图1所示,CPU将原始音频数据通过PCI总线传至FPGA后以每组数据16 bit的格式串行传输至音频芯片TLV320AIC23B,并由音频芯片将数字量转换为模拟音频信号输出。FPGA实现PCI接口功能和对音频编解码芯片的配置与数据传输功能,其内部主要由PCI协议接口,I2S协议接口,I2S配置寄存器,I2C协议接口以及FIFO存储器等组成。

图1 系统框图

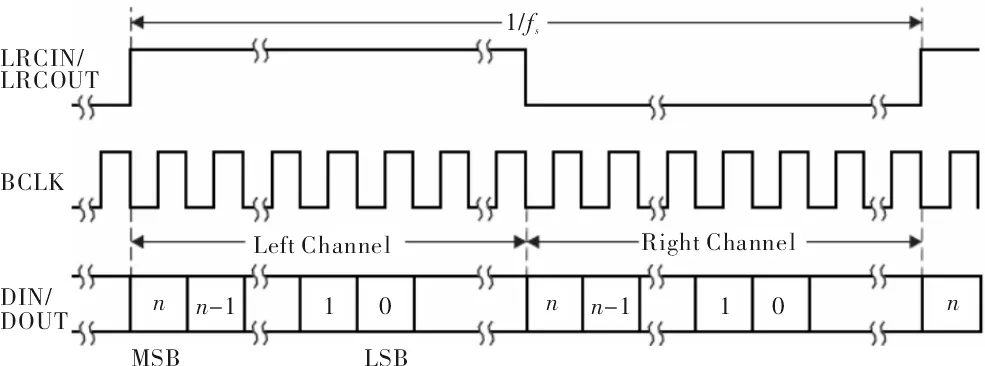

TLV320AIC23B在系统中实现数字音频信息到音频模拟量的转换,在系统上电工作时,首先需要通过I2C接口配置它的多个控制寄存器,此后芯片将根据位传输时钟(Bclk)与左右声道控制时钟(LRCIN),按控制寄存器中配置的方式采集由FPGA发送来的音频数据。接收到的数据将传至芯片内部进行数模转换、滤波等处理。

FPGA根据I2S协议规范与芯片要求,由主时钟(MCLK)分频产生位传输时钟(Bclk)与左右声道控制时钟(LRCIN),与音频数据同步发送至TLV320AIC23B。其中左右声道控制时钟(LRCIN)应与音频数据的原始采样级别频率相同,根据I2S的协议规范及芯片资料,其位传输时钟(Bclk)与芯片的主时钟(MCLK)如下

BCLK=Sampling Size×Sampling Rate

(1)

MCLK=Sampling Size×Sampling Rate×384

(2)

式中,Sampling Rate为原始采样级别频率;Sampling Size为采样大小。

系统中,TLV320AIC23B芯片采用左对齐的接口模式,其时序如图2所示,其中LRCIN为高电平时音频的左声道选通,为低时音频的右声道选通。在LRCIN的一个周期内,左右声道上传输同一组数据[2]。由于PCI总线的传输速度远高于I2S总线的传输速度,为不使CPU过高频率的响应中断,所以在FPGA中生成一个FIFO,可使得PCI总线可以连续传入大量数据。此外,由于不同的音频文件有着不同的采样级别频率,而通常音频文件的采样频率为16 kHz或32 kHz,故在FPGA中生成I2S_config寄存器,可以通过PCI总线设置此寄存器以调用FPGA中不同的数字时钟管理(DCM),从而为TLV320AIC23B芯片提供不同的时钟。

图2 I2S传输时序

2 PCI接口设计

PCI协议比较复杂,它不仅有严格的同步时序要求,而且需要许多的配置寄存器,因此实现电路也比较复杂。通常情况下,在FPGA中实现PCI接口通常有3种方式[3]:(1)用FPGA自行设计PCI接口,该方法可根据需要有选择地实现PCI接口功能,更贴近系统需要,而且可以降低系统成本,但需要开发者对PCI协议有着深刻的了解,且在外部环境恶劣时,不容易满足系统的稳定性要求,开发难度较大。(2)利用PCI硬核来对系统进行开发,PCI硬核即是嵌入在FPGA内部的固化电路,类似于专用的PCI接口芯片,设计者只需完成信号链接与验证即可,但此方法中,PCI硬核已经固化在FPGA中,影响了系统的灵活性。(3)利用PCI软核进行开发,PCI软核可以根据用户自身的需要进行配置,更为灵活,贴近用户系统,且其已经过设计厂商的验证,可靠性高。本文采用Mentor公司提供的开源软核MPCI32用于FPGA上PCI接口的开发。

Mentor公司的PCI核完全符合PCI2.2的标准,支持33/66 MHz、32位数据的传输,PCI核的结构如图3所示,该PCI核的功能是将入口测复杂的PCI接口信号转为出口侧较为操作的用户信号[4]。PCI核内用户侧设置有主控制接口和从控制接口以及配置寄存器等模块,其中从控制接口分为寄存器接口与FIFO接口。因为本文中仅使用了从控制接口,所以图中仅对从控制接口的信号展示。可以看出,IP核左侧的信号为PCI的标准信号,在使用时与前端PCI总线连接,右侧信号为本地数据信号,可以看出IP核将PCI上原本复用的地址线与数据线处理后分别接出为32位的地址线与32位数据线,并且原本总线上双向的数据线被区分为单向读信号线与写信号线。此外还有后端逻辑对寄存器的读写地址信号线与PCI访问逻辑的读写地址信号线,后端对寄存器使用时的请求信号线,寄存器被占用的标志信号线等。配置寄存器包含所有PCI配置空间的信息,其中包括表明设备信息的Device ID与Vendor ID寄存器,以及命令寄存器,Base Address Register等主设备初始化时需要访问的信息,这些信息在PCI核生成时已经被设定,无需改动。

在设计PCI接口时,用户通过发起寄存器读写请求tar0_req,去访问后端寄存器,从寄存器交换数据,在CPU检测到都算逻辑未使用寄存器时,可发起占用请求并占用寄存器(tar0_gnt被置位),此时,PCI读写此寄存器中的数据。

图3 PCI IP核结构图

3 音频接口设计

在驱动后端的音频芯片时首先需要通过I2C接口配置音频芯片的控制寄存器,此后根据音频数据不同的采样级别频率控制FPGA产生的时钟,最终音频数据从FPGA内部的FIFO中通过FPGA产生的时钟依据I2S协议标准向音频芯片传输。在FPGA中设计的音频接口包括I2C时序协议接口模块,I2S时钟控制接口模块和I2S时序协议接口模块。

3.1 I2C接口模块的设计

I2C总线是由飞利浦公司开发的串行总线,总线由两根信号线构成,其中SCLK为时钟信号线,SDA为双向数据线。I2C总线上的所有设备均可做为主设备,每个设备在总线上都有唯一的地址[5]。

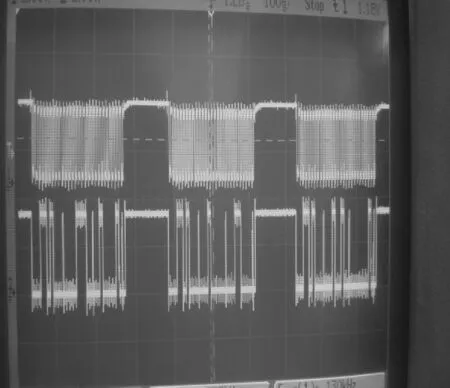

立体声音频编解码器TLV320AIC23B中,共有11个寄存器需要配置,所有寄存器为只写寄存器。这些寄存器分别控制芯片输出音频的左右耳机音量、左右功放音量、芯片电源、采样率等参数。在芯片的配置参数传输时,以I2C的数据线(SDA)在时钟线(SCLK)为高时下降沿条件作为数据的起始位,此后每当FPGA向TLV320AIC23B传输8位数据时,TLV320AIC23B在第9个时钟时通过SDA向FPGA返回一个ACK信号[6]。如果FPGA确认收到ACK信号则继续传输下一组数据,否则将重复传输此组数据。实际中示波器测量的传输波形如图4所示。

图4 I2C实际测量波形

3.2 I2S时钟控制接口模块的设计

由于不同的音频数据有着不同的采样级别频率,所以在传输不同音频文件时,FPGA提供给TLV320AIC23B的时钟频率不同,为使不同采样频率的声音文件都能在本系统上正常播放,故在FPGA内部使用其DCM由主时钟12.288 MHz生成16 kHz和32 kHz两种采样时钟频率,接入缓冲器BUFGMUX中,并且通过在PCI的配置空间中开辟一个寄存器,寄存器的值接至BUFGMUX的选择端,这样通过配置PCI总线配置此寄存器即可根据播放音频的情况选择时钟频率。

3.3 I2S时序协议接口模块的设计

I2S时序接口模块的主时钟由FPGA内部提供,模块内通过对主时钟进行分频产生BCLK与LRCin,模块在每个LRCin的上升沿由缓存FIFO中读取一个16 bit的数据放入临时寄存器,此后在BCLK的每个上升沿依次由高至低读取寄存器中的每一位并赋值给数据线SDIN,并且在LRCIN的下降延时重复传输此数据,从而完成音频数据的I2S协议传输[7]。

4 系统测试及结果

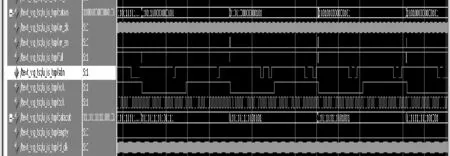

通过在上位机中向CPU内部Flash烧录一段音频数据,此后通过访问FPGA的配置寄存器将此段数据传入至FPGA内64 kB的FIFO中,后端音频模块检测到FIFO非空即开始工作。首选通过逻辑仿真软件对系统进行仿真,结果如图5所示,信号线SDIN、LRclk,BCLK输出结果符合I2S协议规范中左对齐模式。此后可以在音频芯片模拟输出端接入耳机或功放等音频播放设备,用示波器测量其模拟输出。结果证明此系统工作正常,可以按照要求播放16 kbit·s-1与32 kbit·s-1WAV音频文件。通过示波器测量的模拟输出如图6所示,可以看出明显的包络信号。通过以上结论可以看出,系统可以充分利用FPGA片内资源,从而减少对板内面积占用并减低系统功耗,也易于移植入同类的嵌入式系统中[8-9]。

图5 I2S结果仿真图

图6 实际测量音频波形

在本文的基础上,可以进一步发挥FPGA的灵活性,比如在开发FPGA上支持PCI从设备DMA模式,以进一步加强PCI总线的读写效率、I2S总线的右对齐和DSP模式等,并且可以开发语音芯片上的语音采集功能,使系统实现语音采集、转换、传输等功能。

[1] 吴德铭,陆达.高速通信中基于FPGA的PCI总线接口研究与设计[J].计算机应用,2005,11(11):2717-2719.

[2] Texas Instruments.TI TLV320AIC23B-Q1 data manual[M].USA:Texas Instruments,2006.

[3] 麻志鹏,沈小林.PCI总线接口的FPGA设计与实现[J].计算机与数字工程,2011(11):95-99.

[4] Mentor.MPCI32 product specification[M].USA:Mentor,2002.

[5] 林峰,许昕.I2S接口硬件设计与测试 [J].微电子学,2013(3):387-389,394.

[6] 黄俊辉,杨镂玲,凌霄.基于FPGA的I2S IP核设计[J].软件导刊,2013(1):32-34.

[7] 庞维,王剑钢,王朝阳,姜海峰,王明江.基于XC3S1000 FPGA芯片的数字录放音系统的设计[J].重庆邮电大学学报,2007(增刊):69-71.

[8] 史小斌,宋思盛,黄根全.PCI总线从设备接口的CPLD实现[J].电子科技,2011,24(11):59-62.

[9] 李国光,罗丰.一种64位高速PCI总线接口的设计与实现[J].电子科技,2011,24(2):57-59.

Design of a PCI-I2S Interface Conversion Circuit Based on FPGA

WANG Danyu,SUN Wanrong,CHENG Long,WEI Xuesong

(School of Electronic Engineering,Xidian University,Xi’an 710071,China)

We present a design of a PCI-I2S audio system based on FPGA.By combining the PCI soft core,FIFO,and the designed interface circuit in FPGA,we implement such buses as PCI,I2C,and I2S in this FPGA system.We also implement the function of audio date transmission and playing by using the stereo audio codec Tlv320aic23b with FPGA.The system makes full use of the resources on FPGA and its characteristic of reprogrammability to reduce the complexity of the hardware circuit design.

PCI;FPGA;I2S;audio

2014- 10- 16

王丹宇(1990—),男,硕士研究生。研究方向:EDA技术。E-mail:wangdanyu1990@163.com。孙万蓉(1960—),女,教授。研究方向:数据采集与传输技术,图像信号处理。

10.16180/j.cnki.issn1007-7820.2015.05.015

TN79;TP

A