D/A转换在System View环境下的仿真及硬件实现

2015-10-17辜强

辜 强

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室,陕西 西安 710071)

D/A转换在System View环境下的仿真及硬件实现

辜 强

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室,陕西 西安 710071)

针对模拟信号在传输介质中优于数字信号,而设计数模转换模块。首先用System View对DAC模块进了仿真。然后设计的D/A转换的硬件电路。通过设计了一个前置的串并转换电路,不仅可以实现8位并行数字信号的D/A转换,还可实现8位串口输入数字信号的D/A转换。在输出端,接入一个有源二阶低通滤波电路,使模拟输出更为平滑。达到了在实际范围内较低波形衰减的目的。

D/A转换;权电流;串并转换;低通滤波

通信系统分为模拟通信系统和数字通信系统。模拟通信直观且容易实现,但保密性差,尤其是微波通信和有线明线通信,易被窃听。只要收到模拟信号,就容易得到通信内容,抗干扰能力弱,电信号在沿线路的传输过程中会受到外界和通信系统内部的各种噪声干扰,噪声和信号混合后难以分开,从而使通信质量下降。线路越长,噪声积累也就越多。但数字通信系统弥补了模拟通信的缺陷,加强了通信的保密性,提高了抗干扰能力。数字信号在传输过程中会混入杂音,可以利用电子电路构成的门限电压来衡量输入的信号电压,只有达到某一电压幅度,电路才会有输出值,并自动生成一个整齐的脉冲。较小的杂音电压到达时,由于它低于阈值而被过滤掉,不会引起电路动作。因此再生信号与原信号完全相同,除非干扰信号大于原信号才会产生误码。为防止误码,在电路中设置了检验错误和纠正错误的方法,即在出现误码时,可以利用后向信号使对方重发。因而数字传输适用于远距离传输,也能适用于性能较差的线路;数字化通信还可构建综合数字通信网。采用时分交换后,传输和交换统一,可以形成一个综合数字通信网。

D/A转换器(DAC)是将二进制码或BCD码表示的数字量通过D/A转换器转换为模拟量,转换器输出的模拟量与输入二进制码或BCD码成正比,这种转换器的核心是一个电阻网络。

1 基于System View的DAC电路仿真

System View基本属于一个系统级工具平台,可进行包括数字信号处理(DSP)系统、模拟与数字通信系统、信号处理系统和控制系统的仿真分析,并配置了大量图符块(Token)库,用户容易构造出所需的仿真系统,只要调出有关图符块并设置好参数,完成图符块间的连线后运行仿真操作,最终以时域波形、眼图、功率谱、星座图和各类曲线形式给出系统的仿真分析结果。

目前常用的D/A转换器有权电阻网络D/A转换器、倒T型电阻网络D/A转换器、权电流型D/A转换器、权电容型D/A转换器以及开关树型D/A转换器等类型。

2 有源RC低通滤波器

图1 有源滤波总框图

在电路中RC网络起着滤波的作用,滤掉不需要的信号,这样在对波形的选取上起着重要作用,通常主要由电阻和电容组成。电路中运用了同相输入运放,其闭环增益

(1)

同相放大器具有输入阻抗高,输出阻抗低的特点,广泛用于前置放大级。将输出信号的一部分或全部引入输入端称为反馈,其中的电路称为反馈网络,反馈网络分为正、负反馈。

3 方案的选择

(1)关于滤波器类型的选择。当要求带通滤波器的通带较宽时,可用低通滤波器和高通滤波器合成。

(2)级数选择。多级滤波器串接时传输函数总特性的阶数等于各级阶数之和。当要求的带外衰减特性为-mdB每倍频程(或mdB每10倍频程)时,则取级数n应满足n≥m/6(或n≥m/20)。

(3)元器件的选择。一般设计滤波器时都要给定截止频率F(ωc)带内增益Av,以及品质因数Q(二阶低通或高通一般为0.707)。设计时经常出现待确定其值的元件数目多于限制元件取值的参数之数目,因此有许多个元件均可满足给定的要求,这就需要设计者自行选定某些元件值。

ωc2=1/CC1RR1

(2)

Q=0.707

(3)

ωc/Q=1/R1C+1/R2C+(1+Av)/R2C1

(4)

Av=1+R4/R3

(5)

因为通带增益Av=2;截止频率Fh=2 000Hz;Ui=100mV。所以可得Fc=2 000Hz时,取C=0.01μF,由式(2)计算对应的参数K=5,可得Av=5时,取C=C1=0.01μF;K=5时,R1=5.63kΩ,R2=11.8kΩ,R3=R4=33.75kΩ。

4 仿真实验与分析

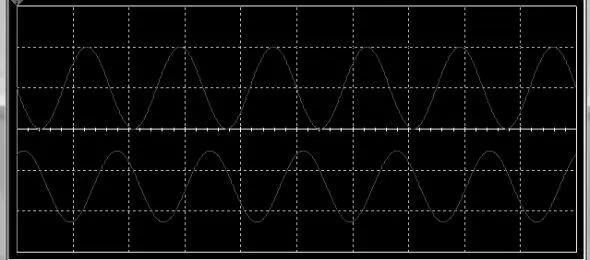

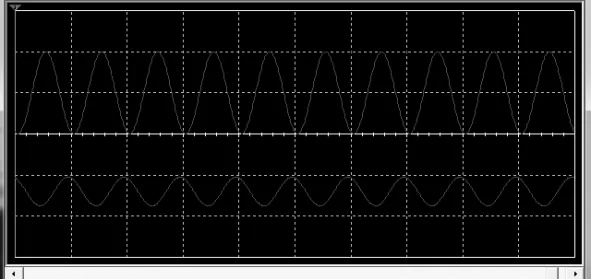

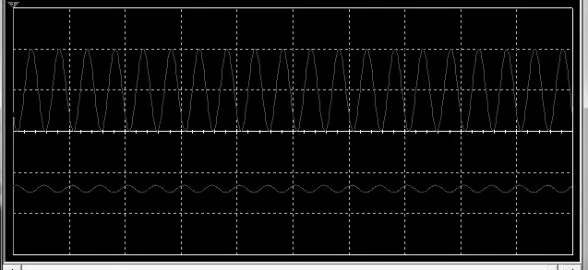

仿真实验如图2~图5所示。

图2 RC滤波波特图

图3 3 kHz输出结果

图4 5 kHz的输出结果图

图5 10 kHz的结果输出

由于阶滤波器电路相对简单,但带外传输系数衰减慢,一般在对带外衰减性要求不高的场合下选用,无限增益多环反馈型滤波器的特性对参数变化比较敏感。当要求带通滤波器的通带较宽时,可用低通滤波器和高通滤波器合成,优于单纯用带通滤波器。滤波器的级数主要根据对带外衰减特殊性的要求来确定。每一阶低通或高通电路可获得-6 dB每倍频程的衰减,每二阶低通或高通电路可获得-12 dB每倍频程的衰减。多级滤波器串接时传输函数总特性的阶数等于各级阶数之和。

[1] 阎石.数字电子技术基础[M].北京:高等教育出版社,1998.

[2] 天津市无线电技术研究所.模数与数模转换技术[M].北京:科学出版社,2009.

[3] 康华光.电子技术基础:数字部分[M].北京:高等教育出版社,2001.

[4] 秦键.一种基于PWM的电压输出DAC电路设计[J].现代电子技术,2004,27(14):81-83.

[5] 刘书明,刘斌.高性能模数与数模转换器件[M].西安:西安电子科技大学出版,2000.

[6]LawrenceJKushner,MarcusTAinswort.Aspuriousreductiontechniqueforhigh—speeddirectdigitalsynthesizers[J].IEEEInternationalFrequencyControlSymposium,1996(2):920-928.

[7] 郑君里,应启珩,杨为理.信号与系统[M].北京:高等教育出版社,2004.

[8] 杨志忠.数字电路[M].北京:高等教育出版社,2004.

[9]WilliamsJ.Componentandmeasurementadvancesensure16-bitDACsettlingtime[S].USA:LinearTechnologyCorpration(AN7419987),1998.

[10]许波,夏玮玮,宋铁成.模拟与数字通信导论[M].北京:电子工业出版社,2007.

Simulation and Hardware Implementation of D/A Conversion in System View Environment

GU Qiang

(Key Laboratory of Electronic Information Countermeasure and Simulation,Xidian University,Xi’an 710071,China)

The analog signal is better than the digital signal in the transmission medium,so a digital to analog converter is designed.System View is used to simulate the DAC module.Then the D/A conversion hardware circuit is designed.A front-end parallel/serial conversion circuit is designed,which makes possible D/A conversion of both 8-bit parallel digital signals and 8-bit serial digital signals.On the output side,an active second-order low-pass filter circuit is included so the analog output is smoother.Lower waveform attenuation within the practical range is achieved.

DAC;power current;series and transforms;low pass filter

2014- 10- 20

辜强(1988—),男,硕士研究生。研究方向:雷达和通信干扰技术。E-mail:408875414@qq.com

10.16180/j.cnki.issn1007-7820.2015.05.013

TN79

A

1007-7820(2015)05-043-03