TDMA突发信号自适应门限检测方法

2015-09-26梁中英张少侃廖世文广州海格通信集团股份有限公司广州510663

梁中英,张少侃,廖世文(广州海格通信集团股份有限公司,广州 510663)

TDMA突发信号自适应门限检测方法

梁中英,张少侃,廖世文

(广州海格通信集团股份有限公司,广州510663)

0 引言

时分多址(TDMA)接入方式是一种常用的卫星通信方式,属于突发的传送模式。在突发通信系统中,信号检测的虚警率和漏检率直接影响解调性能。文献[1]中对比了固定门限和自适应门限检测的优劣,由于接收信号电平是未知和时变的,采用固定门限检测方法,在信号功率发生变化、信噪比较低以及干扰功率发生变化的情况下,都会降低检测性能。这些情况要求采用自适应捕获方法[2]。本文介绍的自适应门限检测方法,不仅可以检测信道是否到达,可以精确到帧头起始位置。

1 自适应门限捕获方法

突发信号的检测方法有时域检测法和频域检测法,其中时域检测法包括短时能量法、短时自相关法、高阶累积量法等;频域检测法包括幅度谱检测法、循环谱相关法等[3]。由于本系统帧结构的设计包括前导序列,专门用于信号检测,所以选择时域检测法,实现简单。

选择适当的前导序列,需要具有尖锐的自相关性[4],对于具有前导的突发信号,通过已知前导序列与AD采样的接收信号进行相关运算,就可以在出现前导的位置检测到峰值,再减去检测的处理时间,得到的就是这帧数据的起始位置。

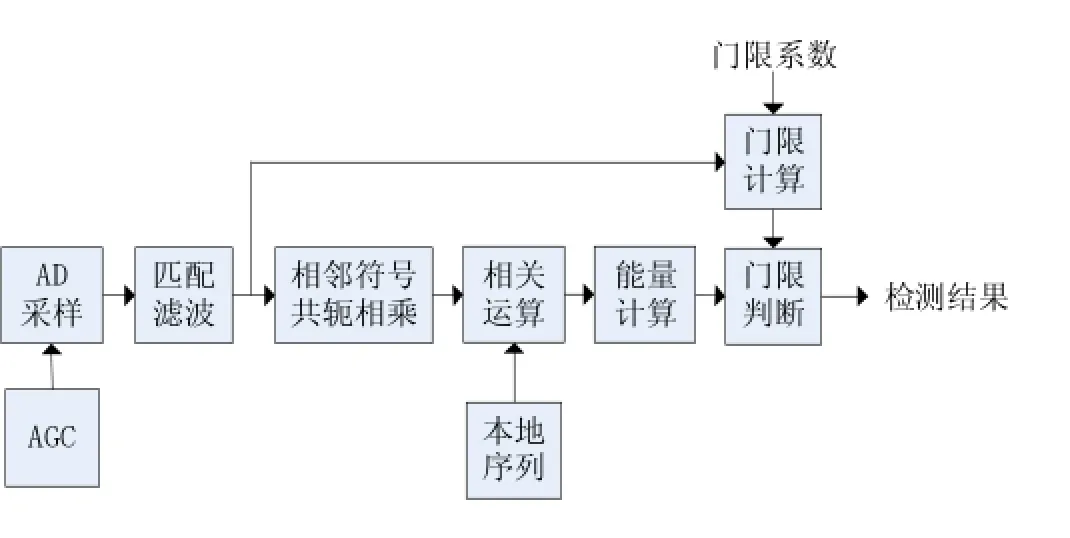

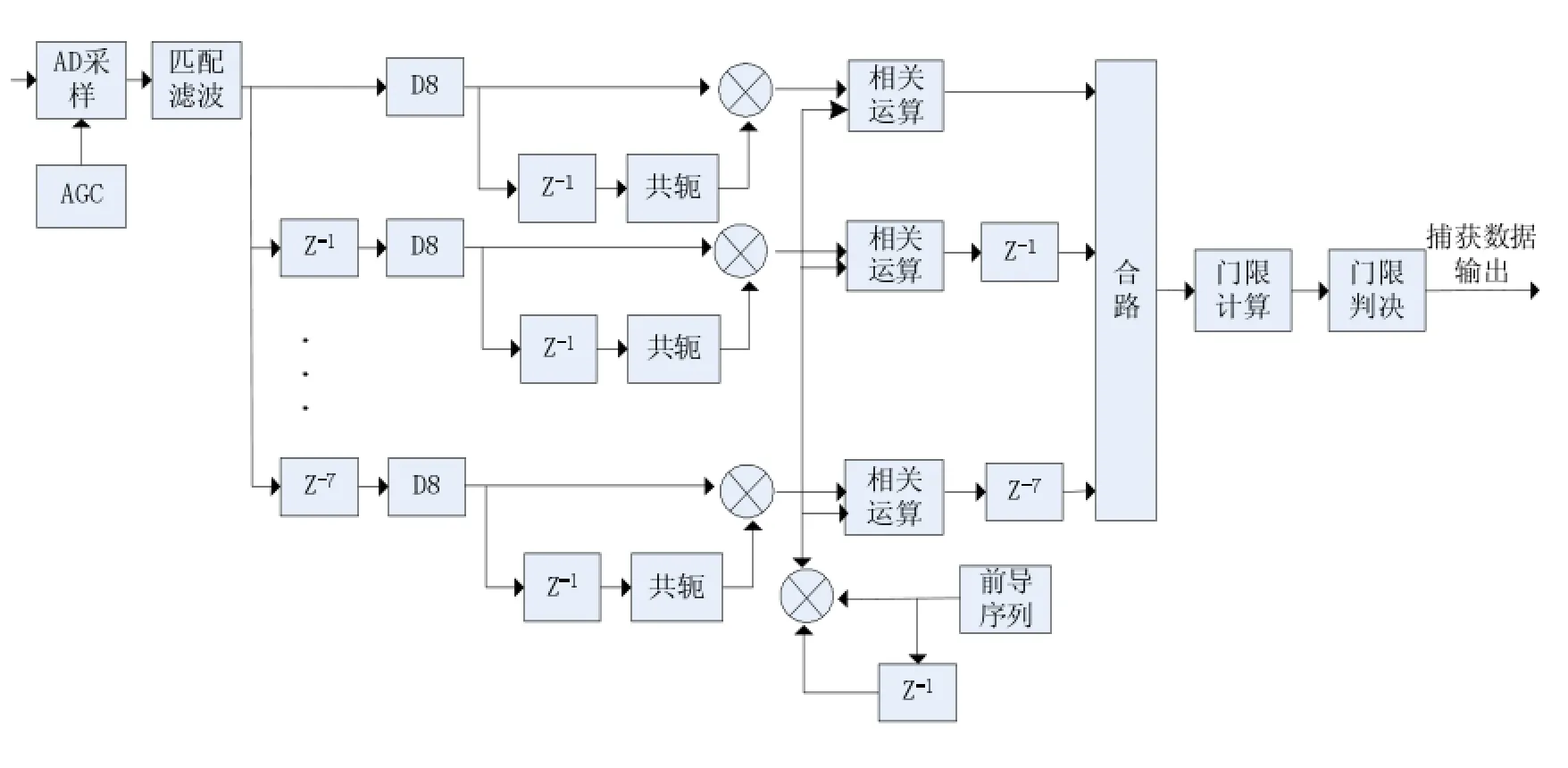

在突发信号捕获之前,需要对AD采样的数据进行自动增益控制(AGC),这一环节至关重要,AGC调整的动态范围对捕获的性能有很大的影响。捕获的处理流程如图1所示。经过匹配滤波后的信号,相邻符号进行共轭相乘,然后与已知的本地序列(同样也是对前导共轭相乘后的结果)做相关运算,再经过门限计算和门限判断,得到捕获的结果。

图1 自适应门限捕获方法处理流程

(1)自动增益控制(AGC)对捕获的影响

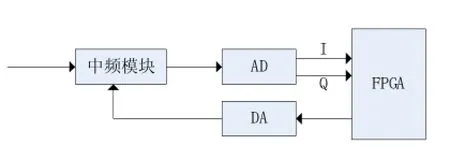

AGC是通过对AD采样信号能量的检测来控制信号输入功率的大小,直到信号能量落入到设置的能量范围内,采用闭环控制,如图2所示。图中AD为采样中频信号的AD芯片,FPGA对AD采样信号进行短时能量计算,根据计算的结果调整控制DA的数据大小,从而调整模拟电压的大小,达到控制中频模块输出的信号幅度的目的[5]。

短时能量能量值与DA输出的模拟电压是相对应的,需要实际测试出信号不溢出并且不会太小以至于捕获门限检测不到的动态范围,这样才能准确地确定自适应捕获门限的参数。换句话说,两者是相辅相成的关系。AGC的动态范围直接影响了捕获门限的动态范围。

图2 AGC控制示意图

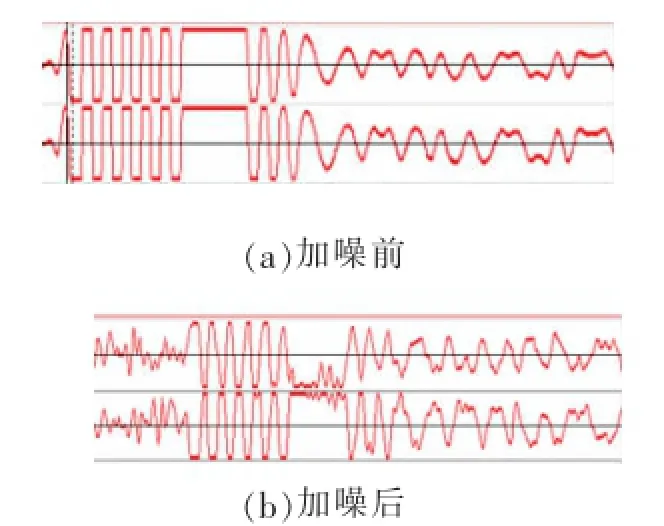

系统中利用64个符号的前导序列进行捕获,对于4M带宽的信号,需要AGC需要在足够短的时间内将接收信号调整到捕获的动态范围内。由于DA的每一次控制都需要时间,一旦AGC控制的速度不够快,就会导致64个符号的前导序列中有一部分数据溢出或过小,在信噪比过低或频偏过大的条件下,就会使捕获的起始值偏移,一旦偏移过大,就会对解调性能造成影响。AGC调整效果图如图3所示。

图3 AGC调整效果图

为了解决AGC对捕获的影响,在开销允许的条件下,可以在前面加一段序列,专门用作AGC。这就需要平衡性能和开销之间的关系。

(2)自适应门限计算及判决方法

信号经过预处理做完相关、合路后开始进行门限计算,设匹配滤波后的信号为R(x),首先对R(x)进行模平方运算,得到单点能量,通过滑动窗法计算窗内能量,每进入一个样点,计算得到一段能量的累加值[6],再乘以一个门限系数,得到自适应门限值Y(x):

由于这个门限的计算需要N个样点才出一个结果,所以需要将相关能量值时延N个clk再与门限比较,如图4所示。

图4 自适应门限计算流程图

门限系数ρ是一个可调参数,根据不同的漏检和虚警需求可仿真获得。

门限的判决方法也是至关重要的,选取不适当,在信噪比低的情况下会造成虚警。本文根据实际系统中遇到的多种虚警的情况,总结出判决条件如下:

(1)判断相关能量值是否超过门限值,一旦出现,则记录该值,如果连续多个相关能量值超过门限,则记录最大值;

(2)这时还不能根据这个值来判定这段数据的起始,从这一时刻开始,继续搜锁一帧的长度,如果又出现(1)的情况,比较当前时刻最大值和前一时刻最大值,判定两者中大的一个为数据的起始依据,直到这一帧长度搜索完毕。

在处理过程中,需要将输入数据缓存,检测到最大峰值后,需要减去处理时间,即可得到帧头的起始位置,为了保证处理的实时性,一旦检测到帧头就假定捕获到了,开始后续处理,当在处理的过程中,如果出现(2)中描述的情况,认定前一个值为虚警,则将其他模块复位,认定帧头为当前时刻,继续后续处理,以此类推,直到一帧结束。经过仿真和实测,增加第(2)个条件后,可以适当的降低门限系数,在大大降低了虚警率的同时,又降低了漏检率。

2 MATLAB仿真结果分析

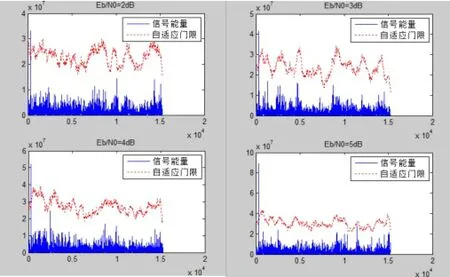

对信号加噪后的仿真结果进行分析,信噪比越低,虚警率和漏检率越高,这时需要对门限系数进行详细的测试和调整来达到一个均衡状态。本系统根据实际卫星通信链路的需求,调整好门限系数值,仿真结果如图5所示。从图中可以看出,Eb/N0值越小,噪声对信号的能量计算影响越大,在帧头处出现的峰值越小。这种情况是固定门限就会很容易出现漏检。

图5 不同信噪比下捕获效果仿真图

当Eb/N0值大的时候容易出现虚警,会有多个超过门限的能量峰值出现,如图6所示。但是如前面章节所述的门限条件判断,在这种情况下,会和前面超过门限的能量峰值做比较,比前面峰值小的位置,都认为不是帧头,所以大大降低了虚警率。

图6 不同信噪比下捕获效果仿真图

漏检概率和虚警概率曲线图如图7所示,在Eb/ N0=2dB的时候,没有漏检且虚警为零,可以满足系统的设计需求。

图7 漏检概率和虚警概率仿真图

3 FPGA硬件实现验证

系统AD采样速率为符号率的8倍,即1个符号8个样点,经过根升余弦匹配滤波后,通过时延,将信号分成8路并进行8倍抽取,分别对这8路信号进行处理,这时每路信号是以符号为单位的。

对每路信号进行相邻符号共轭相乘,接着与已知的前导序列进行相关运算。之所以分为8路进行处理,是因为这样就转化为对符号进行操作,那么此时的相关只需要做加法,即不需要进行乘法运算,在FPGA实现的时候,就可以节省大量的乘法器资源,然后对8路相关结果进行延时合路,进入到门限计算的环节。

按照自适应门限的计算方法计算门限,并根据实测中遇到的各种情况综合考虑后的门限判决条件进行判决,得到突发信号的起始数据位置,完成捕获的操作。

4 结语

本文结合实际工程需求,介绍了突发信号检测的原理和改进的自适应检测方法,进行了MATLAB仿真并对仿真结果进行分析,一定范围内的频偏和相偏对算法的影响较小,且两个门限的限制大大降低了虚警率和漏检率。最终利用FPGA较少的资源,对本算法进行了工程实现,验证了此种方法的可实现性。

图8 FPGA硬件实现框图

[1]刘乃安,曾兴雯,郭峰等.高速突发通信中的自适应门限技术及其性能[J].电子学报,1998,26(1):111-114.

[2]吴玉成,陈宁,高珊.突发通信中的自适应门限信号检测方法[J].电子与信息学报,2007,29(12):2896-2898.

[3]吴晓东,路友荣,黄渊灵等.TDMA突发信号的检测[J].电信技术研究,2005,2:28-33.

[4]张波,郭英,霍文俊等.一种快速的PN码同步捕获方法[J].电子设计工程,2011,19(3):7-9

[5]刘艳.基于FPGA的大动态范围数字AGC的实现[J].电子设计工程,2009,17(8):42-44.

[6]吴玉成,陈婷婷.在滑动窗口中判决的自适应门限检测方法[J].系统仿真学报,2008,10(20):2770-2773.

Burst Signal;Adaptive Threshold;FPGA

Adaptive Threshold Acquisition Method for TDMA Burst Signals

LIANG Zhong-ying,ZHANG Shao-kan,LIAO Shi-wen

(Guangzhou Haige Communications Group Incorporated Company,Guangzhou 510663)

1007-1423(2015)23-0020-04

10.3969/j.issn.1007-1423.2015.23.004

梁中英(1985-),女,黑龙江鹤岗人,硕士研究生,工程师,从事领域为卫星通信数字信号处理领域工作

张少侃(1988-),男,陕西西安人,硕士研究生,助理工程师,从事领域为卫星通信数字信号处理领域工作

廖世文(1985-),男,广西柳州人,硕士研究生,工程师,从事领域为卫星通信数字信号处理领域工作

2015-06-26

2015-07-31

基于提高TDMA突发信号检测性能的目的,对现有的自适应检测方法进行改进,优化相关器且改善门限判决方式,在简化算法的同时降低检测的虚警率和漏检率,给出MATLAB仿真结果。利用Altera公司的CycloneIII系列FPGA对该设计方法进行实现,通过系统测试验证此设计方法的可行。

突发信号;自适应门限;FPGA

发改办高技[2012]2083号

For the purpose of improving TDMA burst signal detection performance,according to existing adaptive detection method,optimizes the correlator and threshold decision method,reduces the false alarm probability and false dismissal probability,and simplifies the algorithm at the same time,shows the result of MATLAB simulation.Realizes the design by CycloneIII FPGA of Altera corporation,and the system experiments illustrate the effectiveness of this design.