基于FPGA的I2C总线应用研究

2015-08-20魏海波马铮刘杰

魏海波,马铮,刘杰

(湖北汽车工业学院电气与信息工程学院,湖北十堰442002)

基于FPGA的I2C总线应用研究

魏海波,马铮,刘杰

(湖北汽车工业学院电气与信息工程学院,湖北十堰442002)

I2C总线作为高性能的串行传输总线,已在微电子领域得到了广泛的应用。本课题中,在EP2C5Q208C8N平台上采用硬件描述语言VHDL,通过Moore型有限状态机编程设计了模数转换器件PCF8591T的I2C总线控制器。实验结果表明:所设计的I2C总线控制器遵循I2C总线接口协议,数据传输稳定可靠。

I2C总线;串行传输总线;有限状态机;硬件描述语言;接口协议

doi:10.3969/j.issn.1008-5483.2015.03.011

I2C总线是Philips公司推出的串行总线,由于结构简单、传输速率高、支持主从及多主工作方式、具备总线仲裁等特点[1],在硬件电路设计中可以大为简化电路复杂程度。诸如TI、ST、Freescale等众多全球知名半导体厂商在其推行的高性能IC芯片中添加了I2C总线接口,以确保其产品的市场份额。现场可编程逻辑门阵列是较为新型的半定制电路产品,利用查找表方式实现组合逻辑,通过相应触发器驱动其它电路,从而完成功能开发。该半定制产品既解决了定制电路功能限定的不足之处,又克服了原有编程器件可用器件偏少的问题[2]。

根据I2C总线电气特性及通讯协议,采用Altera公司高性价比的CycloneII系列EP2C5Q208C8N器件,结合I2C总线数据传输器件PCF8591T,以VH⁃DL语言设计了具体的数据传输模块。

1 I2C总线接口协议

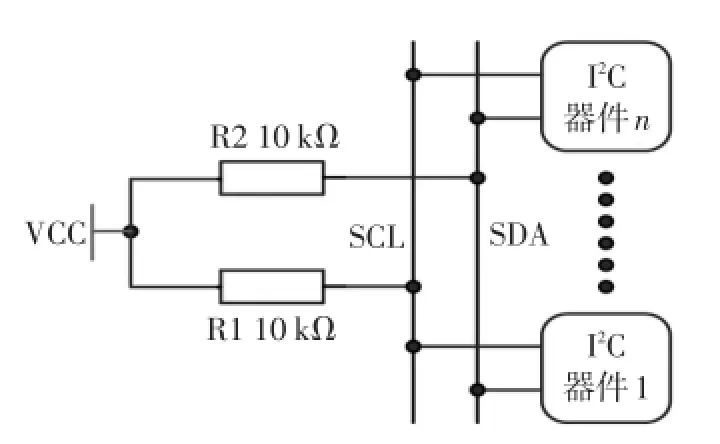

I2C总线采用时钟总线(SCL)和数据总线(SDA)实现数据的双向同步传输。为了衡量I2C总线空闲时的状态定义其逻辑高电平为总线空闲状态,通过监控I2C总线上的SCL和SDA总线状态,就能判定I2C总线的实时状态。通过连接上拉电阻至总线电源电压实现,如图1所示。

图1 I2C总线基本框架图

连接在I2C总线上的每个器件都通过I2C总线接口将各自的SCL和SDA直接挂在总线上。这样,器件之间均构成线“与”关系,任意器件的低电平都会带来该总线的低电平逻辑。

IC总线由主器件发动一帧数据的传输,通常包含起始信号(S)、地址选通控制字信息(ADR_ sel)、应答/非应答信号(ACK)、数据传输字信息(DAT_trans)、结束信号(P)。主器件通过地址选通控制字中的传输方向位信息判断I2C总线的数据传输方向,而选通信号中存在数据传输的方向位信息,大多数情况下同时涉及主器件与从器件之间的双向通信,因此选通信号会产生2次;起始信号、应答/非应答信号、终止信号是决定I2C总线启动停止与数据接受与否的关键要素,必须严格按照总线协议进行。一帧完整的I2C总线信息如图2所示。

图2 I2C总线完整时序

从图2中可以看出,当I2C总线启动后,首先发出一个起始信号S启动总线。总线启动后,在SCL时钟下进行寻址字节的广播信号发送,位于I2C总线上的任意器件都能接收到该字节信息,仅有1个与之完全相同的地址器件才能与之匹配,同时获得数据传输方向提示。在第9个时钟下,从器件响应主控器件,这时通信双方已做好数据收发的准备工作。之后进入正常的数据发送阶段,根据实际情况决定是否终止数据传输,从而产生终止信号P。

2 硬件方案

在具有I2C总线的器件中,通常都配备了地址引脚用于设定器件的I2C总线3位可编程引脚。通过对这些引脚的设定可以产生多达8个相同器件的总线接入。本课题中,采用4通道8位I2C总线数据传输器件PCF8591T作为总线控制对象,利用Al⁃tera公司高性价比FPGA器件EP2C5Q208C8N芯片作为I2C总线主控器件,以有限状态机方式设计了来自外部模拟量的数据采集工作。

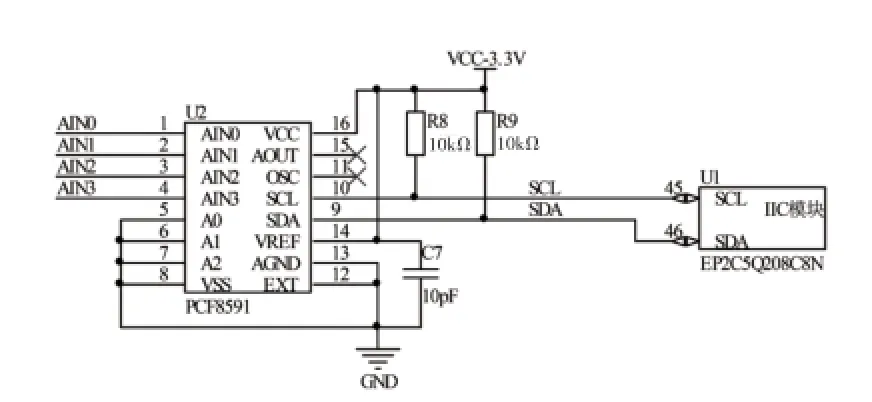

硬件电路原理图如图3所示,A/D转换器件PCF8591T的AIN0~AIN3是来自外部的4组待采集的模拟量数据,A0~A2是该器件的地址选择引脚,直接接地,即后续I2C总线寻址字节中的3位可编程位信息D3~D1,应设置为“000”。该器件的2条 I2C总线SCL和SDA分别通过10kΩ的上拉电阻连接到器件的VCC端,以保证I2C总线空闲期间是逻辑高电平。同时,SCL和SDA直接与FPGA器件的2个通用I/O管脚连接,通过管脚配置为SCL和SDA总线,实现I2C总线数据传输的硬件条件基础。

图3 FPGA的I2C总线数据采集原理图

3 软件设计

3.1I2C总线时钟确定

从I2C总线传输速率来看,其标准模式传输速率位100 kHz,快速模式为400 kHz,高速模式为3.4 MHz。从图2可以看出,I2C总线3个特殊信号的保持时间均应该不小于4.7μs,取近似值5μs,故而选用本课题I2C总线传输速率为200 kHz,这样在一个I2C总线周期里可以完成对这类特殊信号的处理过程。

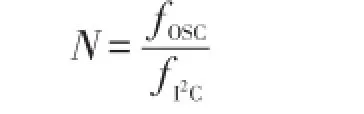

FPGA采用50 MHz的有源晶振,对于I2C总线所需求的200 kHz时钟,可以通过分频程序实现,两者之间的分频系数为

代入已知信息 fOSC为50 MHz,fI2C为200 kHz,计算得分频系数N为250。

3.2I2C总线控制字确定

PCF8591T中,为了实现其功能,除了规定的地址寻址字节外,还设置有额外的控制字,用于控制该器件的工作方式及其它功能[3]。通过查阅产品手册,确定了I2C总线通讯的相关控制字设置,相关说明见表1。

表1 PCF8591T I2C总线通讯控制字设置

PCF8591T器件中只有2个通信相关寄存器:地址字寄存器和控制字寄存器。当该器件启动后需要先展开初始化工作确定其工作方式,这就需要完成表1中的步骤1~2。此时该器件才真正地进入工作,开始采集外部模拟信号并转换,在下一个I2C总线周期中输出数据。

3.3VHDL软件实现

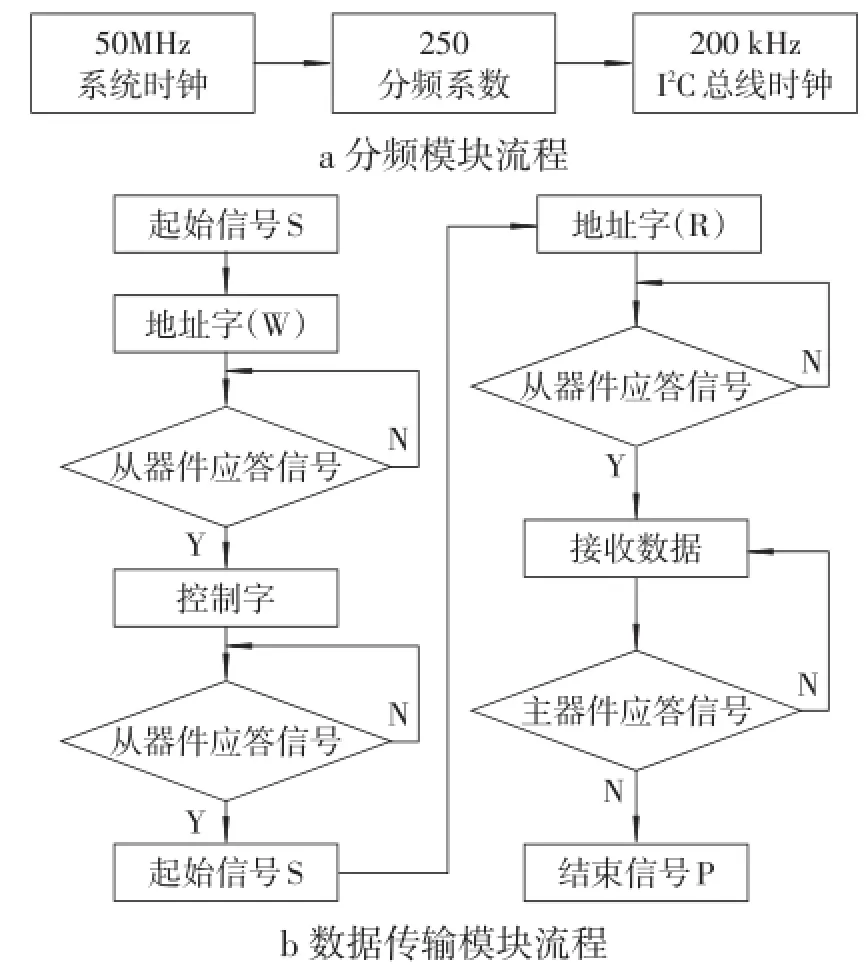

在VHDL编程中,PCF8591T器件的I2C总线通讯主要涉及2个模块:分频模块和I2C总线数据传输模块。分频模块建立I2C总线的时钟,I2C总线数据传输模块是在分频模块建立的I2C总线基础之上通过Moore型有限状态机完成,其具体流程见图4。

VHDL软件编程中,建立起FPGA对PCF8591T的完全控制,时钟总线SCL采用单向总线方式由FPGA发送所有的时钟信号至PCF8591T,数据总线SDA的通信双方是相互的数据传输过程,采用双向总线实现。编译通过后的RTL级电路如图5所示。

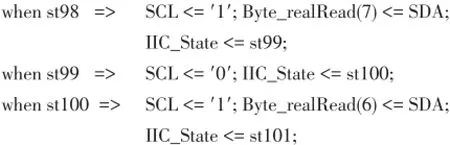

在VHDL设计的I2C软件程序中,主要涉及启动、停止、应答/非应答以及数据传送4个部分,其中数据传送部分是核心部分,部分程序如下:

图4 PCF8591T的I2C总线通讯软件流程图

图5 I2C总线RTL级接口电路

在MOORE型有限状态机的驱动下,在每个I2C总线的高电平期间读取来自PCF8591T的位转换数字量信息,经过8个总线周期自高位到低位依次读取1个字节信息量;在第8个周期的总线低电平期间完成1个字节信息量的存储,以便用于后续的处理任务。之所以是高电平进行数据读取传输,是因为有限状态机只能在状态内进行数据操作,与I2C总线的规定低电平数据变化,高电平数据稳定传输存在一定的差异。

4 仿真结果分析

I2C总线的Quartus II仿真,受到SDA数据总线是双向传输总线的影响,不能通过下载到FPGA器件里的程序实现。为了确保仿真的正常展开,引入3组来自PCF8591T的虚拟数字转换值实现。图6即引入虚拟数据后修改部分程序后的功能仿真图。

图6中的输入量data0,data1,data2模拟来自PCF8591T转换后的数字量;CLK_scl是经过分频后的I2C总线主频;Reset是I2C总线复位信号,设置为高电平保持其无效状态;SCL是I2C总线时钟,从FPGA至PCF8591T的单向时钟信号;SDA是I2C数据总线,典型双向信号;channel0_data,chan⁃nel1_data,channel2_data即经过IIC总线传送到FP⁃GA内部的3组转换的数字量。

从图6中可以看出,由于I2C总线传输送率高,A/D转换时间很短,假定3组模拟量同时转换。转换完的数字量在I2C总线控制信号作用下,依次将数字量传送到FPGA内部设置的3个寄存器中。SDA~result是FPGA内部自动生成的临时SDA总线位寄存器,可以清楚地再现IIC总线的起始信号S、应答信号/非应答信号ACK以及终止信号P。

图6 I2C总线通讯功能仿真图

5 结语

根据工业现场需求,设计了硬件描述语言VH⁃DL的I2C总线通信程序,通过Altera公司Cyclone II器件EP2C5Q208C8N在对象模数转换芯片PCF8591T上成功实施,较好地验证了FPGA器件具有良好的接口适应能力。样机试制后经过工业现场测试,获得了理想的运行结果,表明FPGA器件在工业领域也具有强健的核心竞争力。

[1]李全利.单片机原理及接口技术[M].2版.北京:高等教育出版社,2009:222.

[2]百度百科.FPGA[EB/OL].[2015-06-16].http://baike. baidu.com/link?url=uLbhqpY7MK658-NuJSVLqJebmcZ⁃lI5-TwZ04wvJPHg91cEeMEd9uojBgw8Eovx2N9I0fTWU Uozq0tR2aGRnuSK#6.

[3]Philips.PCF8591 8-bit A/D and D/A converter[K].Phil⁃ips Semiconductors,2003:5-6.

Application Research of I2C Bus Based on FPGA

Wei Haibo,Ma Zheng,Liu Jie

(School of Electrical&Information Engineering,Hubei University of Automotive Technology,Shiyan 442002,China)

As the serial bus of high performance,I2C Bus has been widely used in the field of microelec⁃tronics.Using hardware description language VHDL and Moore finite state machine,the I2C bus control⁃ler of analogy-to-digital converter PCF8591T was designed through programming on EP2C5Q208C8N platform.The experimental results show that the I2C bus controller is stable and reliable by I2C bus in⁃terface protocol.

I2C bus;serial transmission bus;finite state machine;hardware description language;inter⁃face protocol

TP336

A

1008-5483(2015)03-0048-04

2015-06-19

湖北省自然基金重点项目(2012FFA062)

魏海波(1984-),男,湖北十堰人,硕士,从事电源及其相关技术研究。E-mail:xinxin840920@163.com