低轮廓铜箔在高频材料中应用的研究

2015-08-18王红飞赵亮兵广州兴森快捷电路科技有限公司广东广州510663深圳市兴森快捷电路科技股份有限公司广东深圳518028

范 红 王红飞 赵亮兵 陈 蓓(广州兴森快捷电路科技有限公司,广东 广州 510663)(深圳市兴森快捷电路科技股份有限公司,广东 深圳 518028)

低轮廓铜箔在高频材料中应用的研究

范 红王红飞赵亮兵陈 蓓

(广州兴森快捷电路科技有限公司,广东 广州 510663)

(深圳市兴森快捷电路科技股份有限公司,广东 深圳 518028)

铜箔作为线路板中电子与信号传导通道的载体,是PCB制造中重要原料。随高频、高速PCB发展,低粗糙度铜箔应用越发广泛。本文主要研究三种不同粗糙度铜箔对PCB传输线直流电阻和高频材料的介电参数的影响,以及研究低轮廓铜箔与高频树脂体系材料结合的抗剥离强度。具体比较聚苯醛复合树脂、改性环氧树脂板材与STD、RTF、VLP铜箔的剥离强度,以及铜箔类型对线路的直流电阻以及材料介电常数、损耗的影响。

低轮廓铜箔;粗糙度;电阻;介电常数;损耗

1 前言

铜作为一种具有高电导率、成本适中、可加工性优越的导体材料,在PCB以及整个电子领域的导电材料中占主导位置,在覆铜板上和压合外层上都会使用。从铜箔制作角度进行分类,用于PCB的铜箔包括压延铜箔和电解铜箔两大类。两类铜箔原铜箔生产中都有毛面与光面,对原铜箔进行涂覆、耐热层处理及防氧化处理等一系列的表面处理加工,可以获得不同粗糙度的铜箔也称不同轮廓铜箔,如标准电解铜箔(STD)、反转铜箔(RTF)、低轮廓铜箔(VLP)三种不同粗糙度的铜箔。

PCB行业从铜箔的厚度、外观、抗张强度、剥离强度、抗高温氧化性、铜箔的质量等角度对其进行大量研究和给出相应的规定要求。随着PCB对线路的精细化提升,对铜箔的可加工能力进行大量改良提升,如低轮廓(LP)、超低轮廓(VLP)铜箔具有非常低的粗糙度,能够减少高频高速下信号趋附效应而在高频高速材料中广泛应用。目前,覆铜板介电常数取值方面没有考虑铜箔对其影响,铜箔的不同是否会影响材料的介电常数、损耗等介电性能的差异,未进行系统研究。本文主要研究标准电解铜箔(STD)、反转铜箔(RTF)、低粗糙度铜箔(VLP)三种常用的电解铜箔对某高频材料的介电性能的影响。

随着在3G/4G通信基站以及更高的以太网、云服务器的发展,PCB将朝着高频高速方向提升,对电阻、阻抗、损耗的控制精度要求将越来越高。在PCB设计和生产中,掌握铜箔对材料的介电性能影响,在实现精准的电阻和阻抗控制以及降低损耗方面有很高的参考价值。

2 实验

2.1实验仪器与材料

仪器:扫描电镜(SEM)、光学轮廓仪(Optical Profiler—Contour GT-K1)、万能材料测试仪(Material Testing Machine)、微电阻仪(Ohm Meter)、安捷伦网络分析仪(Agilent Network Analyzer-E5071C)。

材料:铜箔厚度为18 μm(0.5 oz)的VLP、RTF、STD铜箔;高频材料A(聚苯醛复合树脂体系)和高频材料B(改性环氧树脂体系)。

2.2实验过程

(1)粗糙度测试:采用扫描电镜分析三种铜箔的表面晶格颗粒大小和均匀性,采用光学轮廓仪测量三种铜箔表面衡量表面粗糙程度的Ra、Rq、Rz等参数及3D视图。

(2)剥离强度:设计长50 mm、宽3 mm的测试条,比较电镀前、后三种铜箔与高频材料A及高频材料B结合的抗拉力情况,通过实测蚀刻后的线宽w/mm和平均抗拉力度F/N,根据拉力与宽度的比值求出抗剥离的强度。

(3)直流电阻:在相同的工艺下对三种18 μm (0.5 oz)铜箔,设计线长为254 mm(10 in),制作线宽分别为0.15 mm(6 mil)、0.2 mm(8 mil)、0.25 mm(10 mil)的线路,通过微电阻仪测量各线路的电阻。

(4)介电常数测量方法:对三种不同铜箔,在相同厚度规格、材料、叠层结构设计相同内层传输线阻抗。具体使用反推统计法[1],先利用阻抗设计模型设计相同线宽与阻抗,网络分析仪测量阻抗,并通过切片实测线宽、铜厚、介厚等参数,再代入阻抗模型中反推Dk值,根据大量数据统计获得不同铜箔下的反推Dk值。

(5)损耗测量:在相同的配本、半固化片,叠层结构、传输线设计下,分别设计50 Ω(线宽0.15 mm)、100 Ω(线宽0.1 mm,间距0.125 mm)长度都为254 mm(10 inch)的带状线,利用Agilent Network Analyzer(E5071C)进行TRL校准后,测量不同铜箔类型与高频材料A的插入损耗。

3 结果与讨论

3.1表面形貌

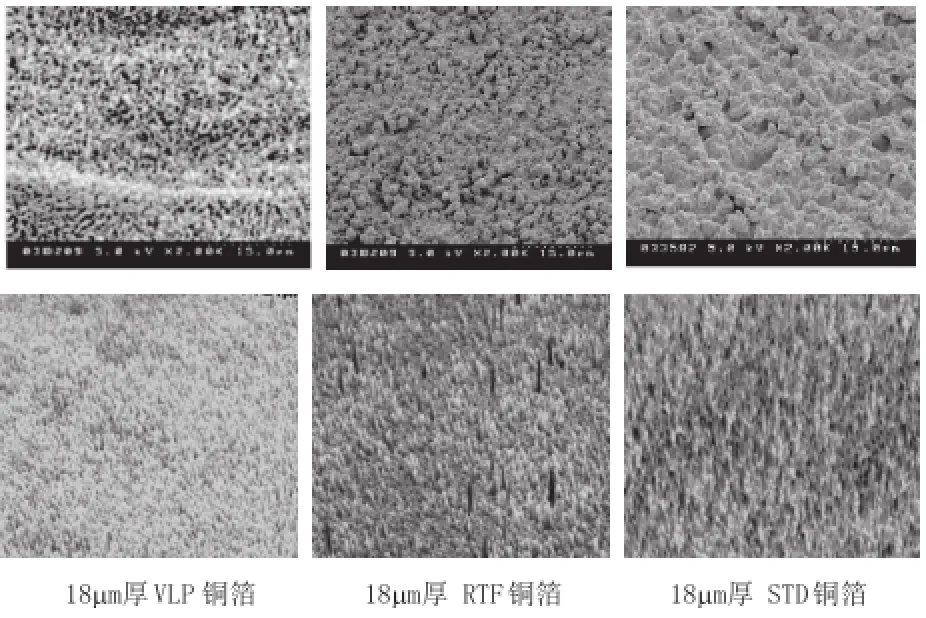

通过扫描电镜和光学轮廓仪测量PCB常用的VLP、RTF、STD三种铜箔(厚18 μm)的表面形貌,其表面颗粒大小以及3D形貌如图1所示。

图1 三种常用PCB铜箔毛面的表面形貌(上:SEM图;下:3D图)

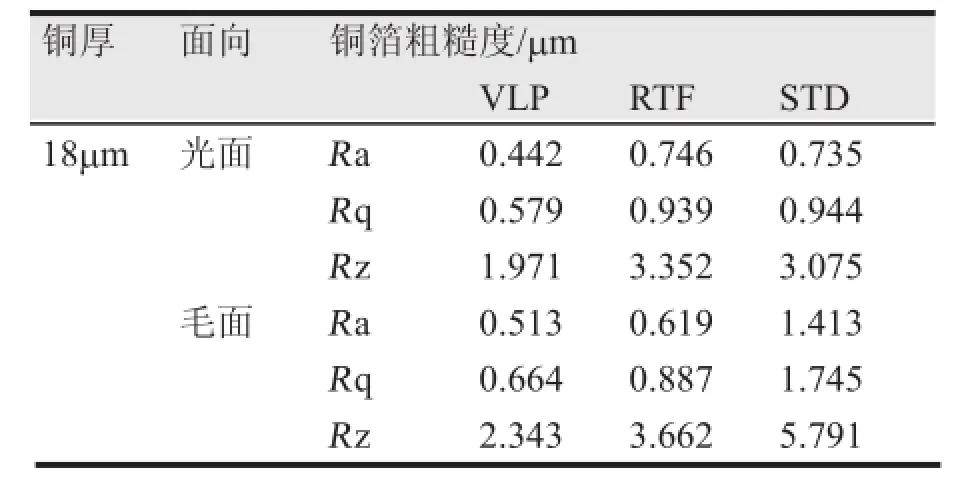

表1 铜箔的粗糙度

其中:Ra:粗糙度平均值,表示测试面积上铜箔表面形貌的粗糙;Rq:粗糙度算术平方根(RMS);Rz:粗糙度峰高与谷深落差(最大10点均值),表示测试范围内一定宽度带上铜箔表面形貌的高低落差。

从图1中可以看出,毛面颗粒大小依次是STD、RTF、VLP铜箔,其中VLP铜箔表面颗粒非常细小且分布均匀,从表1中的粗糙度数据也能看出相同的变化趋势,VLP铜箔的Ra、Rq、Rz值都较RTF铜箔低,RTF较STD铜箔低。

3.2不同树脂体系下的抗剥离强度

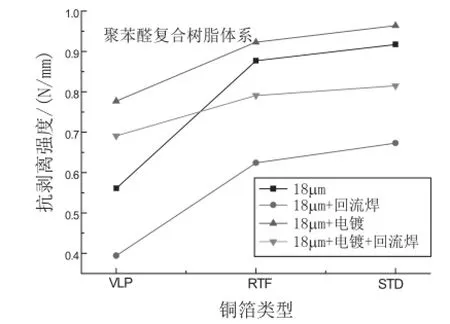

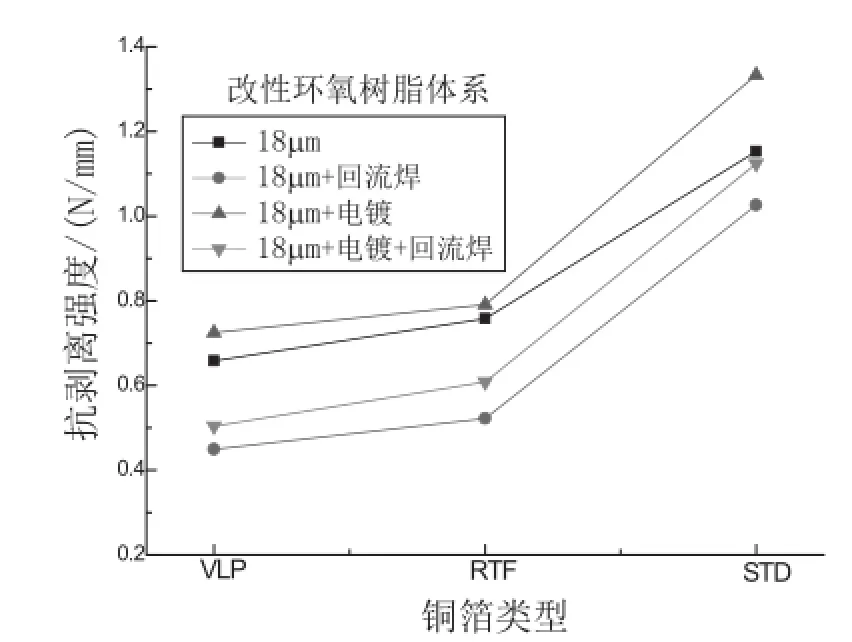

IPC-4562标准规范[2]对铜箔的剥离强度要求,按照IPC-TM-650测试方法,要求金属箔的最小剥离强度应符合适用详细规范的规定或供需双方商定。行业根据材料类型要求常规板材抗剥离强度≥0.875 N/mm高频高速类板材≥0.520 N/mm。在邱彦佳、蔡芬敏等[3][4]认为铜箔的厚度及加工会影响其抗剥离强度。文章研究对比三种18 μm铜箔在聚苯醛复合型、改型环氧树脂体系的高频材料中的抗剥离强度,以及经过电镀、5次回流焊后抗剥离强度的变化。图2、图3分别为某高频材料A(聚苯醛复合树脂体系)和某高频材料B(改性环氧树脂体系)中三种铜箔的抗剥离强度变化趋势。

从图2、图3中可以看出,随着铜箔粗糙度的增大其与树脂结合力增强;过回流焊后抗剥离强度降低,经过电镀后其抗剥离强度增大。基铜经蚀刻且不过回流焊后进行拉力测试,VLP、RTF铜箔与两种树脂体系结合力最小为0.55 N/mm,能满足行业对高频高速材料要求抗剥离强度>0.52 N/mm;表层电镀后过回流焊,也能满足高频高速材料对抗剥离强度的要求。

图2 聚苯醛复合树脂体系下抗剥离强度对比

图3 改性环氧树脂体系下抗剥离强度对比

3.3对直流电阻的影响

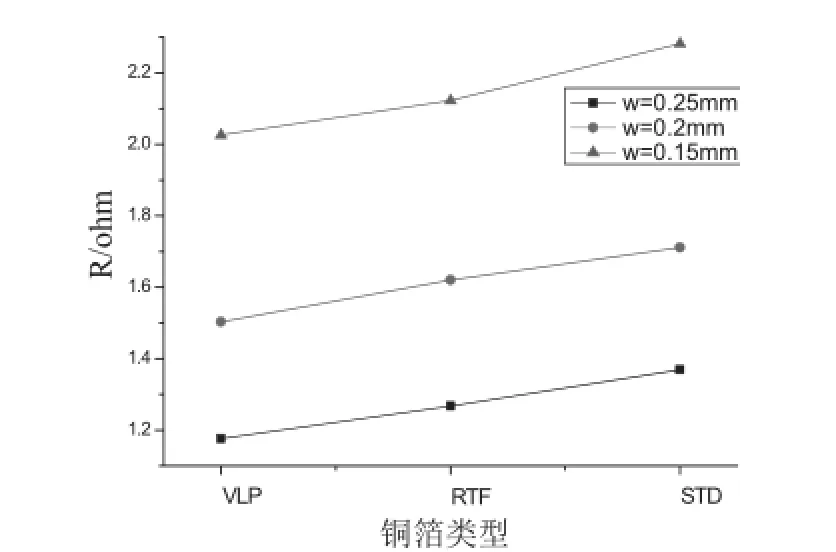

在PCB设计中,一些电子产品对线路板内传输线的直流电阻有一定要求,目前,行业对有直流电阻要求的线路板一般控制在设计值的±10%范围,部分要求控制在±5%。根据经典欧姆定律:(其中,R为电阻,Ω;ρ为铜电导率0.017593(Ω·mm2/m);电阻仅与线路长度和横截面积有关。然而,对于不同铜箔类型设计相同线宽、长度的传输线的直流电阻是否一定相等。根据现有铜箔规格厚度按照称重法计量,不同铜箔类型的加工过程中经微蚀刻后,铜面厚度以及覆盖有机涂层厚度存在差异,导致相同规格厚度的有效导体厚度不同,造成相同线宽下有效导体截面差异[5]。在铜箔制造工艺中,姜力强[6]发现在生产电解铜箔时,沉积层的电阻率开始随阴极电流密度的增加而增加。为研究不同铜箔对传输线的直流电阻的差异,对含18 μm的VLP、RTF、STD三种铜箔的板材,各设计十组长度为254 mm线宽分别为0.15 mm、0.2 mm、0.25 mm的传输线,经过内层蚀刻后使用微电阻仪(Ohm Meter)测量各线宽下的电阻,如图4所示,相同线宽、铜箔下的电阻均值随铜箔类型的变化趋势。从图4中可以看出,表面粗糙度最大的STD铜箔直流电阻最大,其次是RTF、VLP铜箔,相同设计下RTF铜箔较VLP铜箔的直流电阻偏大4%~6%。

图4 传输线长254mm直流电阻随铜箔类型变化趋势

3.4对介电常数的影响

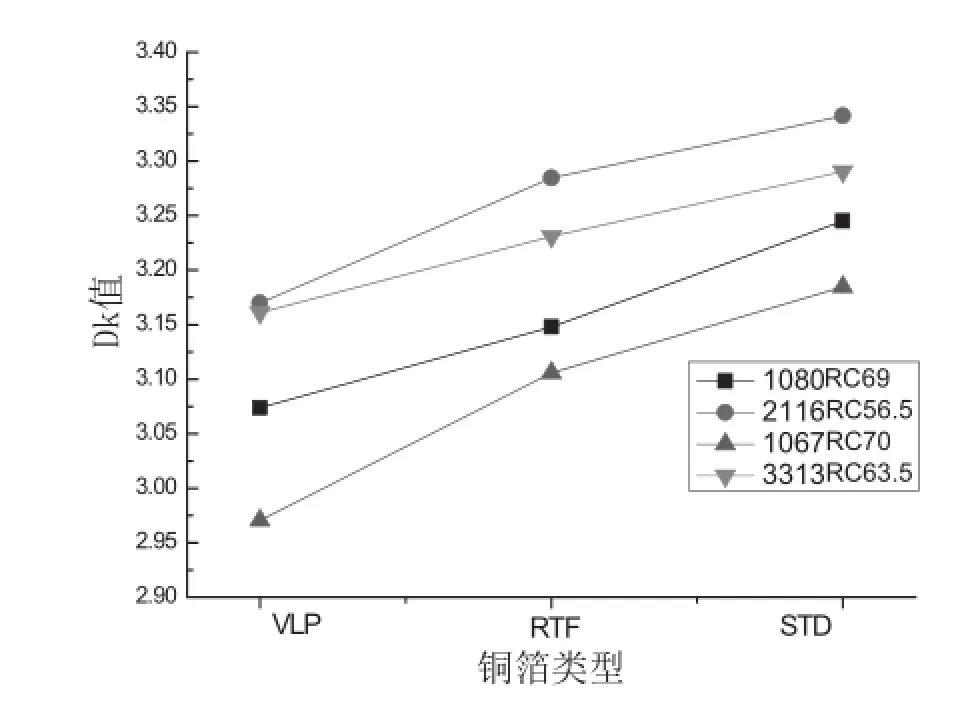

介电常数是PCB阻抗设计中不可或缺的因子,指相对于真空增强材料储能容量的能力,属于材料本身所固有的电气特性。在IPC-650测量介电常数的标准中,含铜与无铜的板材都可以作为测试样品。此前,根据材料的介电常数依赖于板材中树脂与玻纤的成分以及所占比值,不受铜箔的影响。然而,铜箔本身也具有一定介电性能和储能能力[7],影响覆铜板整体的介电常数;在铜箔与板材压合过程中,铜箔毛面嵌入在树脂内,类似于铜箔填充到树脂中,改变树脂的介电常数值。因此,为研究铜嵌入树脂内的程度对板材的介电常数的影响,是否与铜箔表面粗糙度有关,通过反推统计法[1]对不同粗糙度的STD、RTF、VLP铜箔与某高频材料(A)的介电常数情况,采用0.5 oz的三种铜箔与2张1080(RC69%)压合制作芯板,并使用完全相同的叠层并设计完全相同的多组阻抗条(coupon)。通过测量各附连扳(coupon)的内层阻抗值,利用测量对应线宽、介厚、铜厚等数据进行反推统计Dk均值,对100组数据进行统计所得的结果如图5所示,从图中可以看出,1080配置VLP、RTF、STD的介电常数分别为3.073、3.148、3.245,粗糙度越低的铜箔对应的Dk值越小。

图5 1080与三种铜箔的反推统计介电常数分布

采用与上1080同样的方法,对比某高频材料(A)中1067、3313、2116三种规格半固化片与STD、RTF、VLP铜箔压合的介电常数情况,通过设计相同叠层、相同的阻抗布线下不同铜箔类型的Dk均值,利用反推统计法获得不同情况下的介电常数均值的变化r势如图6所示。

从图4中可以看出,采用反推统计法获得的介电常数随着铜箔表面粗糙度的增大而增大。相同板材条件下,使用STD铜箔较RTF铜箔下的介电常数大0.07~0.1;使用RTF铜箔较VLP铜箔下的介电常数大0.06~0.09。因此,在使用低粗糙度铜箔材料设计高精度阻抗时,需要考虑铜箔对介电常数的影响。

图6 三种铜箔与高频材料A的几种固化片压合的反推Dk变化趋势

3.5对损耗的影响

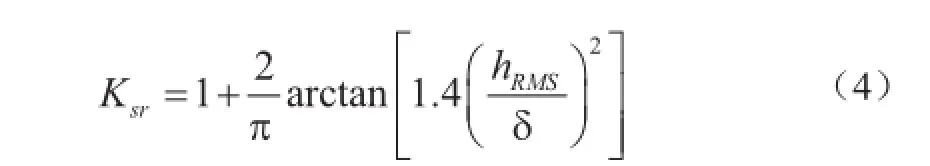

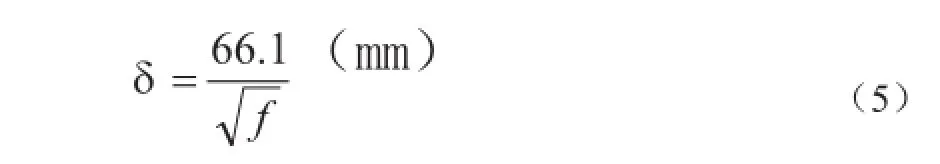

在高频高速信号传输中,传输线受到变频场的作用,存在趋肤效应(skin effect)的现象,导体内部的电流分布不均匀,电流趋向在导体表面富集。频率越高趋肤效应越强,导致损耗增大。根据Hammerstad[8]解释传输线模型中表面粗糙度对损耗影响,是将光滑导体的信号损耗乘以Hammerstad系数,公式如下所示:

其中,Ksr为趋肤系数,hRMS为表面粗糙高度的均方根(Rq),δ为趋肤深度。趋肤深度受传输频率的影响,有:

根据经典损耗理论,传输线总损耗[8]根据公式:

考虑到趋肤效应,传输线的总损耗通过修正有:

其中,αdt为总损耗,αdc为无趋肤效应的导损,αdd为介损。

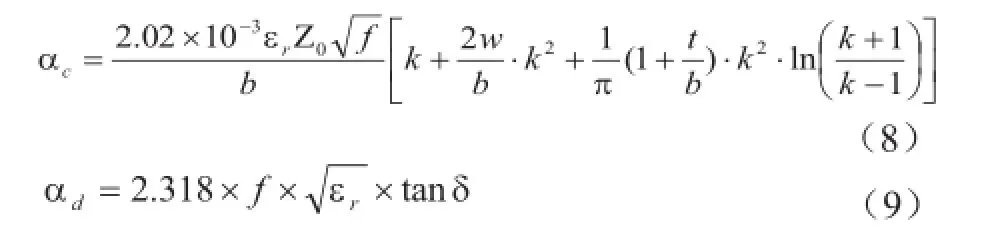

以带状线为例,带状线的导体损耗和介质损耗有以下公式:

其中,f为信号传输频率,εr为介电常数,t为传输线铜厚,w为传输线宽度,b为两地之间的介质厚度,常数为介质损耗因子。

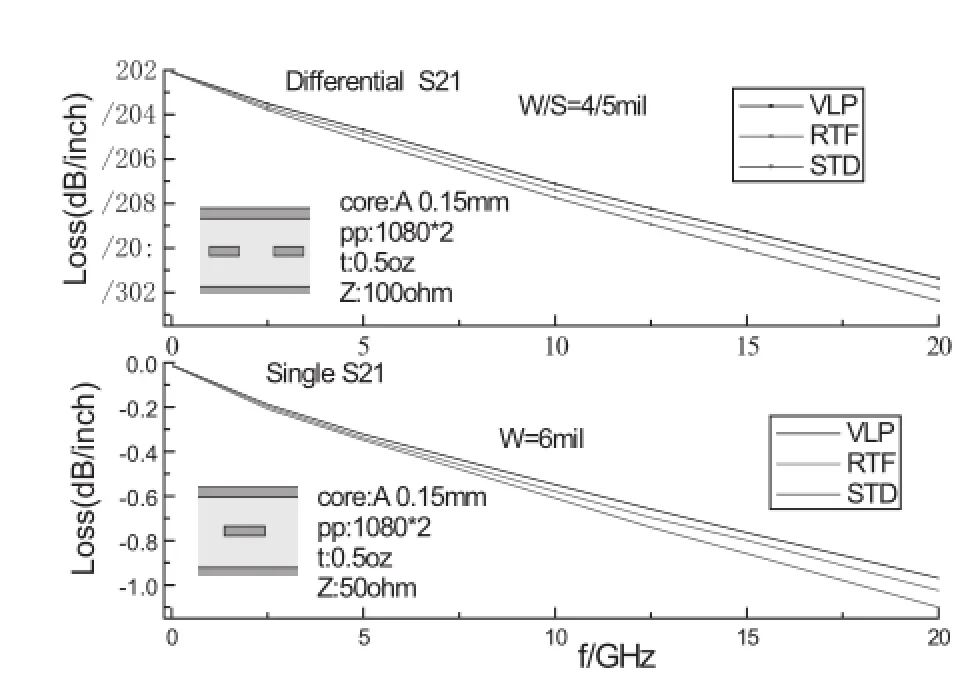

从上损耗理论损耗的影响因素来看,铜箔表面粗糙度影响传输线的导体损耗,粗糙度越大,趋肤效应中的Hammerstad系数越大,导损、总损耗越大。实验采用了高频材料A(1080)分别配置VLP、RTF和STD,在相同的配本、半固化片,叠层结构、传输线设计下,设计50 Ω、100 Ω的带状线,利用Agilent Network Analyzer(E5071C)进行TRL校准,测量不同铜箔下的插入损耗随频率的变化关系结果如图7所示。

图7 VLP、RTF、STD铜箔带状线的信号损耗

从图7中可以看出,相同条件下(材料、频率、线宽、叠层),粗糙度越大的STD铜箔损耗越大。当频率小于3 GHz,三种铜箔对插入损耗的影响较小,随着频率增大,三者的差异越来越明显。在10 GHz下,VLP、RTF和STD三种铜箔下的带状传输线(宽6 mil)的损耗分别为0.548 dB/in、0.579 dB/in 和0.61 dB/in。10 GHz下,VLP较RTF铜箔的单位长度损耗偏小0.031 dB/in;RTF较STD铜箔的单位长度损耗偏小0.033 dB/in。因此,低粗糙度铜箔有利于降低高频高速信号的损耗。

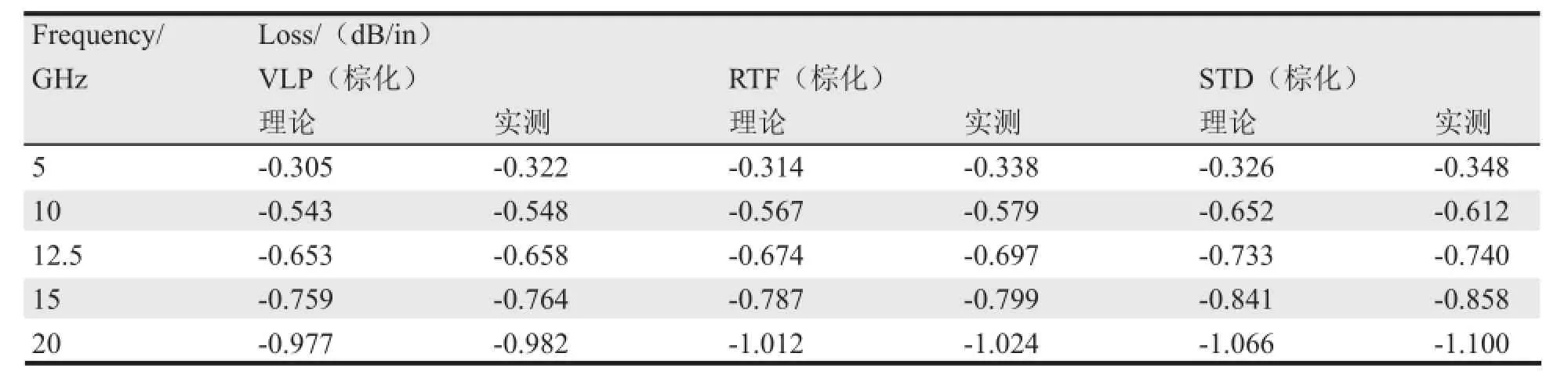

利用三种铜箔的Rq值以及公式(4)~公式(9),对上图7中三种铜箔下的单端损耗进行理论计算,对比5 GHz ~ 20 GHz频率下的理论损耗和实际损耗如表2所示。

从表2可以看出,理论损耗与实际损耗变化趋势基本重合。说明经典趋肤效应和损耗计算公式能解释粗糙度对插入损耗的影响。根据经典损耗计算公式(9),相同的材料下的介损相同;相同的线宽、阻抗、叠层和材料下,由公式(9)得αc值不变;三者的损耗差异来源于粗糙度造成趋肤效应系数(Ksr)的不同,粗糙度越低Ksr越低,越有利于降低损耗。因此,低粗糙度铜箔将在高频高速材料中广泛使用。

表2 带状线(单端6mil)的实测损耗与理论损耗对比

4 小结

(1)VLP、RTF、STD铜箔粗糙度Ra分别为0.513、0.619、1.413。

(2)VLP与聚苯醛复合树脂体系压合的抗剥离强度为0.55 N/mm,经过电镀及回流焊后抗剥离强度为0.69 N/mm;与改性环氧树脂体系压合的抗剥离强度为0.63 N/mm,经过电镀及回流焊后抗剥离强度为0.52 N/mm;RTF铜箔较VLP抗剥离强度高,都满足高频材料对剥离强度的要求。

(3)相同条件下,STD铜箔较RTF铜箔的直流电阻大4%~6%,RTF铜箔较VLP铜箔的直流电阻大4%~6%。

(4)相同板材条件下,通过反推法获得STD铜箔介电常数较RTF铜箔的偏大0.07~0.1;RTF铜箔较VLP铜箔的介电常数大0.06~0.09,高精度阻抗设计需要考虑铜箔类型对材料有效介电常数的影响。

(5)低粗糙度铜箔降低高频高速材料的损耗,在聚苯醛复合树脂体系中,10 GHz下VLP较RTF铜箔的单位长度损耗偏小0.031 dB/in;RTF较STD铜箔的单位长度损耗偏小0.033 dB/in。

[1]范红,王红飞,陈蓓. PCB板材介电常数的测量方法及其应用[J]. 印制电路信息,2014.11.

[2]IPC-TM-650标准.

[3]邱彦佳. 不同厚度铜箔对基板剥离强度的影响[J].印制电路信息.2008(4):27-31.

[4]蔡芬敏. 电沉积参数对电镀妥铜箔组织性能的影响[M]. 南昌大学学位论文, 2014.

[5]Alexander. A Designed Experiment for the Influence of Copper Foils on Impedance, DC Line Resistance and Insertion Loss[J].

[6]姜力强,郑精武,李华. 电沉积铜层的力学和电学性能的研究[J]. 稀有金属,2003,27(3):347-349.

[7]邝向军. 关于金属介电常数的讨论[J]. 四川理工学院学报(自然科学版), 2006.4(19).75-79.

[8]Stephen C. Thierauf .High-Speed Circuit Board Signal Integrity[M]. Artech House, Inc. Boston London.

范红,技术中心研发工程师,从事高频、高速PCB相关研发工作。

Study on low profile copper foil effect on high frequency material

FAN Hong WANG Hong-fei ZHAO Liang-bing CHEN Bei

The copper foil as the carrier of electronics and signal transduction channel in printed circuit board, is one of the most important raw material for PCB manufacturing. With the development of high-frequency and high-speed PCB, low profile copper foil is widely used in specific fields. This paper mainly studies the impact of copper roughness on DC resistance and dielectric properties of PCB materials. Peel strength and insertion loss of STD, RTF and VLP laminated with different high-frequency laminates were studied.

Low Profile Copper Foil; Roughness; Resistance; The Dielectric Constant; Insertion Loss

TN41

A

1009-0096(2015)08-0029-06