基于FPGA的同步器信号采集技术研究

2015-08-10高志远闫文宇

高志远,闫文宇

(中国飞行试验研究院 陕西 西安 710000)

在航空测试中需要采集并记录同步器信号参数,用于保障飞机的安全飞行,和评估飞机的部分性能。同步器信号参数主要包括:飞机的姿态角,航向角,发动机喷口直径这些参数[1]。

飞机姿态和航向陀螺输出的角度信号为三相交流同步器信号,又称自整角机信号。这些信号经过专用同步器芯片处理后,可以得到数字两形式的角度信号和模拟量形式的较速率信号[2]。

三相交流同步器信号为正弦波电压信号,交变电势与输出信号的角度对关系为3个相角差位120°的正余弦公式,输出信号的角度仅取决于三相信号幅值的比值[3]。

1 系统硬件设计

系统由同步器预处理模块,电平转换模块,数模转换模块,处理器组成。各功能模块在处理器的控制下协调工作完成两路角度信号和角速率信号的采集。系统整体结构如图1所示。

1.1 同步器预处理模块

此模块由专用同步器信号处理芯片SDC辅以外围电路组成。自整角机三线输出的角度信号,经SDC同步器处理芯片进行预处理。处理输出成位数可选的数字量角度信号到数据寄存器,同时输出模拟量角速率信号。

1.2 电平转换模块

图1 系统整体结构图Fig.1 The overall system structure diagram

由于SDC芯片工作电压位5 V而FPGA的IO工作电压是3.3 V,需要用电压转换芯片74LVC164245使SDC输出5 V信号,转换为FPGA可用的3.3 V信号。

1.3 模数转换模块

同步器输出两路模拟量的角速率信号,经AD7606模数转换芯片转换为16位数字量供处理器使用。

2 软件设计

系统的运行由FPGA控制完成,软件由角度读取模块,角速率读取模块,控制模块,数据缓存模块,配置模块和接口模块组成。各功能模块在控制模块的控制下工作,来完成对角度信号和角速率信号的处理工作。组合模块如图2所示。

2.1 配置模块

图2 组合模块结构图Fig.2 Combined module structure diagram

此模块主要从主控板卡获取以下信息:1)通道使能;2)通道测量范围;3)通道采样率。功能模块以这些配置信息,采样数据并进行数据处理。

2.2 角度读取模块

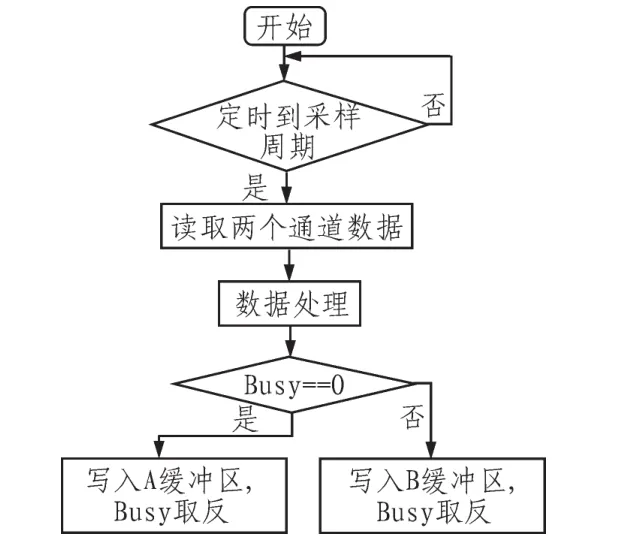

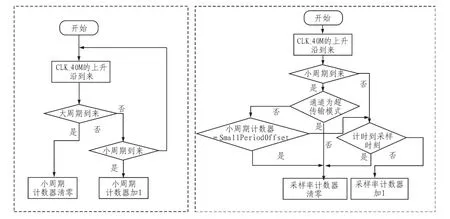

此模块以一个较高的采样率对同步器芯片转换后的数据进行采样,采样后的数据在两个寄存器中进行缓存[4],具体过程如图3所示。

综上,笔者析得国内正念疗法研究主题相对集中,围绕正念训练、正念、心理健康、正念干预等核心关键词,形成了以躯体疾病、禅修、MBSR、社会生活问题等重点关键词为代表的热点主题,在这些热点主题四周又衔接诸多研究议题。

图3 角度读取流程图Fig.3 Angle read flow chart

系统以64K的频率采样,当定时器到达采样周期后首先读取第一通道的角度数据,同时判断Busy信号确定将采样的数据写入那个缓存,然后读取第二通道数据,同时根据Busy信号将采样数据写入第二通道的缓存。

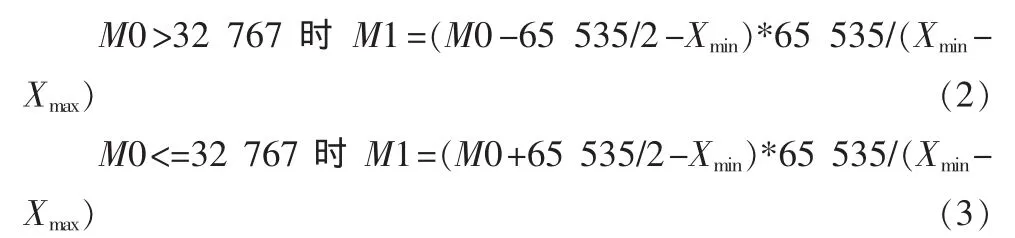

同步器芯片默认测量范围时0~360°对应码值0~65 535。假设用户配置某通道测量范围时0~360之间的任意范围Xmin~Xmax,则采集的数据需要按公式(1)进行变换,其中M0是采集的原始数据,M1是转换后的数据。

假设用户配置某通道测量范围时-180°~180°之间的任意范围 Xmin-Xmax,则采集的数据需要按公式(2)或(3)进行变换,其中M0是采集的原始数据,M1是转换后的数据。

在读取角度数据时按照同步器芯片SDC的时需要求,通过相应控制位的操作可以使转换后的数据锁存在输出寄存器,此时即可对其进行读取。

2.3 角速率读取模块

同步器芯片对输入的三相交流电进行处理后输出对应模拟量的角速率信号,此信号经AD转换器件AD7606快速转换为数字量。处理器读取AD7606转换后的角速率数据过程与读取角度数据类似,采集后的数据根据Busy信号存入相应的缓存。

在读取角速率数据时按照同步器芯片SDC的时需要求,通过相应控制位的操作可以使转换后的数据锁存在输出寄存器,此时即可对其进行读取。由于布板面积的限制,AD7606采用并行字节读模式,转换后的数据按高低字节输出,两个通道的角速率信号[5]。

2.4 控制模块

控制模块负责对采集数据的读取,并按照通信协议定的时序要求将数据传输给主控板卡。

2.4.1 时序控制

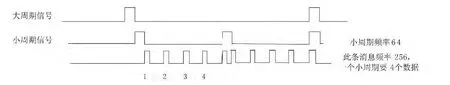

每个通道都有一个采样率计数器,以CLK_40M的时钟触发计数。假设通道为超传输模式如图4所示,当小周期到来时采样率计数器清零,当计时到采样时刻将次通道写使能置1,将读取的通道数据写到数据RAM中OutBuffOffset开始的缓存中。

控制模块按照图5所示过程实现时序控制,每当采样率计数器为零时将此通道的采样数据写到输出缓冲区。

2.4.2 数据传输

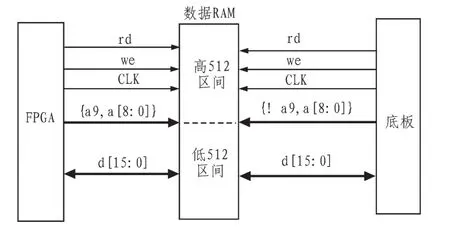

数据空间使用1K的RAM分为高512地址区和低512地址区,FPGA和地板对数据空间的连接如图6所示。

在对数据空间操作时,按照小周期同步切换高位地址实现乒乓操作,如图7所示。

图4 超传输时序图Fig.4 Super transmission timing diagram

图5 时序控制的实现过程Fig.5 Process to achieve timing control

图6 FPGA和底板与数据RAM连接图Fig.6 FPGA and motherboard and RAM data connection diagram

图7 数据空间乒乓操作时序Fig.7 The ping-pong operation timing data space

每当小周期同步触发时钟上升沿到来之后,FPGA将采样的数据写入512空间;同时底板从另512空间读取上次存放的数据,送给主控。

3 结束语

文中解决了两通道同步器信号的实时采集问题。可以实时对两通道的角度和角速率信号采集,并按照传输协议将数据传输给主控板。用户可按照采集信号的特性配置适当的测量范围,和采样率来提高采集信号的精度。经过仿真和系统调试,验证了此同步器采集系统软硬件设计合理,系统稳定性和精确度都达到了设计指标要求。

[1]苏建军.飞行参数记录系统同步器信号的采集[J].自控与测量,2003(3):42-44.

[2]杨宏伟.感应同步器信号采集原理[C]//2011航空试验测试技术学术交流会论文集,2010.

[3]庞湘平.三相交流同步器信号的数字化处理[J].仪表技术,1999(6):41-42.

[4]王先全.基于FPGA的感应同步器的数据采集和处理的研究[J].仪表技术与传感器,2010(5):41-43.

[5]于克泳,孙建军.新一代16位8通道同步采样ADC-AD7606在智能电网中的应用[J].电子产品世界2010(17):63-65.

[6]闫利军.基于DSP和FPGA的多通道RS422总线采集技术研究[J].硅谷2014(7):53-55.

[7]李国旭,毛红艳,孟祥斌,等.基于FPGA的无刷直流电机调速系统设计与实现[J].电子设计工程,2015(17):137-140.

[8]蒋治国,李焕.一种移动通信信道仿真器的FPGA实现[J].电子设计工程,2014(23):158-160.