一种半并行多芯片测试方法

2015-06-13王志平季晓燕

王志平,季晓燕

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

目前,集成电路测试能力和水平不仅得到了很大的提高,且进入了高速发展时期,国际上高端的ATE集成电路测试设备主要集中在美国和日本,如美国的泰瑞达Teradyne公司的UltraFLEX测试系统、日本的爱德万Advantest公司的V93000测试系统和T2000测试系统等,但自动测试系统价格昂贵,国内为提高利用率,通常将硬件配置到基本状态。

国内射频集成电路技术的研究主要都集中于设计和加工工艺上,其测试技术的研究也是近几年才开展起来。目前,基于ATE的数字、模拟和混合集成电路测试技术已经比较成熟,基于ATE的RF芯片测试技术尚在发展和完善中。因此,在现有的软硬件条件下探索射频测试的方法,突破射频测试技术,实现多射频芯片半并行测试,可有效缩短测试时间,减少测试成本,为射频芯片的量产测试打下基础。

1 高效半并行测试方案

多芯片(multi-site)并行测试可有效地降低RF射频收发芯片的测试成本,但要实现完全的并行测试,并行数量越大,测试系统需要的硬件配置越高。

以V93000测试系统为例:为了支撑4路I/Q并行测试,需要2块MBAV8模拟板卡;为实现8路RF信号并行测试,需要2套RF射频板卡。而实际上,由于模拟板卡和射频板卡利用率相对偏低,为提高设备利用率,一般仅配置到基本状态,即2套RF射频板卡和1块MBAV8模拟板卡。

MSE是关于多芯片测试工作效率的一种表征方法,用百分数表示,是一个测试系统的品质和是否适合高产测试的指示器[1,2]。MSE计算公式为:

MSE=(1-(((MSTT-SSTT)/NS-1)/SSTT)*100。式中,MSE为多芯片并行测试效率(%);SSTT为单芯片测试时间;MSTT为多芯片测试时间;NS为并行测试芯片个数

一般来说,V93000测试系统数字资源配置充足,模拟射频部分资源仅配置到基本状态,为减少测试时间,首先分析测试时间分布。

整个测试时间分布分为如下5个部分:①测试系统软件/硬件启动;②测试板启动(继电器…);③待测芯片启动(电源/数字信号);④待测芯片测试(RF/基带部分发射和接收测试);⑤Post流程(加载和计算,limit)。

为实现高效半并行测试,所有可并行的启动设置只能运行一次。在上述所有步骤中,测试系统软件/硬件启动、测试板启动和待测芯片启动应该仅并行运行一次。对于后续流程来说,由于V93000测试系统具有将此流程隐藏加载和计算的功能,因此Post流程时间可以忽略。只有待测芯片测试部分应该被连续运行,增加了测试时间。待测芯片测试可简单的定义为使用模拟/数字触发后运行测试向量,整个运行过程的测试时间分为测试系统内部运行(Analog,Digital,SW)和运行时间两部分。

为了提高半并行多芯片测试效率,唯一可以串行运行的部分是“运行时间”,测试系统硬件部分多芯片之间的测试向量重启时间也需要避免,也就是说所有多芯片运行时必须处于同一个向量集(shot)。

通过研究发现,为满足上述所有需求,编写测试程序时可参照单颗芯片的方案将多芯片测试放在一个向量集里。理想状态下高MSE半并行测试执行程序如图1所示。

图1 一个测试向量shot的半平行测试

2 模拟激励

模拟激励方面,在已有测试系统的硬件条件限制下,为了实现不同芯片的shot运行,唯一的方法是分享资源。因为在多芯片测试情况下,每个芯片使用的激励是相同的,可以使用内部或外部组件来进行分享。

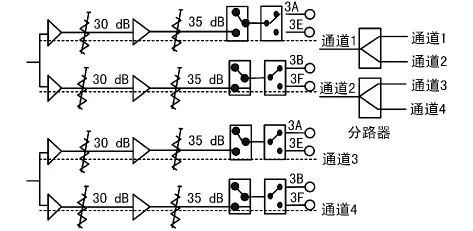

2.1 RF激励

RF射频卡的第3类端口在内部分解成2个相同的通道,这2个通道使用同一个射频源。因此,如果V93000测试系统硬件包含2套射频板卡,那么便拥有2个相同通道,可支持4颗芯片并行测试。当并行测试芯片的数量超过4颗,则需要外部的功率分路器(Power Splitter)来实现射频源的共享,如图 2 所示[3]。

图2 RF激励分享

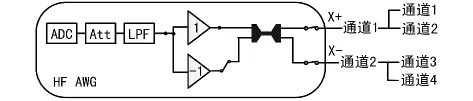

2.2 基带(Baseband)激励

在基带部分,一块 MBAV8包含 4块 VHF AWG,可以支持2个芯片的IQ输入。如果支持4颗芯片,需要利用差分从一个AWG中得到2路信号。如果支持大于4颗芯片并行测试,需要外部缓冲器来驱动2个通道的信号,基带激励分享如图3所示。

图3 基带激励分享

因此,使用上述方法,可以基于有限的硬件资源同时驱动多个芯片。

3 模拟测量

在已有测试系统的硬件条件限制下实现半并行测试需要考虑的另一个问题是测量部分。当需测量的芯片大于1颗时,必须保证串行测试发生的几率最低。

3.1 RF测量

假定V93000测试系统硬件包含2套射频板卡和1块MBAV8模拟板卡,这时V93000测试系统可以支撑4颗芯片的并行测试。对于大于4颗芯片并行的情况,V93000测试系统可以提供“多芯片交错(site interlace)”功能来支持一个测试向量shot的半并行测试[4,5]。

多芯片交错可以使用HW触发在同一个Sequence程序中将继电器切换至不同的通道(例如:从2A1到2B1),不同通道对应着不同的待测芯片。采用这种方式,只需对同一个Sequence中的程序进行串行,而不需要串行不同的 Test Method[6,7]。

对于16颗芯片并行测试,需要使用测试板上的RF继电器来进行通道切换,这些继电器是由数字通道进行开关控制的。可以在测试向量中控制继电器开关,测量时采用一个测试向量shot。RF继电器如图4所示。

图4 RF继电器

3.2 基带(Baseband)测量

V93000测试系统的一块MBAV8模拟板卡具有4个VHF数字化仪表,可以同时支持2对IQ信号的测量。因此,如果要实现4个芯片同时测量,需要寻找一种方法在同一个pattern实现不同通道的切换,从而提高MSE,目前主要有以下3种方式实现切换:Sequencer控制程序(V93000功能部件)、板级驱动数字通道控制和模拟开关代替数字控制的继电器。

3.2.1 Sequencer控制程序

V93000测试系统拥有的一个独特的功能是“Sequencer Controlled Utility”,公用通道借助专用的串行接口用数字信号进行控制。这种通道相比于通用静止通道的优势在于可以在Sequencer中进行切换和同步读取。这种接口需要至少4个数字管脚通过Utility Block连接到芯片测试板上,接口描述如表1所示。

表1 Utility接口描述

16个utility block是相互独立的,可在同一时间通过各自的串行接口进行操作。Sequencer驱动通道如图5所示。

图5 Sequencer驱动通道

3.2.2 板级驱动数字通道控制

对于硬件无法支持Sequencer Controlled Utility功能的测试系统,它的数字通道的电流驱动能力无法驱动这些继电器,这时可以通过增加驱动来提供足够的电流。采用这种方式,可以用数字通道控制继电器开关。板级驱动数字通道控制如图6所示。

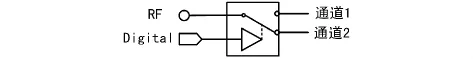

3.2.3 模拟开关代替数字控制的继电器

最后一种方式是选择不需要大电流驱动的模拟开关进行通道切换,这样的话数字通道可以直接控制模拟开关切换,模拟开关如图7所示。

图6 板级驱动数字通道控制 图7 模拟开关

4 实际测试情况比较

在实验过程中进行了典型的RF到基带和典型的基带到RF通道的测试[8]。

测试的前提条件如下:芯片并行测试数量为8颗;测试系统硬件配置为2套射频板卡和1块MBAV8模拟板卡;激励部分:RF的port3采用外部的功率分路器(Power Splitter)来实现射频源的共享,AWG采用差分加外部缓冲器的方式。测量部分:RF部分采用多芯片交错,基带测量部分采用模拟开关。

4.1 基带到RF测试

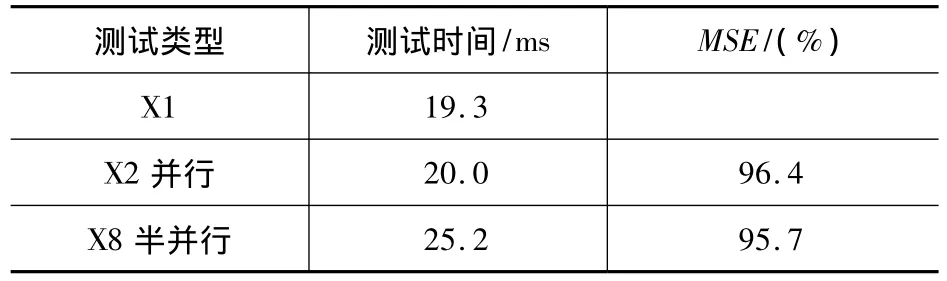

测试向量运行时间:4 Msps* 1 024 pts=>250 us;射频板卡开关切换时间为1 ms。BB-RF通道测试时间及MSE如表2所示。

表2 BB-RF通道测试时间及MSE

4.2 RF到基带测试

基带测试向量运行时间:4 Msps*1 024 pts=> 250 μs;模拟开关切换时间:<10 μs。RF-BB 通道测试时间及MSE如表3所示。

表3 RF-BB通道测试时间及MSE

通过对比测试时间和MSE的结果可以看出,半并行状态的MSE近乎等于全并行状态的MSE,因此该测试方案可有效提高测试效率,降低测试成本。

5 结束语

举例展示了在V93000测试系统硬件资源受限的条件下,如何利用测试系统资源和测试板相结合的优势实现半并行测试,提高了测试效率MSE,降低了测试成本,并为同类射频芯片的半并行测试提供了有效参考。

随着半导体技术的发展,卫星通信领域、卫星导航领域、雷达通信领域和电子通信领域等市场对射频集成电路的需求日益剧增,因此无论是在射频集成电路研发阶段还是生产阶段均有大量的测试需求,工业化生产将期望更高水平的并行测试效率和测试成本的进一步节约。

[1]WEIMER J.图形测试:多工位模拟和混合信号器件并行测试效率的关键[J].中国集成电路,2011,140(1):60-65.

[2]WEIMER J.使用Multi-Sector技术提高混合信号芯片的并行测试效率[J].中国集成电路,2011,145(6):76-79.

[3]郭文刚,郗洪杰.阵列系统中多端口网络噪声系数测试分析[J].无线电工程,2011,41(3):59 -61.

[4]王 智,陈宝林.基于VEE的射频模块自动测试系统设计[J].无线电工程,2014,44(6):77 -80.

[5]陶新萱,廖海涛.Verigy 93000中直流参数的并行测试方法[J].中国集成电路,2011,145(6):80 -83.

[6]裴颂伟,李兆麟,李圣龙,等.基于V93000的SoC中端口非测试复用的ADC和DAC IP核性能测试方案[J].电子学报,2013,7(7):1 358 -1 364.

[7]陶新萱.Verigy 93000 SoC测试系统及测试中偏置电流的实现[J].电子工业专用设备,2011,192(1):4 -6.

[8]马康健,秦丹阳.多端口射频开关矩阵控制测试系统[J].无线电通信技术,2013,39(3):57-60.