基于FPGA的多传感器集成光纤传输系统

2015-06-09袁俊杰胡天宇

袁俊杰,胡天宇

(北方工业大学机电学院,北京 100144)

基于FPGA的多传感器集成光纤传输系统

袁俊杰,胡天宇

(北方工业大学机电学院,北京 100144)

为实现直接从传感器接口到光接口的高速度、高集成度的传输系统,提出了一种基于FPGA的多传感器集成光纤传输系统方案。以FPGA和光纤收发模块为简单架构,搭建了光纤传输系统硬件平台,在此基础上,开发了系统的智能化软件。系统实现了对模拟接口和数字接口的传感器信号的采集与传输,并通过应用时分复用原理,实现了多路传感器信号通过单光纤传输。测试结果表明系统具备一定误码侦测能力,可满足复杂工业现场传感器信号传输距离远、实时性高的需求。

光纤通信;数字光纤传输系统;现场可编程门阵列;时分复用;传号反转码编解码

0 引言

随着信息技术的发展,光纤通讯被广泛应用于视频监控、语音通话、图像传输、作战指挥系统等领域[1-2]。随着工业现场的系统复杂程度、可靠性、以及自动化管理等要求不断提升,现场总线及工业网络得到了广泛应用。与传统的以电信号为媒介的传输网络相比,光纤传输的数据容量大、距离远、电磁兼容性强,尤其适合恶劣工业环境,以光纤为介质的以太网及现场总线已开展了应用研究[3]。目前应用中一般通过光纤转接模块将原来以太网、RS485、CAN等总线的电信号转变为光信号进行传输,以提高信号传输距离和抗干扰性能[4],通常是对原有链路的改造升级。在工业测控系统设计阶段,若能直接在传感器输出端进行电光/信号转换,则能进一步提高系统抗干扰能力和集成度,提高可靠性。在某些环境恶劣的应用场合,如有色金属冶炼工业中,需对温度、成分等多种参数进行多点测量,现场电磁干扰严重,环境温度高,传感器数量多,且到控制系统的传输距离远。本文提出一种基于FPGA的智能传感器信号采集与光纤传输解决方案,通过设计可扩展的多输入传感器数据采集模块,进行多路数字量及模拟量信号的采集,并通过时分复用技术,将多个传感器数据通过单光纤传输至主控制器,该系统可提高系统集成度,简化布线,并提高抗干扰性能。

1 系统总体方案

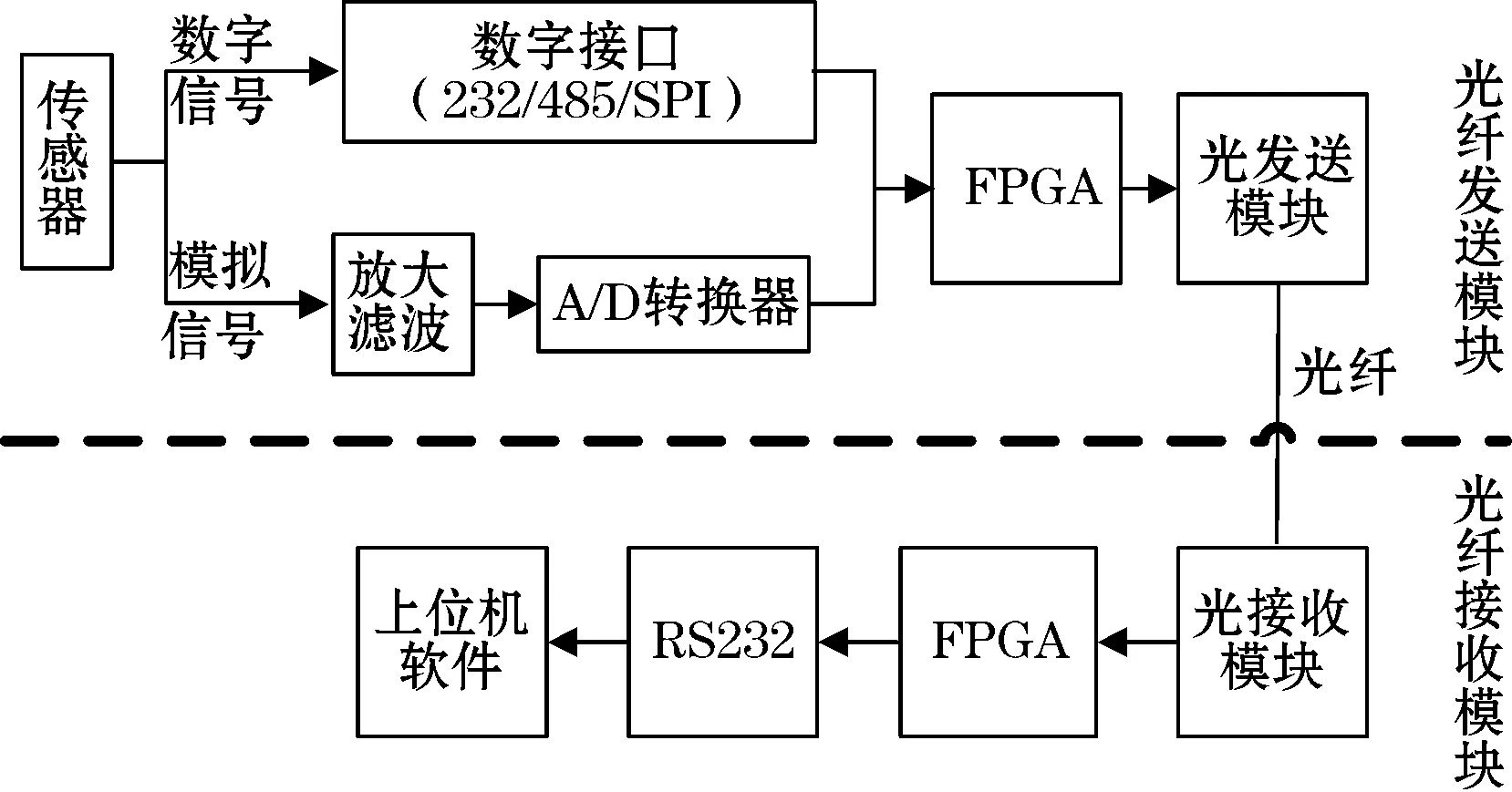

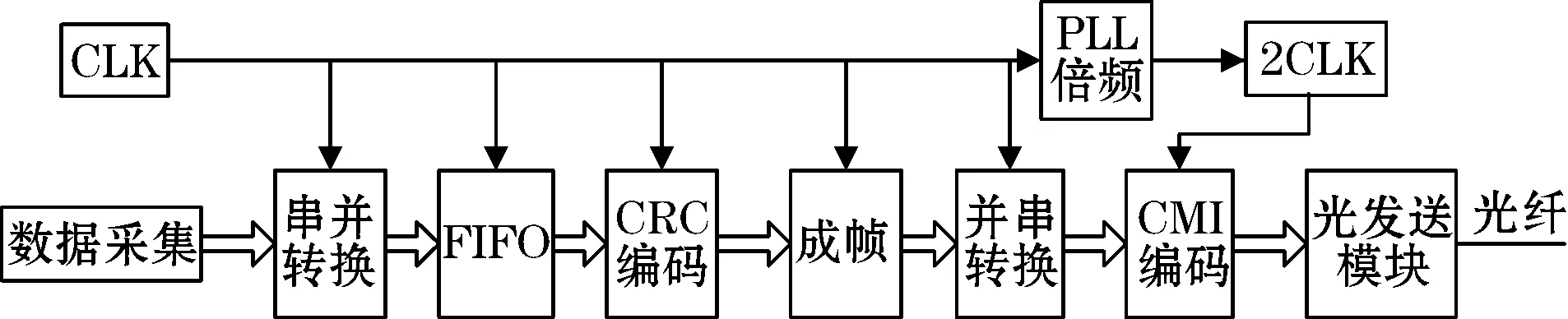

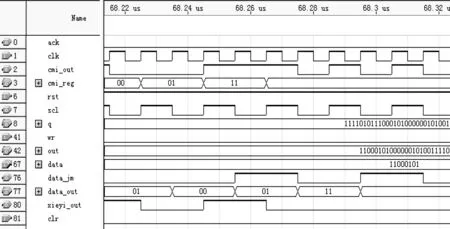

本系统核心功能为采集数字量、模拟量传感器信号,经电/光转换后,通过光纤进行传输。系统处理核心基于FPGA,具有配置灵活、可扩展的特点。模拟量传感器信号兼容4~20 mA和0~5 V的标准工业信号,同时提供数字I/O,计数器等接口,也可根据应用需要,兼容CAN总线或RS485信号。因此系统接口模块可分为数字和模拟信号接口两部分,数字接口包括开关量、RS232/485、SPI等,模拟接口由信号调理和A/D转换电路构成。系统总体方案如图1所示。

图1 光纤传输系统总体方案

其中光纤传输流程为:采集的传感器信号通过FPGA进行信号处理和编码操作,得到适合光纤传输的数字码流信号,该信号通过光发送模块实现电/光转换,并通过光纤传输。在接收端,光接收模块将收到光纤信号进行光/电转换,经时钟提取、解码等处理后,得到传感器数据,然后可通过RS232送至上位机或经总线接口接入工业网络。

2 系统实现的关键技术

2.1 时分复用技术的原理与实现

为使多路信号互不干涉地在同一信道上传输,需采用复用技术。在时分复用系统中,多路信号在时间上被离散化,相当于对时域进行分割,信号在时域中互不重叠[5]。

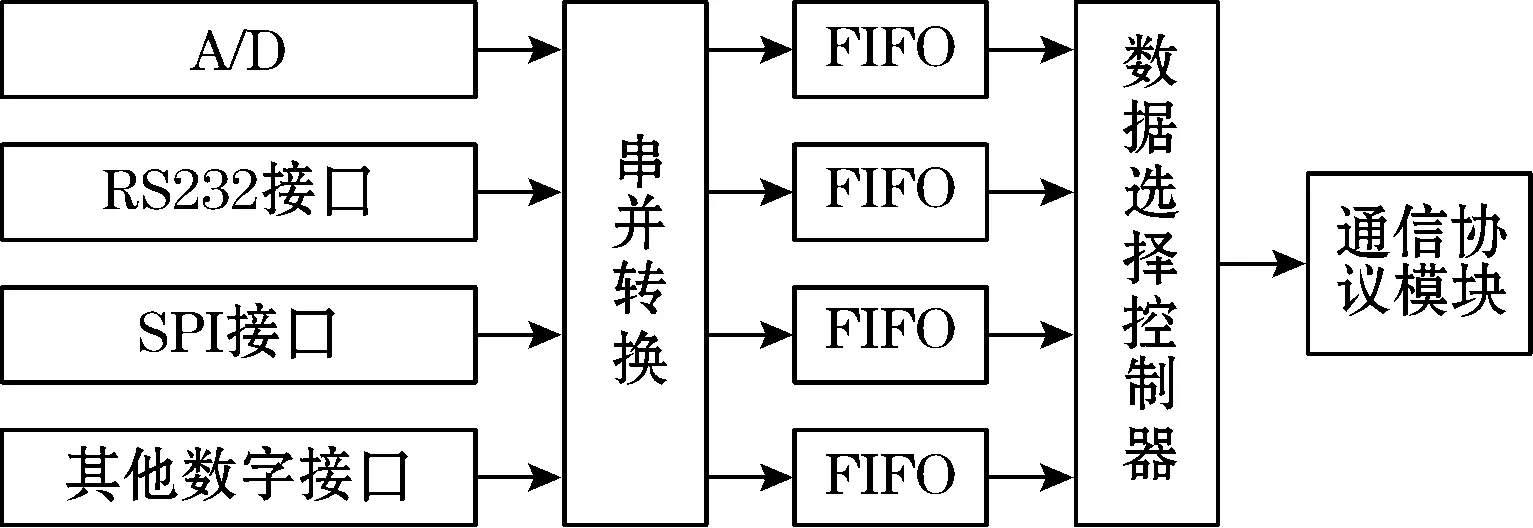

该系统需实现多路传感器数据采集,故需将多路信号进行有序传输。根据乒乓操作方法[6],采集到各传感数据先存入各自FIFO,当目前处理的数据完成电/光转换并发送后,再通过建立数据选择控制器并加入延时,依次从各FIFO中读取数据。这样既保证各传感器之间数据不发生冲突,又能实现单光纤传输的时分复用,形成多个数据的有序传输。另外在每帧传输后留有时隙,当接收端收到数据校验错误或者丢帧时可在该时隙中进行单独查询。其过程如图2所示。

图2 时分复用模块框图

2.2 光纤通信编码方式与实现

在数字光纤传输系统中,一般不直接传输普通数字信号,由于普通数字信号有直流分量,且有长连“0”、长连“1”的情况存在,不利于误码检测,因此需要先通过码型转换将普通二进制码转换成适合光纤传输的线路码[7]。本系统采用传号反转码(CMI,Coded Mark Inversion)编码方式。

2.2.1 CMI编码模块设计

CMI码是一种两电平非零码,其编码规则为:“1”码交替用“00”和“11”两位码表示;“0”码固定用“01”表示[7]。根据上述编码规则,CMI编码模块由码识别器、“1”码编码器、“0”码编码器、“1”码输出选择器、时序控制和输出模块6部分组成。各模块关系如图3所示。

图3 CMI编码原理框图

由于“1”码交替用“00”、“11”表示,在设计“1”码编码器的时候需要加入一个输出状态记忆单元,这个单元是通过D触发器实现的,即D触发器每接收到一个“1”码就翻转一次,来实现记忆“1”码的编码状态[8]。由于CMI码是一种1B2B(1位信息,2位码元)串行输出码,码元数量提高1倍,故Verilog HDL程序中需要把输出模块中的数据进行并串转换,并在2倍的初始时钟频率下进行输出。

2.2.2 CMI解码模块设计

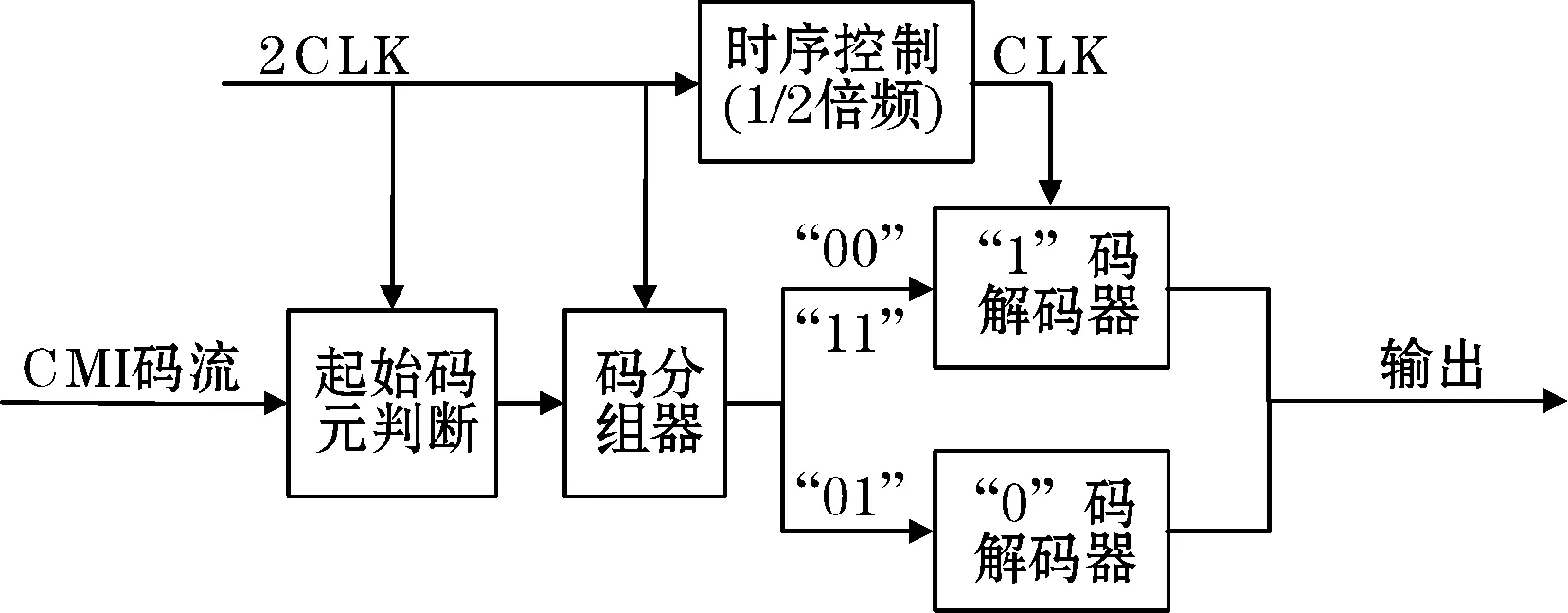

在CMI解码器的设计中,其重点是判断接收到的CMI码流的起始位,从起始位开始把CMI码流的两个码元分为一组进行判断,若为“00”或“11”,则输出“1”;若为“01”,则输出“0”。根据上述解码规则,CMI解码器主要由起始码元判断模块、码分组器、“1”码解码器、“0”码解码器和时序控制模块5部分组成,其译码原理框图如图4所示。

图4 CMI解码原理框图

3 系统软硬件设计

3.1 系统硬件组成

该系统以FPGA为主控芯片,选用型号为CycloneII系列的FPGA-EP2C8T144Q8NA。FPGA内部功能模块通过Verilog HDL硬件描述语言实现。其核心功能模块包括时分复用模块、数据传输协议模块、CMI编解码模块和位同步时钟提取模块。另外为提高数据处理速度,设计了数据串并转换模块,把串行数据转换为并行数据在FPGA内部进行处理,可提高数据处理效率。由于光纤传输的是串行数据,故在数据成帧后需进行并/串转换,再将所得串行数据进行CMI编码以输入光发送模块,并通过光纤发送。

系统外围接口主要包括数字信号接口、模拟信号接口和光信号收发接口。其中,数字信号采集接口包括RS232、RS485和SPI等通讯接口,以及FPGA预留的I/O口,以方便进行扩展,其中与PC上位机的通讯采用RS232;模拟信号采集接口将传感器输出信号进行信号调理后进行A/D转换,将数字信号送入FPGA;光信号收发接口主要负责光/电、电/光转换。光收发模块分别选取HFBR2416和HFBR1414。产生光波长为850 nm,采用多模光纤进行传输,理论最远传输距离为2.7 m。

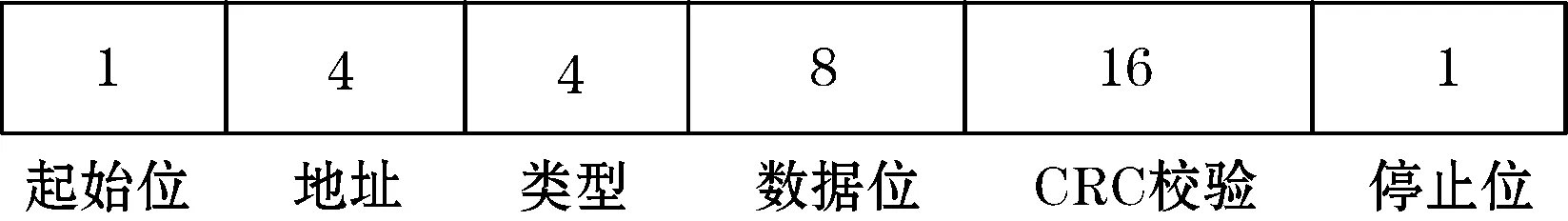

3.2 数据传输协议模块设计

为使接收端能够准确判断有效数据的起止位,需要进行传输协议的制定。该系统定义的数据传输帧为34位,第一位和最后一位分别为起始位和终止位,起始位和终止位之间有4位地址位,4位数据类型位,8位有效数据,16位CRC校验码。起始位为“0”,停止位为“1”,空闲时信道一直处于高电平,当检测到低电平,即起始位“0”时表明有效数据帧开始传输,接收端立即进行CMI解码、解帧、校验、提取有效数据等操作。从起始位起,接收端设置计数器开始计数,当计数器的值为34时并且最后一位为“1”,表明1帧数据传输完毕。光纤中传输的数据帧格式如图5所示。

图5 数据传输协议帧格式定义

3.3 CRC编码校验模块设计

循环冗余码校验(Cyclical Redundancy Check)简称CRC校验,利用除法及余数的原理作错误侦测。系统在应用时,发送端把计算出的CRC数值连同数据一起发送出去[9],接收端对采集数据进行CRC数值计算,与接收到的CRC数值对比,以此来进行误码检测,本系统应用的是CRC16码。

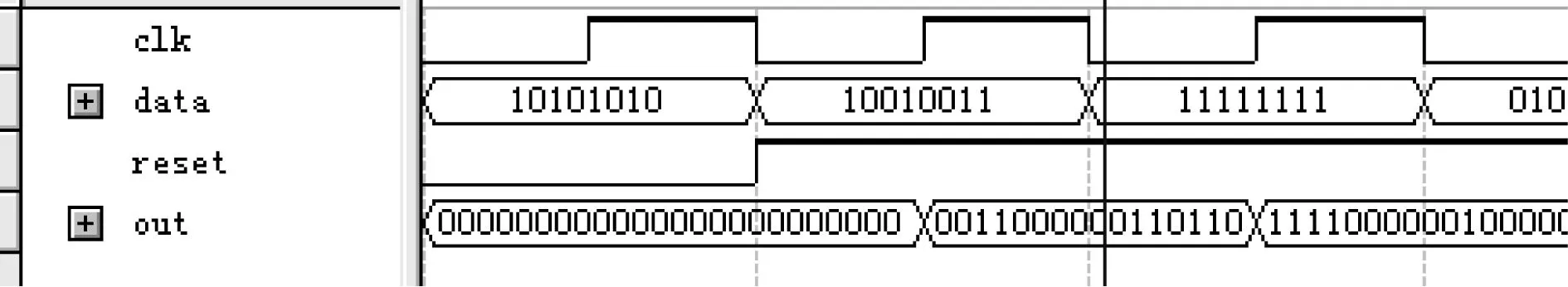

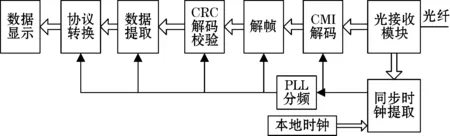

通过Verilog HDL硬件编程语言对8位并行数据进行CRC编码,其仿真波形图如图6所示。data为通过串并转换的8位并行数据,out为CRC16码,由8位数据和16位CRC码组成,共24位。clk为系统时钟,reset为复位信号。通过功能仿真波形可知CRC编码模块满足设计要求。

图6 CRC编码功能仿真图

3.4 位同步时钟提取模块设计

在数字通信系统中,时钟同步非常重要。同步指收发两端的信号在时间上保持步调一致,是保证数字通信系统有序、准确、可靠工作的前提条件[10]。位同步技术是同步技术中最基本的同步,是从接收信号中获取位同步信息,使此时脉冲序列和接收码元起止时刻保持正确关系的技术。

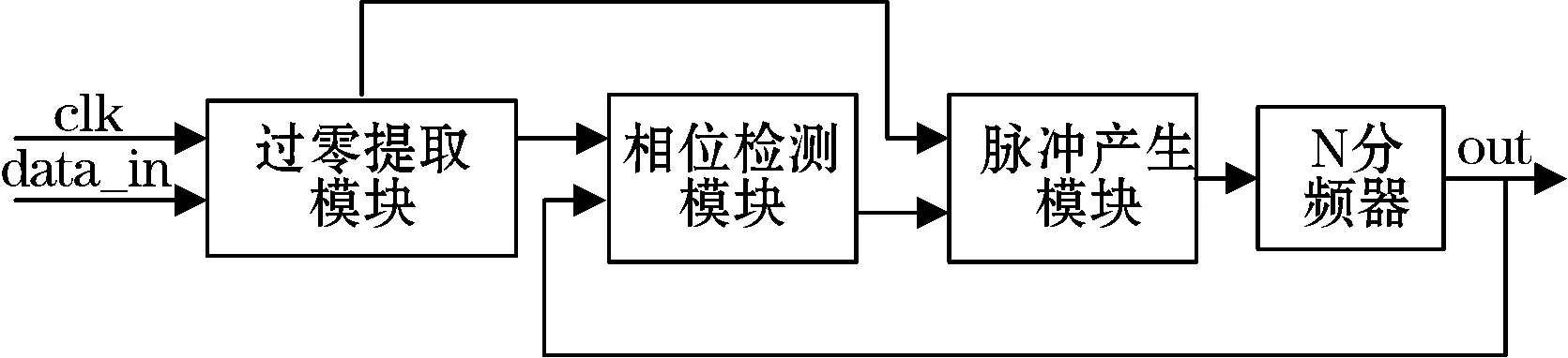

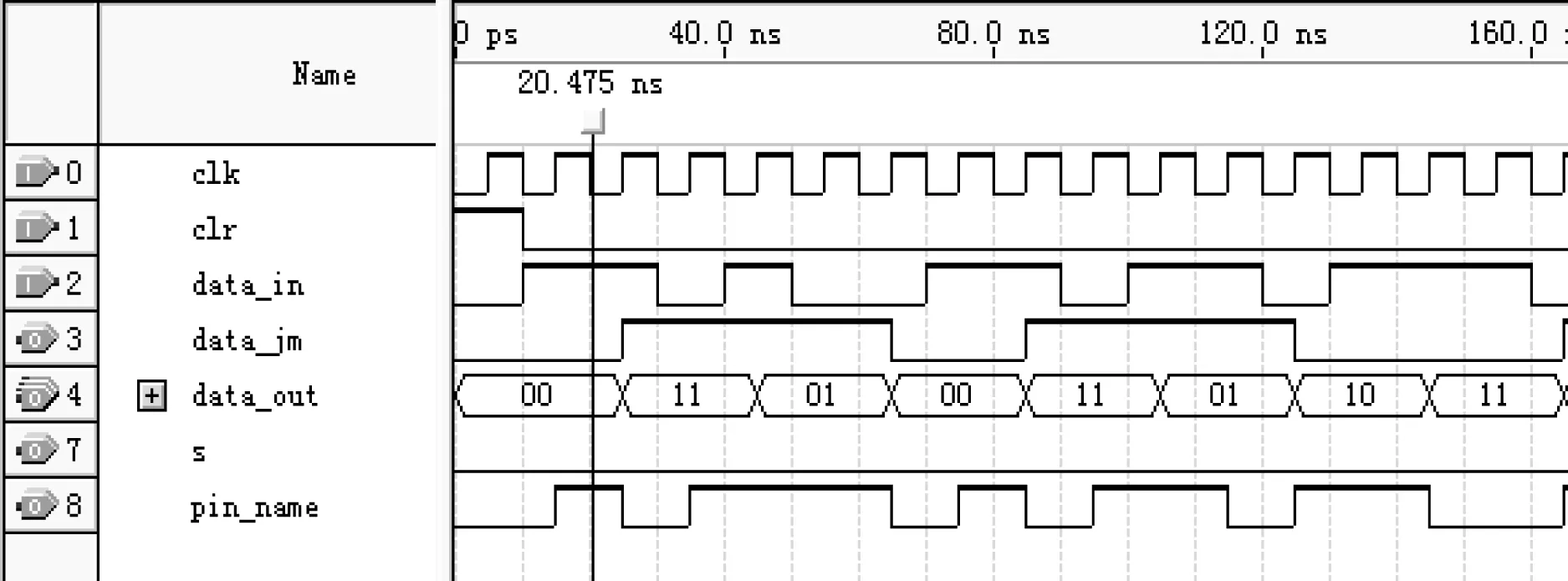

图7是位同步时钟提取模块框图,由4部分组成,分别为过零提取模块、相位检测、N分频器和脉冲产生模块。其中data_in为系统输入的串行数据;clk为串行数据码元时钟2倍频信号,通过锁相环技术获取[11];out是系统产生的与串行输入码元同步的脉冲信号,即位同步时钟。

图7 位同步时钟提取模块框图

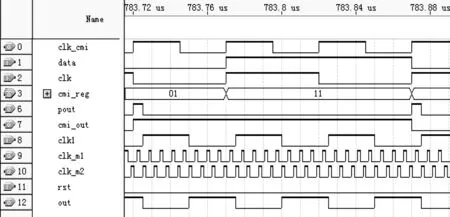

其工作原理为:用过零提取模块检测出数据流中的上升沿和下降沿,然后将输出脉冲送给相位检测模块,相位检测模块的另一输入端是系统产生的位同步时钟,由此构成闭环控制系统,达到实时动态补偿效果。相位检测模块将检测出输入码元与提取的同步时钟相位进行比较,可能存在超前或者滞后。当输入码元超前于提取的同步时钟时,相位检测模块输出端q=1,若滞后则q=0,q值决定脉冲发生器给计数器正脉冲还是负脉冲。模块的功能仿真图如图8所示,在10 ms时位同步时钟达到了动态平衡。可满足使用要求。

图8 位同步时钟提取功能仿真图

3.5 光纤传输系统总体功能仿真

3.5.1 光纤发送模块功能仿真

系统发送模块框图如图9所示。为方便观察功能仿真结果,把组成发送模块的各子模块输出均添加了输出管脚。数据采集接口采集数据后,首先进行并串转换,然后输入到FIFO模块中,当发出读FIFO命令时,从FIFO中读取一组数据,并进行CRC校验编码,之后将数据打包成帧、并/串转换以及进行CMI编码。该模块的功能仿真如图10所示,其时序符合功能要求。

图9 光纤发送模块框图

图10 发送模块功能仿真图

3.5.2 光纤接收模块功能仿真

系统接收模块框图如图11所示。当接收到光纤中传输的数据后,先进行时钟位同步操作,保证接收端数据的时钟与发送端发送的CMI码流位同步,然后判别有效数据帧的起始位,进行CMI解码、串并转换、CRC校验等操作后,提取有效数据进行显示。为提高数据处理速度,接收模块中的各子模块之间为并行数据,故数据提取后需将并行数据转换为串行数据,以通过串口与上位机通讯。接收模块功能仿真如图12所示,图中时序表明可以实现预期功能。

图11 接收模块框图

图12 接收模块功能仿真图

4 结论

本文设计了一种面向传感器输出端的高集成度数据采集与光纤传输系统,可满足在强电磁干扰等恶劣条件下的远距离传输要求,传输数据可靠,误码率较低,应用领域较为广阔。若应用于恶劣工业现场领域,可提高信号传输可靠性,抗干扰性,减小电磁辐射,也可直接用于机电一体化设备,可大幅度减少布线,提高电磁兼容性能。另外,系统硬件电路板留有充分的I/O资源,具备扩展能力,对FPGA内数据处理模块稍加修改即可应用于不同接口的传感器数据采集。

从目前有线通信系统的发展趋势看,本文设计的基于FPGA的多传感器集成光纤传输系统还需要从以下几个方面来提升其性能:

(1)提高系统的传输过程中的误码纠错能力,增加通信系统的可靠性;

(2)充分利用FPGA内部资源,使一套通信系统能够完成更多传感器数据的传输,以降低成本;

(3)应用通信效率更高的编码方式,提高通信系统的实际传输带宽,以满足实时性要求。

[1] 韩红霞,郭劲,曹文华,等.基于FPGA高速视频信息传输方案设计.电子器件,2005,28(4):820-822;854.

[2] 汪精明.基于FPGA的传像光纤束图像预处理器.计算机技术应用,2010(4):42-44.

[3] 杨国栋,梁自泽,李恩,等.一种光纤现场总线通讯系统的分析与设计.高技术通讯,2009,19(7):754-759.

[4] 魏丰,潘小虎,曾男,等.光纤CAN总线集线器及其组网技术研究.仪器仪表学报,2011,32(12):2839-2844.

[5] 刘颖.数字通信原理与技术.北京:北京邮电大学出版社,1998.

[6] 吴继华,蔡海宁,王诚.Altera FPGA/CPLD设计(高级篇).北京:人民邮电出版社,2011.

[7] 樊昌信,曹丽娜.通信原理.2版.北京:国防工业出版社,2012.

[8] 解金山,陈宝珍.光纤数字通信技术.北京:电子工业出版社,2002.

[9] 王新梅,肖国振.纠错码—原理与方法.西安:西安电子科技大学出版社,2003.

[10] 牛立强,孙洪伟,王宝兴.一种光通信系统中时钟提取电路的设计及实现 .电子科技,2008,21(12):28-30.

[11] 吴继华,蔡海宁,王诚.Altera FPGA/CPLD设计(基础篇).北京:人民邮电出版社,2011.

Multi-sensor Integrated Optical Fiber Transmission System Based on FPGA

YUAN Jun-jie,HU Tian-yu

(College of Mechanical and Electrical Engineering,North China University of Technology,Beijing 100144,China)

To achieve the high integration and high-speed of transmission system directly from the sensor interface to the light interface,a multi-sensor integrated optical fiber transmission system based on FPGA was proposed.The hardware platform of the optical fiber transmission system was built with the simple architecture based on FPGA and optical transceiver module.And on this basis,the intelligent software of the system was developed.The system realized the data acquisition and transmission of analog and digital-interface’s sensor.By applying the principle of time division multiplexing,the multi-channel sensor signal by single fiber was realized.The experimental results indicate that the system has the ability to detect the error code.The system is very suitable for industrial field sensor signal transmission of long transmission distance and high real-time in complex environment.

fiber optic communication;digital optical fiber transmission system;FPGA;time division multiplexing;coded mark inversion encoding and decoding

北京市教委科研计划面上项目(KM201210009003)

2014-02-16 收修改稿日期:2015-01-07

TP23

B

1002-1841(2015)03-0043-04

袁俊杰(1980—),博士,副教授,主要研究方向为测控技术、传感器设计与应用。E-mail:yuanjj@ncut.edu.cn 胡天宇(1987—),硕士,主要研究方向为光纤通信原理与应用。E-mail:hutianyu124@163.com