一种窄边框的液晶显示面板设计

2015-05-10苏子芳

张 军,苏子芳,关 星,赵 哲

(昆山龙腾光电有限公司,江苏 昆山 215301)

1 引 言

随着工艺、设备、材料等技术的不断发展,薄膜晶体管液晶显示技术(TFT-LCD:Thin Film Transistor Liquid Crystal Display)不断突破技术限制、简化制造工艺以降低成本。同时因应市场对更多媒体显示器件的低功率消耗、快速响应、高像素密度(高分辨率)、宽视角及便携性的需求,不断有新的技术被引入TFT-LCD设计中以满足市场需求、拓展 TFT-LCD的应用范围[1-3]。

就便携性而言,一方面要求TFT-LCD显示面板趋向轻薄化并开拓了玻璃薄化的新市场。另一方面随着便携性设备(移动电话,PDA等)应用显示屏面积的不断扩大,为在不增加设备外形尺寸的前提下增加设备的可显示面积,市场亟需TFT-LCD面板设计的技术革新,减小TFT-LCD面板非显示区的面积。因而各种各样的新技术被开发以使TFT-LCD窄边框化。

传统TFT-LCD面板栅极(Gate)线路采用配线从驱动芯片(IC)导入信号使TFT开启,将显示信号输入到像素单元完成画面显示。由于每一条配线对应一行栅极电路,配线条数较多,占用空间较大。为响应市场窄边框高解析度高分辨率产品需求,集成栅极驱动电路(GIA,gate driver in array)技术应运而生[4]。GIA 电路具有减少外围IC数量及其连线、降低显示模组成本、提高显示面板分辨率和弯折度等优点引起了广泛的兴趣[5]。但在使用GIA电路的同时会增加显示器的总体功耗[6],并且GIA电路信赖性较差,长期工作下电路发生异常的风险上升。因此,迫切需要新的应用于TFT-LCD产品的窄边框设计。

2 现有的栅极线路设计技术

2.1 传统栅极线路设计

图1为传统栅极线路设计图。假设其分辨率为1280×720,则有720条栅极走线在面板的左右两侧,单侧为360条栅极走线,按照每条栅极走线宽5μm,间隔5μm来计算,单侧栅极走线的宽度要有3.6mm。则分辨率为1 280×720的手机面板使用传统栅极走线方式时,左右两边非显示区宽度要大于3.6mm。这样的产品设计不能满足市场的需求。

图1 传统栅极线路设计图Fig.1 Traditional gate design

2.2 使用集成栅极电路(GIA)缩小边框

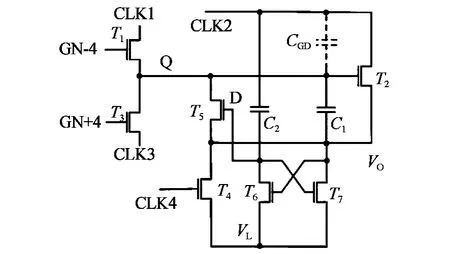

现有技术通过GIA单元电路来取代栅极走线,从而实现窄边框显示面板。图2为一种GIA单元设计原理图,其由4部分构成:预充电部分、自举上拉部分、下拉部分和低电平维持部分[7-8]。其中,预充电部分包括T1;自举上拉部分包括T2;下拉部分为T3和T4;低电平维持部分包括C1,C2,T5~T7。

图2 一种GIA单元设计原理图[7]Fig.2 A GIA circuit design[7]

GIA电路通过移位逐级打开的方式减少了外围驱动IC数量及栅极连线,从而达到减小非显示区域面积及面板窄边框化的目的。然而,GIA电路需要的TFT数目较多,生产过程中的良品率较难控制;并且由于多个高电压信号的使用使得显示面板的整体功耗上升;同时,长时间的偏压工作及高频率的切换使得GIA电路中的TFT寿命变短,长时间使用时电路的稳定性受到影响。

3 新型栅极线路设计

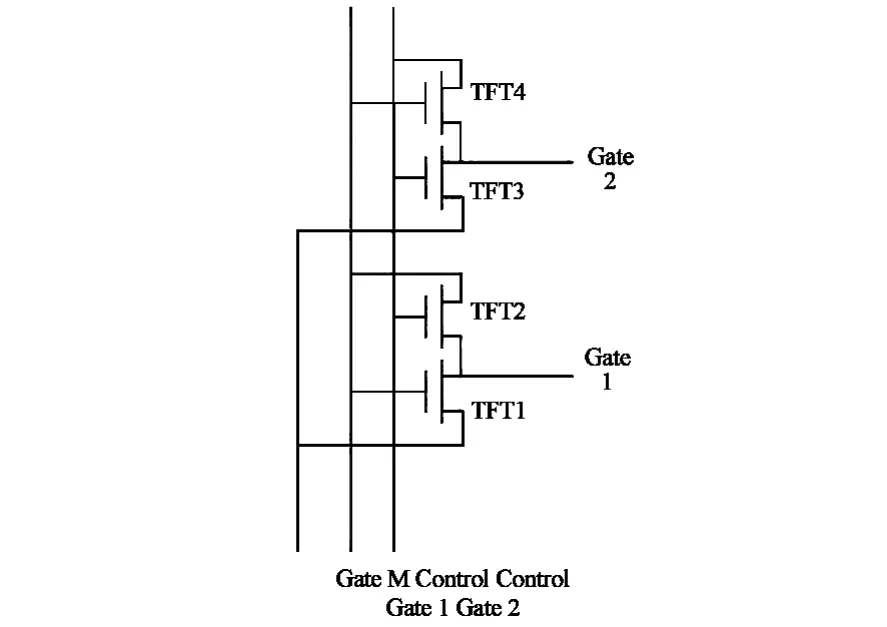

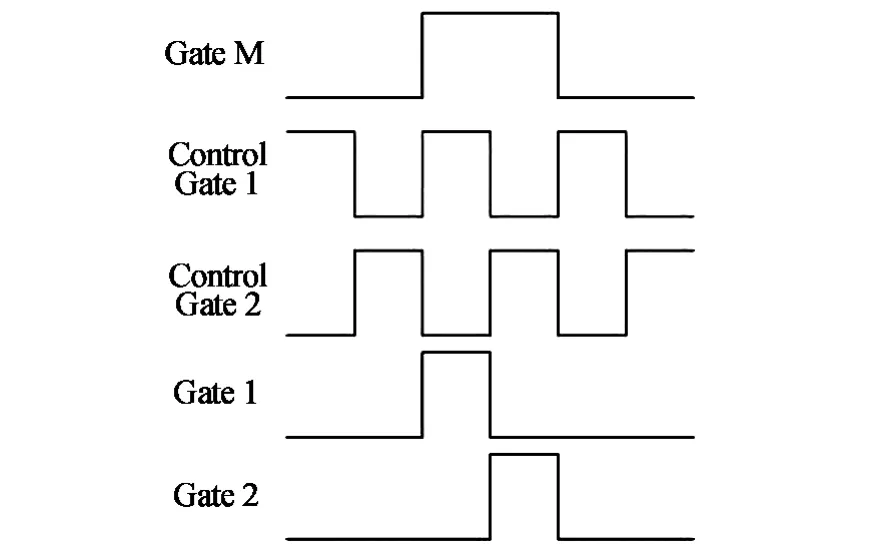

本文提出一种新的栅极驱动电路设计用以减小显示面板上非显示区域的面积(窄边框)并一定程度上提升系统的稳定性。其设计原理及使用的时序如图3和图4。Gate M走线打开的时间为Gate Odd/Even打开时间的2倍;当 Gate M 为高电平的前1/2时间时,Control Gate 1为高电平,TFT1处于打开状态,将Gate M上的高电平充入Gate 1,Gate 1控制的TFT全部打开,信号电压充入其对应的像素单元;当Gate M为高电平的后1/2时间时,Control Gate 1电压为低电平TFT1停止工作,同时Control Gate 2为高电平,TFT2为打开状态,此时Gate 1会充入Control Gate 1上的低电平,从而使Gate 1这条栅极关闭,像素上的电压保持原充入的电压。与此同时当Control Gate 2由低电平变为高电平时,TFT 3打开,Gate 2会充入 Gate M 的高电平,Gate 2控制的TFT全部打开将信号电压充入对应的像素单元,其工作原理与Gate 1相同。当Gate M为低电平时,是 Gate 1与 Gate 2通过 TFT1、TFT2、TFT3、TFT4充入的始终是低电平,使得其控制的TFT都能保持关断状态,这两条Gate对应的显示单元的像素电压处于保持状态,直到下一次Gate M变为高电平。

图3 新型栅极电路设计Fig.3 New gate design

图4 新型栅极电路设计使用的时序图Fig.4 Timing ofnew gate design

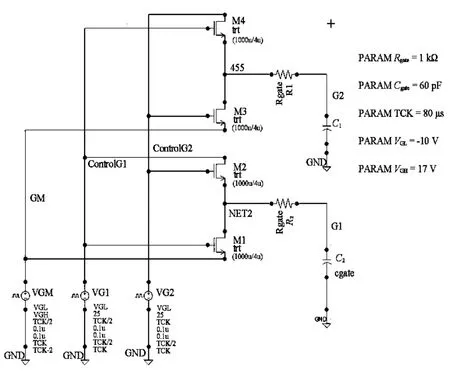

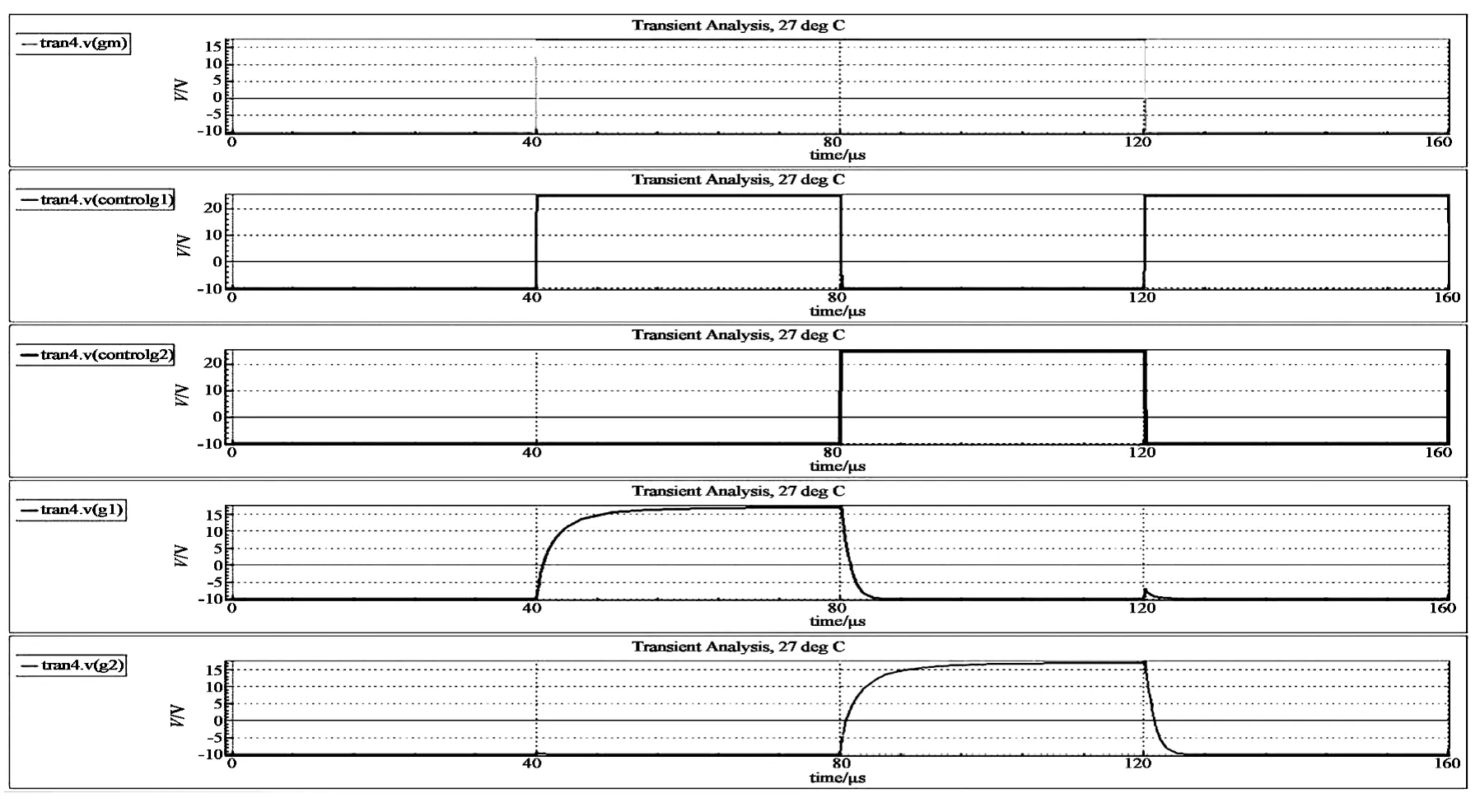

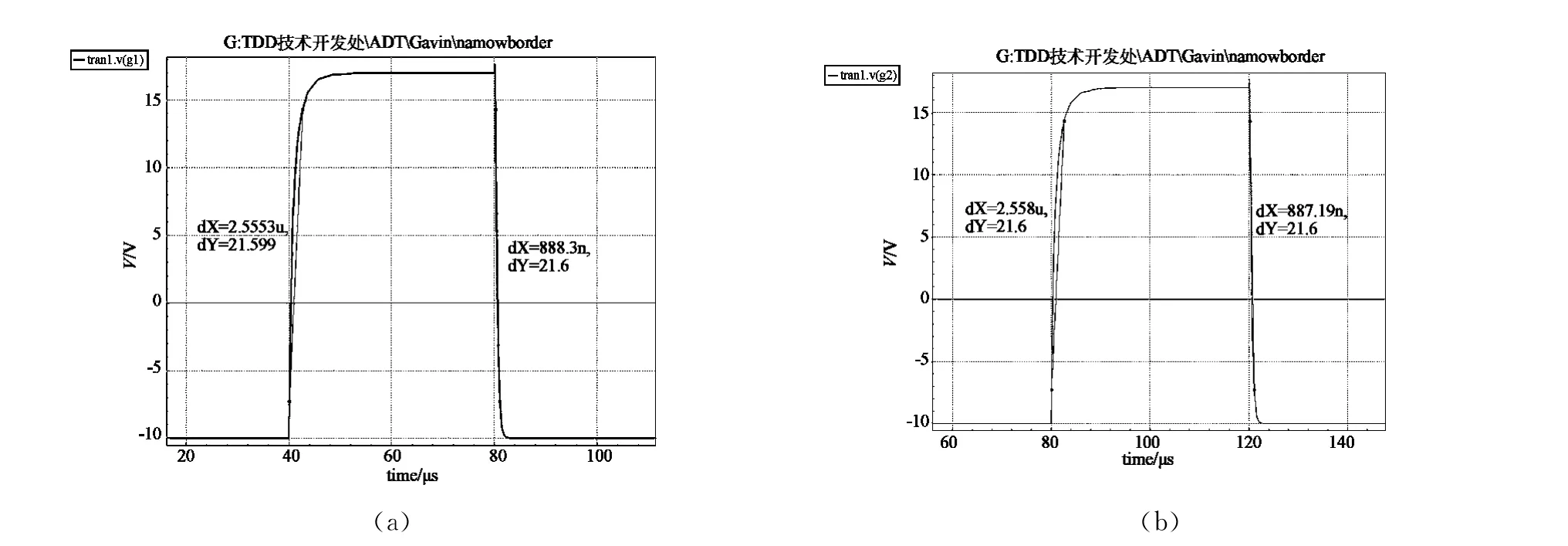

使用上述电路连接负载栅极走线组成模拟电路如图5。使用Gateway软件对图5的电路进行仿真分析。设定每条负载栅极线的阻抗为1kΩ,电容为60pF。每一帧画面开启时间为16.67ms,Gate M 高电压的时间为一个 TCK,80 μs。VGL取-10V,VGH取17V。使用 TFT的W/L为3 000μm/4μm。模拟结果量测波形如图6;栅极信号的上升沿和下降沿量测波形如图7,其中(a)为 Gate 1的波形,上升沿延迟2.6 μs,下降沿延迟0.9μs,总延迟时间为3.5μs;(b)为 Gate 2的波形,上升沿延迟2.6μs,下降沿延迟0.9μs,总延迟时间为3.5μs。在VGL关态时栅极信号的噪声电压为2.5V,持续时间仅3μs,如图8。实验证明新型栅极驱动电路可以实现像素节点的正常充放电并完成显示面板的正常显示。

图5 模拟电路Fig.5 Circuit for simulation

图6 模拟栅极电路波形Fig.6 Simulated waveform of gate driver

图7 上升沿和下降沿时间量测波形Fig.7 Waveform of rising and falling time

图8 耦合效应下的噪声Fig.8 Noise of coupling effect

4 结 论

根据市场对LCD面板高分辨率高解析度、窄边框的要求,提出了一种新型栅极线路的走线方法,减少了栅极走线占用的空间,实现了显示面板的窄边框化。模拟结果表明,传统的栅极走线加入本发明电路后,量测的栅极波形无明显迟豫,且噪声较小,可以实现像素节点的充放电,完成画面的正常显示。由于需要增加两条控制走线及4个TFT,为了使栅极高电压信号无失真,TFT需要较大的W/L,这就需要占用一部分空间,但并不影响总体缩减边框的效果。

[1] Nakajima S,Sugiyama Y,Ichinose H,et al.Novel liquid-crystal materials with high birefringence and low rotational-viscosity for the field-sequential color TN-LCDs[J].SID Symposium Digest of Technical Papers,2000,31(1):242-245.

[2] 董小春,杜春雷.负性光刻胶刻蚀工艺研究[J].光子学报,2004,32(12):1422-1425.Dong X C,Du C L.Study on lighography of negative resists[J].Acta Optica Sinica,2004,32(12):1422-1425.

[3] Lee S H,Kim H Y,Lee S M,et al.Ultra-FFS TFT-LCD with super image quality,fast response time,and strong pressure-resistant characteristics[J].Journal of the Society for Information Display,2002,10(2):117-122.

[4] Moon S H,Lee Y S,Lee M C,et al.Integrated a-Si:H TFT gate driver circuits on large area TFT-LCDs[J].SID Symposium Digest of Technical Papers.Blackwell Publishing Ltd,2007,38(1):1478-1481.

[5] Oh J H,Hur J H,Son Y D,et al.2.0inch a-Si:H TFT-LCD withlow noise integrated gate driver[J].SID Symposium Digest of Technical Papers,2005,36(1):942-945.

[6] Hwang I,Moh S,Lee M C,et al.55.4:Design of integrated a-Si gate driver circuits for low power consumption[J].SID Symposium Digest of Technical Papers,2008,39(1):842-845.

[7] Liao C,He C,Chen T,et al.Implementation of an a-Si:H TFT gate driver using a five-transistor integrated approach[J].Electron Devices,IEEE Transactions ON,2012,59(8):2142-2148.

[8] Choi J W,Kwon M S,Koo J H,et al.Noble a-Si∶H gate driver with high stability[J].SID Symposium Digest of Technical Papers,2008,39(1):1227-1230.