基于STM32和CPLD的TFT-LCD显示控制器设计

2015-05-10尤卫卫冒建亮

尤卫卫,冒建亮,叶 桦

(东南大学 自动化学院,江苏 南京 210096)

1 引 言

液晶显示器由于其轻薄、便携、高分辨率等优点已被广泛应用到生活、工业、军事等各种场合。TFT-LCD显示器作为液晶显示器中一类重要的代表,具有体积小,功耗低,显示品质优良等诸多优势,已经成为当前桌面显示的主流。虽然TFT-LCD显示效果极佳,但由于控制时序相对复杂,其控制一直是大家研究的重点[1-2]。目前对TFT-LCD的控制方式主要有3种:

(1)使用专用控制芯片,但此方式易受器件断档影响,并且不利用技术移植;

(2)使用内置TFT-LCD控制器的STM32,如ARM9等,此方式适用于高端显示领域,成本较高;

(3)使用FPGA或CPLD进行 TFT-LCD的控制器设计,利用此方式设计灵活性强、可移植性高,且器件性价比高。

比较3种方案,本文选择灵活性强、可移植性高,且器件性价比高的第三种方案来设计控制器[3]。

2 TFT-LCD显示控制器的整体架构

图1为液晶屏显示系统的系统框图。其中,主控芯片STM32[4]内部制定了与CPLD间的通讯协议,主要用于实现在LCD上的各类写操作指令,通过Intel8080总线将待显示信息传送给CPLD。作为控制器的核心元件,CPLD主要实现三个模块的功能[5]:

(1)协议解析模块:CPLD接收控制器STM32发出的控制指令,实现对8080总线通讯协议的解析,主要包括待写数据模式,待写数据坐标以及待写数据RGB颜色。

(2)SRAM 读写控制模块:CPLD 在 TFTLCD屏显消隐区间,根据提出的数据坐标及RGB颜色,将相应值写入SRAM相应地址。在TFTLCD屏显有效区间时,将上述数据按照时序依次读出,完成TFT-LCD的显示驱动。

(3)LCD时序驱动模块:根据LCD显示时序,实现液晶屏的显示驱动。

3 TFT-LCD显示控制器的设计

3.1 STM32与CPLD间通信协议

STM32内部实现了底层接口函数及上层界面函数,底层接口函数主要实现通讯协议的制定,包括用于界面显示的各类函数的实现。主要包括:单点写、多点写、8点带背景写与8点不带背景写命令。各命令具体操作如下:

(1)单点写

单点写主要是为了实现一些不易绘制的图形,如圆、三角形等,也可用于显示完整的图片。STM32内部根据指定的时序规则,依次发送指令:选择单点写模式→待显示像素点行、列地址→待显示像素点颜色。

(2)多点写

多点写主要用于绘制直线、矩形等,也可用于局部图形的填充。STM32内部根据指定的时序规则,依次发送指令:选择多点写模式→待显示图形起始点行、列地址→待显示图形长度→待显示图形颜色。

(3)8点带背景写

主要用于字符的覆盖显示,可绘制任意像素为8N×8N的字符。STM32内部根据指定的时序规则,依次发送指令:选择8点带背景写模式→待显示字符起始行、列地址→待显示字符前景色→待显示字符背景色。

(4)8点不带背景写

主要用于字符的层叠显示,可绘制任意像素为8N×8N的字符。STM32内部根据指定的时序规则,依次发送指令:选择8点不带背景写模式→待显示字符起始行、列地址→待显示字符前景色。

根据上述4种操作,STM32可以便捷地进行各类图文的绘制,并将相应的指令传送给CPLD对通讯数据进行解析,实现TFT-LCD的显示驱动。

3.2 TFT-LCD显示驱动设计[6-8]

显示器的驱动主要由CPLD实现,包括LCD时序驱动、通讯协议解析和SRAM读写控制,如图2所示。CPLD接收控制器STM32发出的控制指令,提取待显示点的坐标与RGB数据,并在TFT-LCD屏显消隐区间,将相应数据写入SRAM相应地址。在TFT-LCD屏显有效区间时,将相应数据按照时序依次读出,完成TFTLCD的显示驱动。

图2 TFT-LCD显示驱动框图Fig.2 Driving chart of TFT-LCD display

3.2.1 通讯协议解析模块

CPLD对STM32的通讯协议解析,按照先取指令后取数据的方式进行。当STM32发送控制指令时,控制线RS为0,发送数据指令时,控制线RS为1,每发送完对应的指令,发送相应的数据。因此,通过判断RS由0到1的上升边沿,此时总线上数据状态稳定,即可读取指令至CPLD中的寄存器;同理,当检测到RS由1到0的下降边沿时,可以根据接收到的控制指令,将相应的数据存放入对应的寄存器中,进而在TFT-LCD数据写有效时,进行相应的写屏操作。

写屏操作具体指STM32用于图文绘制的单点写、多点写、8点带背景写与8点不带背景写的驱动程序,采用有限状态机模式,主要分为两大类:第一类是输出只和状态有关,与输入无关,即Moore型状态机;第二类是输出和输入、状态有关,且次态也与输入和当前状态有关,即 Mealy型状态机。本设计中采用的是Mealy型状态机,各部分对应状态操作如下:

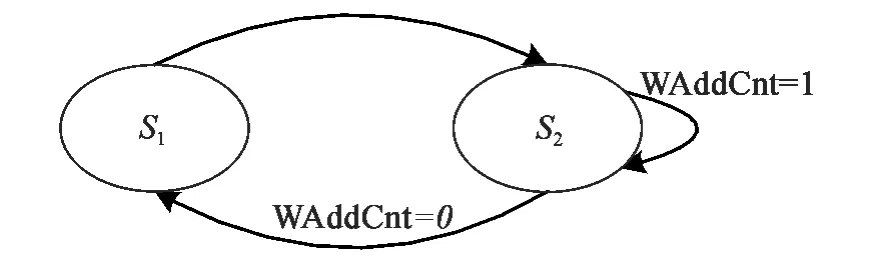

(1)清屏操作

设定状态S1:寄存器清零操作;S2:清屏操作。状态图如图3所示。其中,WAddCnt为写屏操作完成标志。

图3 清屏操作状态图Fig.3 State chart of screen clearing operation

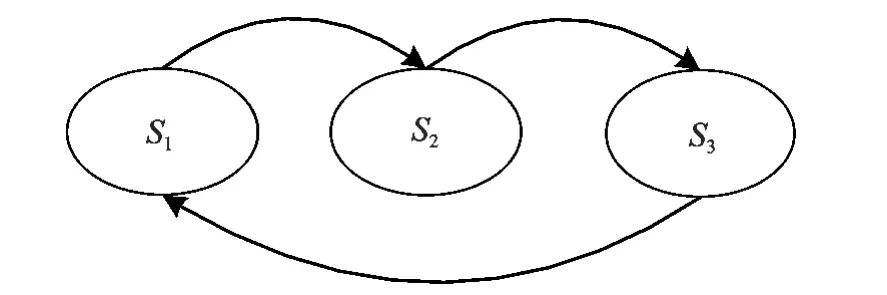

(2)单点写

设定状态S1:等待数据稳定;S2:写单点操作,S3:寄存器清零操作。状态图如图4所示。

图4 单点写操作状态图Fig.4 State chart of single point writing operation

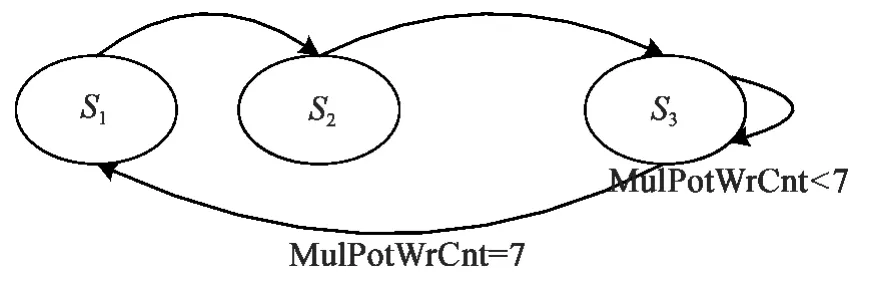

(3)多点写

设定状态S1:等待数据稳定;S2:写起始点操作;S3:写剩余长度点操作。状态图如图5所示。其中,MulPotWrCnt为写计数器,MulPotLength为多点写长度。

图5 多点写操作状态图Fig.5 State chart of multipoint writing operation

(4)8点带背景写

设定状态S1:等待数据稳定;S2:写起始点操作;S3:写其余7点操作。状态图如图6所示。其中,MulPotWrCnt为写计数器;状态S2和状态S3中,对字模数据的操作为:0写背景色,1写前景色。

图6 8点带背景写状态图Fig.6 State chart of 8points with background writing operation

(5)8点不带背景写

设定状态S1:等待数据稳定;S2:写起始有效点操作;S3:无效点计数清零操作;S4:写其余有效点操作。状态图如图7所示。其中,8Addr[7]为字模最高位,每个时钟周期左移1位;8AddrCnt为单字模中两有效点间无效点计数器;MulPotWrCnt为写计数器,8AddrWrCnt为单字模中无效点总计数器。对字模数据的操作为:0为无效点,1为有效点,此时写背景色。

图7 8点不带背景写状态图Fig.7 State chart of 8points without background writing operation

3.2.2 SRAM 读写控制模块

外部缓存SRAM的主要作用是将STM32发送的图文数据进行缓存,以便在TFT-LCD显示有效区间,CPLD可按照一定的时序从SRAM中依次读出。对于SRAM,通过设定与的高低,将芯片的16位数据线分高8位和低8位存储RGB颜色数据,以满足存储像素点640×480的需求,即将整屏数据分为上半屏(0~239行)、下半屏(240~479行)存储,每半屏地址一样,地址数为640×240。当接收到显示像素点为上半屏数据时,设定=0=1,数据存储于低8位,当接收到显示像素点为下半屏数据时,设定=1=0,数据存储于高8位。

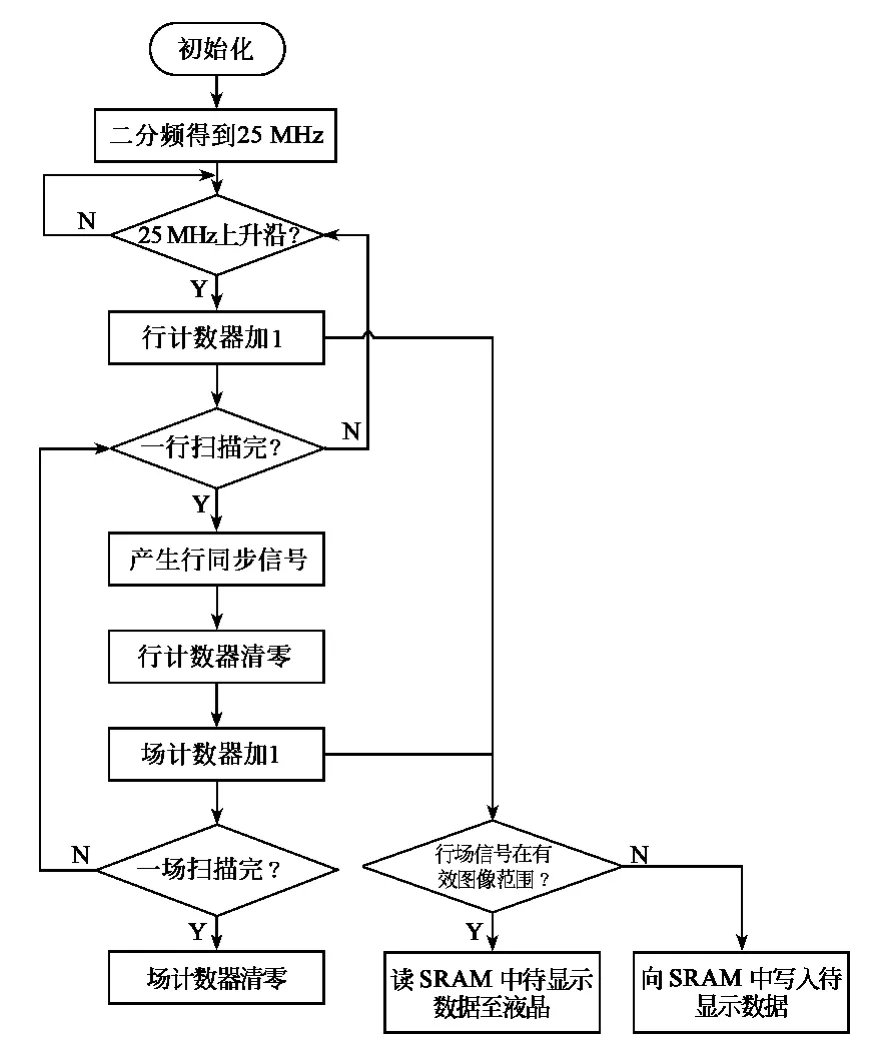

3.2.3 LCD时序驱动模块

LCD驱动程序流程图如图8所示。通过行、场计数器,产生TFT-LCD控制所需的行、场同步信号、像素时钟,同时产生RGB数据读写有效位,即在RGB数据读有效时,按照时序依次从SRAM中读取存储的数值,在RGB数据写有效时,CPLD根据数据传输指令协议,接收并解析STM32给定的TFT-LCD上各坐标点待显示的图像数据。

图8 LCD驱动模块流程图Fig.8 Flow chart of LCD driving module

4 仿真结果讨论

本节利用 Quartus II[9]软件仿真功能,对LCD时序和SRAM读写功能进行仿真。

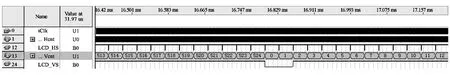

4.1 LCD时序驱动仿真

如图9为LCD时序仿真图,其中,LCD_HS是行同步信号,LCD_VS是场同步信号,可以看出,当场计数器Vcnt达到524时,意味着一场扫描完,LCD_VS发生反转,进入场消隐,同时新的一场同步信号随后到来。

图9 LCD时序仿真图Fig.9 Simulation chart of LCD timing

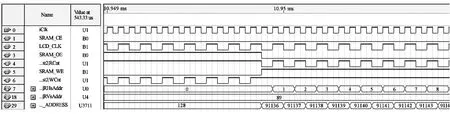

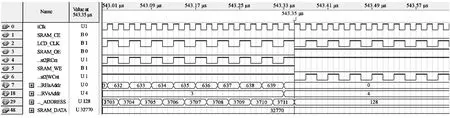

4.2 SRAM 读写仿真[10]

SRAM读写控制信号由TFT-LCD显示有效与消隐区间决定,设定RCnt和 WCnt分别为SRAM读、写状态的地址、数据判断标志位。

图10 SRAM读时序仿真图Fig.10 Simulation chart of SRAM reading

如图11,当WE为低时,SRAM进行写操作。此时,在WCnt为高电平时,给定待写像素点地址,WCnt为低电平时,同样经过20ns时延后写相应地址数据。同时,在SRAM在读操作时,行地址从0~639,当读操作结束并转入写操作时,行地址清0,场地址加1,可见仿真结果的正确性。

图11 SRAM写时序仿真图Fig.11 Simulation chart of SRAM writing

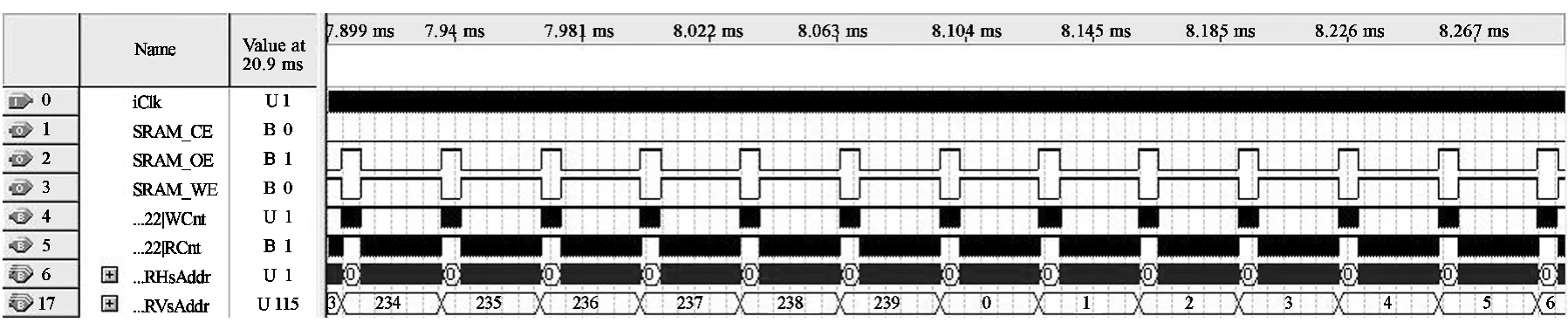

图12是对TFT-LCD半场信号扫描仿真的结果。在TFT-LCD的行扫描中,有一段消隐区间与有效区间;在消隐区间,可以对SRAM进行数据写操作,在有效区间,按照行地址计数0~639依次输出信号。每行扫描结束后,场地址加1,当场地址到达239时,即TFT-LCD半场扫描结束,接下来以同样的地址进行下半场的扫描。

图12 半场扫描完仿真图Fig.12 Simulation chart of half-court scanning finished

4.3 实现结果

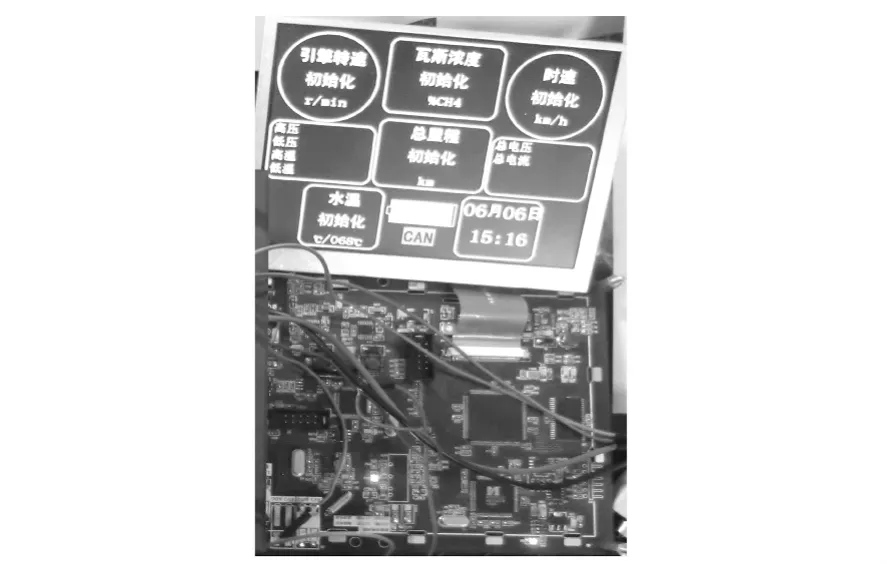

通过采用本文设计方法,实现的设计实物效果如图13所示。

图13 设计实物图Fig.13 Chart of design entity

5 结 论

本文介绍了基于STM32和CPLD的TFTLCD显示控制器的设计方法。TFT-LCD模块采用的是不带LCD控制器的群创AT056TN52-5.6in(1in=2.54cm)TFTLCD。在设计控制器时,采用的是Altera公司的 MAX II系列的 CPLD(EPM570)作为核心部件,以ISSI公司的IS61LV25616大容量SRAM作为显示缓冲存储器。测试结果表明,本文设计的控制器相对市场上TFT-LCD的专用控制芯片工作稳定可靠,性价比高。在很多场合具有一定的实用价值。

[1] 徐婧婧.彩色有源LCD显示屏外围驱动电路的研究与设计[D].长春:吉林大学,2007.Xu J J.The research and design on the peripheral driving circuit of color AM-LCD [D].Changchun:Jilin University,2007.(in Chinese)

[2] Lin J T,Wang F K,Lo S L,et al.Analysis of the supply and demand in the TFT-LCD market[J].Technological Forecasting and Social Change,2006,73(4):422-435.

[3] 李辉祥,黄光明.基于 CPLD 的 TFT-LCD控制器的设计[J].电子设计工程,2011,19(23):128-130.Li H X,Huang G M.Design of TFT-LCD controller based on CPLD [J].Electronic Design Engineering,2011,19(23):128-130.(in Chinese)

[4] 李宁.基于MDK的STM32处理器开发应用[M].北京:北京航空航天大学出版社,2008.Li N.Application of STM32 Processor Development Based on MDK [M].Beijing:Beihang University Press,2008.(in Chinese)

[5] 胡健生,罗卫兵,钱渊.嵌入式TFT-LCD控制器设计[J].计算机工程,2010,5:088.Hu J S,Luo W B,Qian Y.Design of embedded TFT-LCD controller[J].Computer Engineering,2010,5:088.(in Chinese)

[6] 苏维嘉,张澎.基于FPGA的 TFT-LCD控制器的设计和实现[J].液晶与显示,2010,25(1):75-78.Su W J,Zhang P.Design and implementation of TFT-LCD controller based on FPGA[J].Chinese Journal of Liquid Crystals and Displays,2010,(2511):75-78.(in Chinese)

[7] 唐徐立,黄君凯,刘明峰,等.基于FPGA的TFT-LCD控制器设计与实现[J].集成电路设计与开发,2010,35(11):1134-1137.Tang X L,Huang J K,Liu M F,et al.Design and realization of the TFT-LCD controller based on FPGA[J].Design and Development of IC,2010,35(11):1134-1137.(in Chinese)

[8] 黄杰勇.基于CPLD的 TFT-LCD控制器设计[J].现代计算机:上半月版,2013(2):62-64.Huang J Y.Design of TFT-LCD controller based on CPLD[J].Modern Computer:First Half Edition,2013(2):62-64.(in Chinese)

[9] 王冠,俞一鸣.面向CPLD/FPGA的Verilog设计 [M].北京:机械工业出版社,2007.Wang G,Yu Y M.Verilog Design for CPLD/FPGA [M].Beijing:Machinery Industry Press,2007.(in Chinese)

[10] 薛家祥,黄泽林,沈栋,等.TFT-LCD驱动中SDRAM 控制器的仲裁器设计[J].液晶与显示,2013,28(6):877-882.Xue J X,Huang Z L,Shen D,et al.Design of SDRAM controller with arbiter for TFT-LCD driver[J].Chinese Journal of Liquid Crystals and Displays,2013,28(6):877-882.(in Chinese)