智能卡去激活测试问题分析与解决方法

2015-04-15周代卫中国信息通信研究院泰尔终端实验室工程师

周代卫 中国信息通信研究院泰尔终端实验室工程师

张沛 中国信息通信研究院泰尔终端实验室工程师

周宇 中国信息通信研究院泰尔终端实验室高级工程师

孙向前 中国信息通信研究院泰尔终端实验室国际认证部主任,高级工程师

泰尔检测

智能卡去激活测试问题分析与解决方法

周代卫 中国信息通信研究院泰尔终端实验室工程师

张沛 中国信息通信研究院泰尔终端实验室工程师

周宇 中国信息通信研究院泰尔终端实验室高级工程师

孙向前 中国信息通信研究院泰尔终端实验室国际认证部主任,高级工程师

针对移动通信终端设备检测认证中常见的一类智能卡去激活测试失败问题,通过借助专用测试工具实际比对和验证,深入分析并定位了问题原因,进一步提出了一种通过软件控制的分段降压法。该方法通过了实际验证,并且具有不改动硬件设计,同时不影响其他一致性测项的优点。

智能卡 机卡接口 去激活 逻辑电位

1 引言

智能卡SIM(SubscriberIdentityModule,用户身份识别模块)/UICC(Universal Integrated Circuit Card,通用集成电路卡)作为通信系统中用户身份识别和安全加密的主要载体,被广泛应用于移动通信终端、银行社保卡、交通充值卡、物联网嵌入式SIM卡等业务领域。其去激活过程通常发生在终端设备关机、SIM卡冷重启(Cold Reset)或机卡接口电压切换(Voltage Switching)时。为防止对SIM/UICC电路芯片的损坏,机卡接口各管脚掉电次序和电气特性需符合ISO/IEC/ETSI相关技术规范。

在ISO/IEC7816-3章节6.4中规定:当信息交换完成或终止后,如SIM卡无响应、SIM卡被移除,终端设备需按如下顺序去激活机卡接口电路:

(1)RST管脚(C2)切换至逻辑低电位L。

(2)CLK管脚(C3)切换至逻辑低电位L,除非CLK已经终止并处于低电位。

(3)I/O管脚(C7)切换至逻辑低电位L。

(4)VCC管脚(C1)去激活。

可见,终端在去激活时机卡接口电气特性需满足各管脚掉电次序和电压特性两方面的需求。

以上技术要点在移动终端设备机卡接口一致性测试标准中都有完整涵盖,如ETSITS 102 230TC 5.1.3(UICC)和3GPP TS 51.010-1 TC 27.17.1.4(SIM)。并且,这些测试例均为通信终端设备国内进网检测CTA或欧美自愿性测试GCF/PTCRB中的A类测项,即所有认证终端必须通过。

2 问题分析

SIM/UICC去激活机卡接口电气特性测试步骤可概括为:

(1)被测终端设备连接上测试模拟卡。

(2)终端设备开机并正常关机或触发电压切换过程。

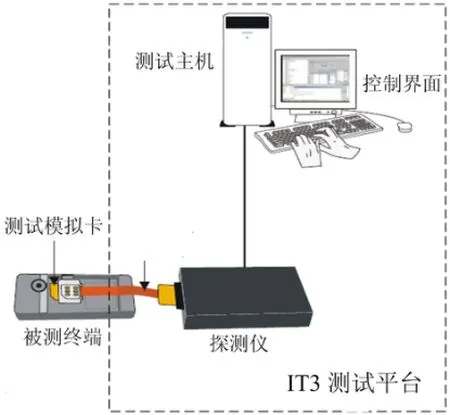

测试中,与模拟卡相连的探测仪(Probe)通过检测关机或电压切换时机卡接口各管脚的时域和电气特性来判定终端是否符合技术标准,特别是“其他各管脚必须在VCC离开高电位之前到达低电位”的要求。实际测试系统通常选用德国COMPRIONIT3测试平台,其连接图如图1所示。

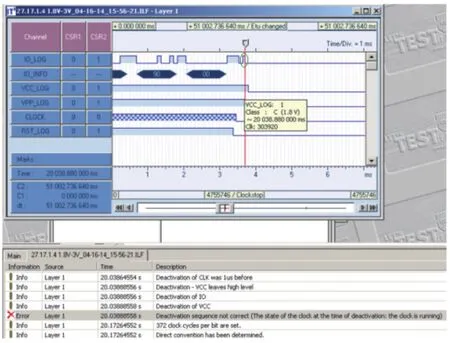

然而,在测试中部分终端设备常无法通过该测试,主要原因为机卡接口各管脚去激活顺序不符合上述要求。在测试系统中常出现如图2的提示。

从系统提示可知,该类常见SIM/UICC去激活测试失败的主要原因在于机卡接口各管脚去激活时的掉电顺序,而与报错提示相对应的时间点为I/O_LOG最后的电位切换时刻。从L1波形图和各步骤时间偏移量可知:RST、CLK、I/O和VCC4个管脚的逻辑电位转换时序(即RST→CLK→I/O→Vcc)是符合测试标准中的规定的。图2中VPP管脚(C6)用于为SIM运行时提供额外电压,相关技术规范中是可选支持的,且现行终端均将其直接连到VCC上,在本测试中不作为考察因素之一。

图1 测试系统连接图

图2 测试例失败系统结果

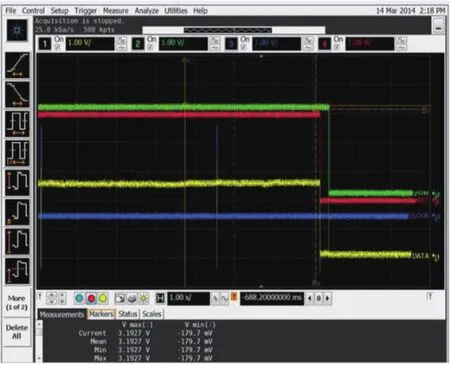

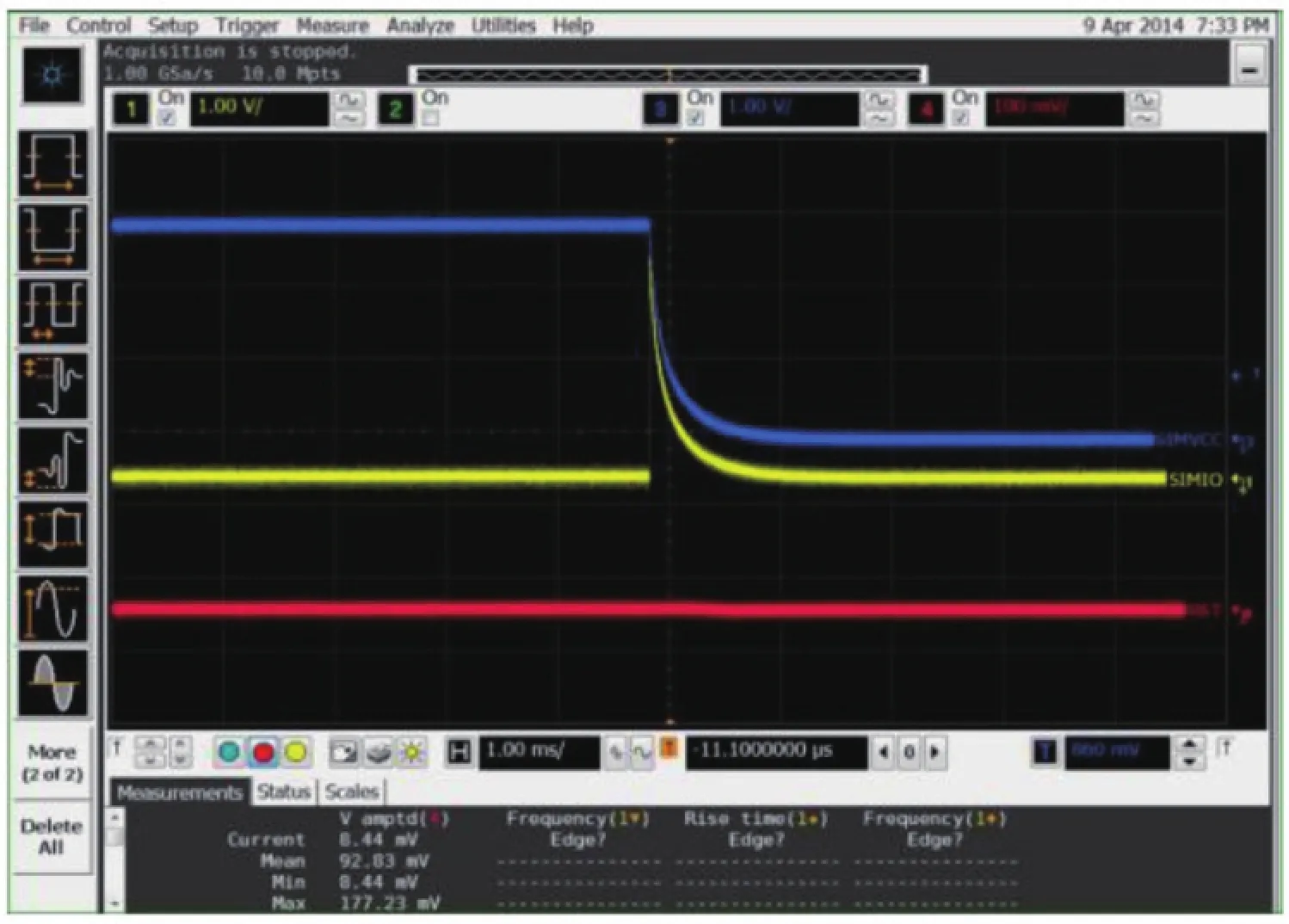

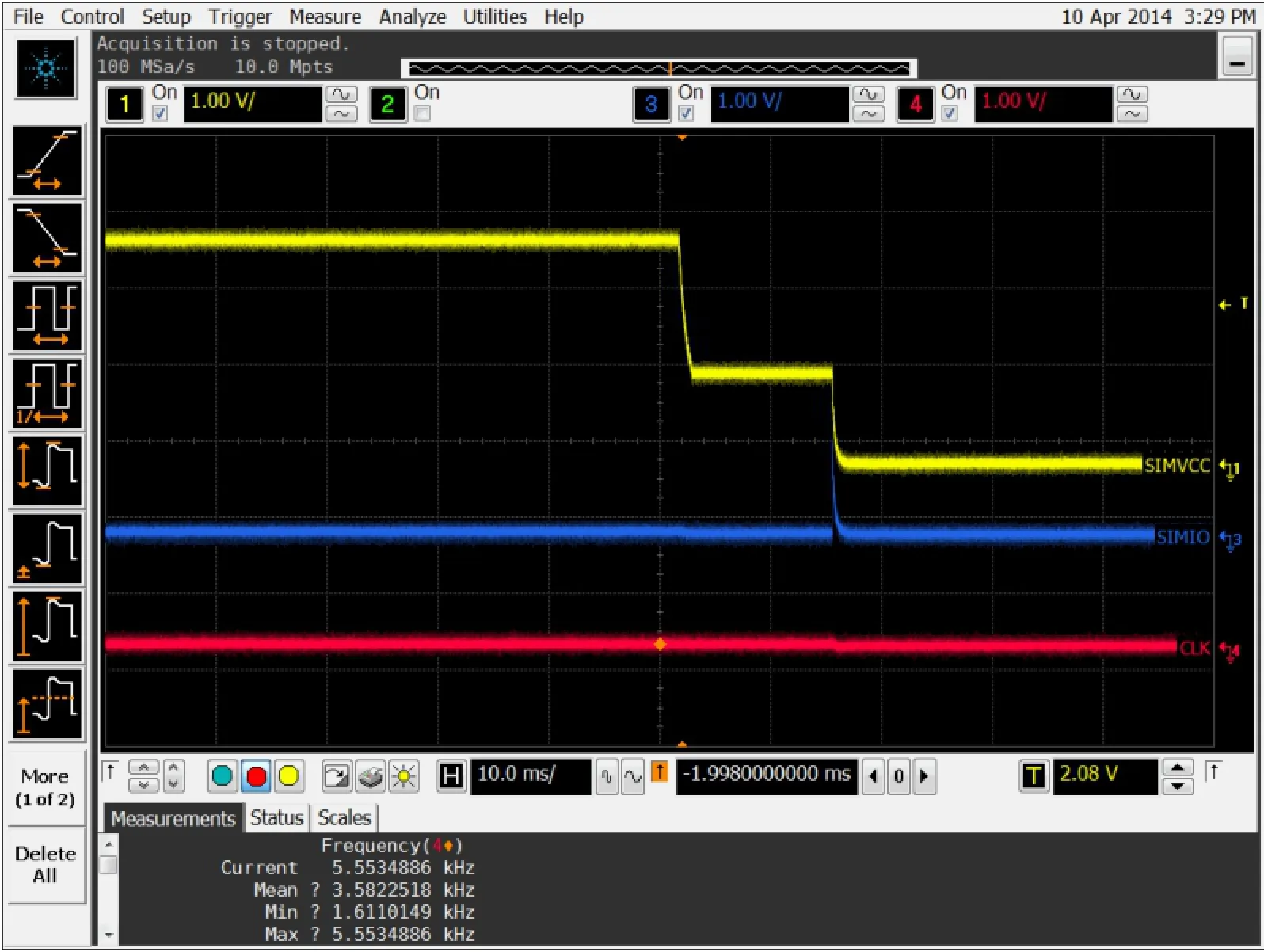

为进一步分析各管脚实际电压信号,借助安捷伦混合信号示波器测得的模拟信号波形如图3所示。

图3中VSIM为VCC,DATA为I/O,CLOCK为CLK(下同)。从图中来看,各管脚掉电顺序也满足RST→CLK→I/O→Vcc的要求,和图2中逻辑波形图相一致。然而,仔细对比发现I/O管脚波形在VCC掉电时刻出现瞬时脉冲,其峰值达到输入逻辑高电位,导致其逻辑状态在处于低电位L后重新被判定为高电位H,并维持了约20ns,即图2中I/O_LOG管脚上标记的瞬时脉冲。然而,从其持续时间和占空比来看,该脉冲并非由基带芯片触发的数据收发所致,因此不需对I/O做软件锁死处理。

在局部放大该波形图后进一步发现其下降沿与VCC同步,且信号幅度和下降趋势完全一致,具体对比结果如图4所示。

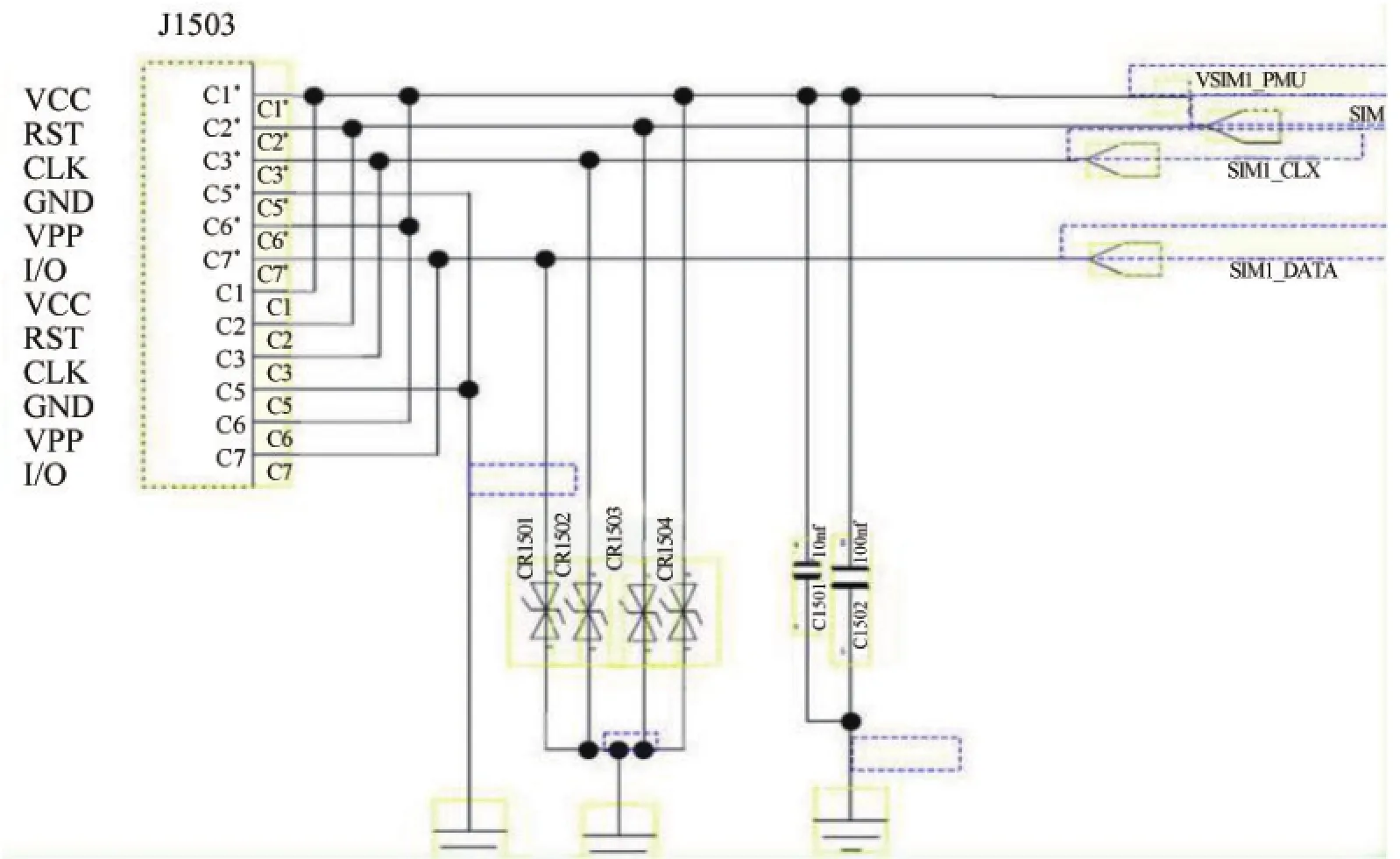

造成上述I/O管脚信号毛刺出现的原因主要为电源管理芯片PMIC或SIM控制器的输出控制导致电压瞬时被拉起。而此信号毛刺在终端设备中普遍存在,通过该测试的终端依然存在。而这主要和SIM/UICC部分的电路逻辑设计有关,通常其原理图如图5所示。

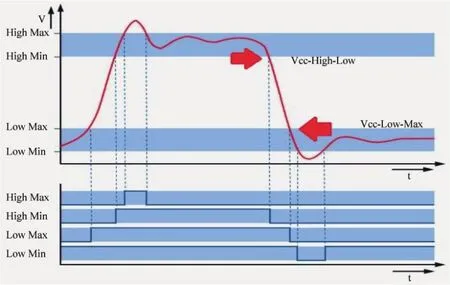

在测量系统的配置中,I/O管脚逻辑电位IO_LOG对应了如下4个门限:

(1)I/O-HIGH-Max。

(2)I/O-HIGH-Min。

(3)I/O-LOW-Max。

(4)I/O-LOW-Min。

其中逻辑电位从H切换至L时的门限为I/OHIGH-Min,对于ClassB(3 V)SIM卡取值为2.25V,对于ClassC(1.8V)SIM卡为1.35V。

类似地,VCC管脚逻辑电位同样对应了4个门限:

(1)VCC-High-Max。

(2)VCC-High-Min。

(3)VCC-Low-Max。

(4)VCC-Low-Min。

图3 去激活时各管脚电压波形图

图4 VCC和I/O波形局部放大图

其中,VCC-High-Min和I/O-High-Min的取值一致。不同的是,VCC_LOG对应单独的最低电压门限,取值为0.5V。其模拟信号和逻辑信号对应关系如图6所示。

图5 SIM/UICC逻辑电路图

图6 VCC管脚模拟和逻辑信号图

因此,对于时间上对齐且幅度和下降速率一致的I/O和VCC管脚信号,因I/O_LOG和VCC_VHMIN的门限值一致,其逻辑信号切换时间点也一致,而VCC_VHMIN从H变成L为本测试中VCC离开高电位的参考时间点,所以I/O管脚不满足“必须在VCC离开高电位之前到达低电位”的要求,最终导致测试例失败。

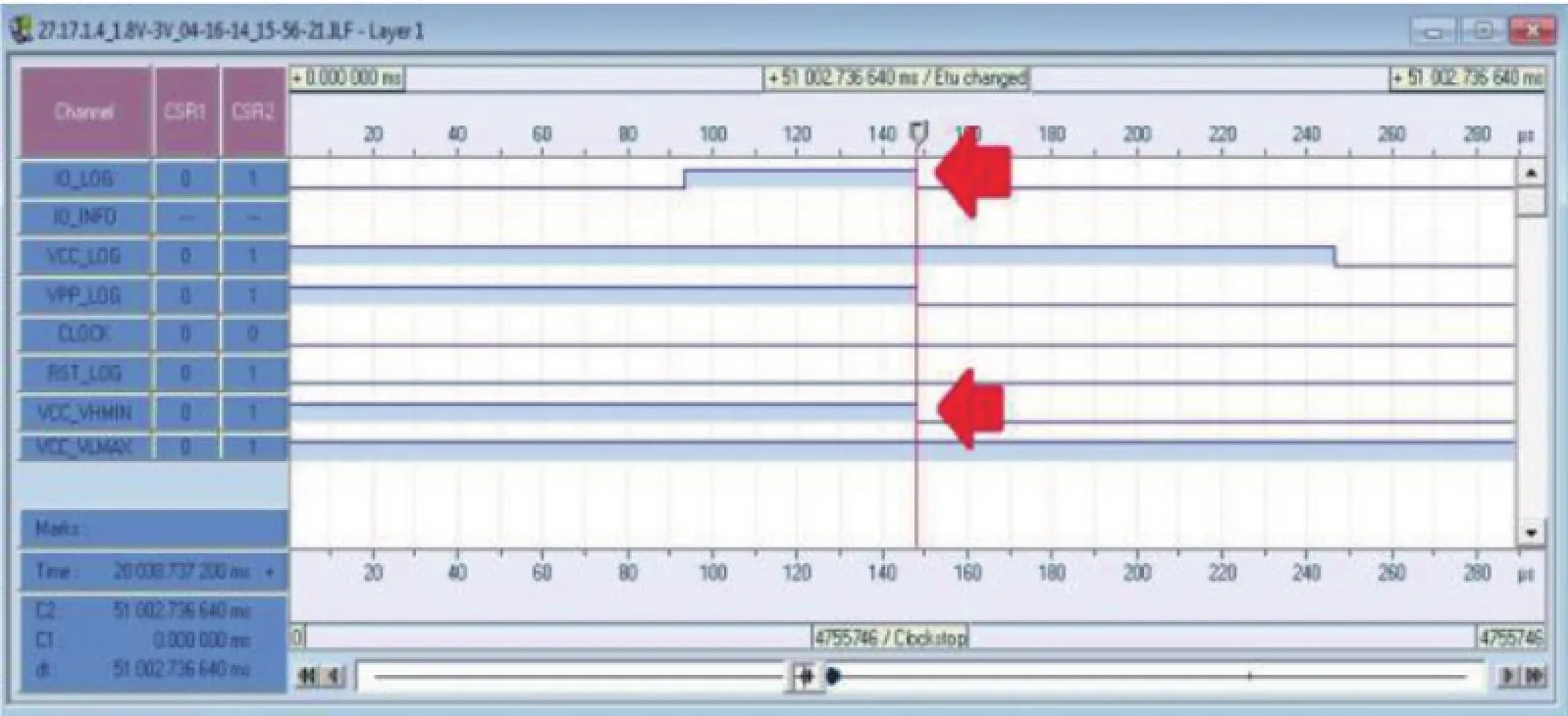

在逻辑波形图上,VCC_LOG由于门限相比于I/O_LOG较低,其状态切换时间点要晚于I/O_LOG,但是由于VCC_LOG仅是VCC管脚的逻辑参考状态之一,不是测试时参考的主要依据。具体可从图7中新引入VCC_VHMIN逻辑信号后的波形图中清晰地看到测试例失败的原因为:I/O_LOG和VCC_VHMIN同步回落低电位。

图7 引入VCC_VHMIN后的逻辑波形图

3 解决方法

从以上分析可知,该测试例失败的主要原因在于I/O管脚最后的突发脉冲信号,而该信号毛刺是由PMIC或SIM控制器在控制VCC掉电时触发的。通过修改滤波电容或者设置VCC去激活延迟等方式并不能完全消除此信号,也不能克服I/O_LOG和VCC_ VHMIN同步下降的问题。

鉴于VCC掉电时I/O和VCC管脚都有此信号毛刺,且I/O_LOG状态转换门限由I/O-High-Min决定,VCC由VCC_VHMIN决定,因此可采取由PMIC或SIM控制器触发的分段降压法克服此问题,其思路为:

(1)VCC电压逐步降到I/O-High-Min以下(如ClassC1.2V)并维持一段时间(如10ms)。

(2)通过VSIM_EN停用VCC。

此方法的优点在于:虽然I/O管脚最后时刻仍存在和VCC一致的信号毛刺,但其峰值已低于I/O-High-Min这一门限,所以I/O_LOG可在数据传输终止后仍保持逻辑低电位而不被暂时拉起,而VCC_VHMIN和VCC_LOG按原门限正常切换至低电位。

此外,该方法无需对现有硬件设计做修改,只需要在SIM软件控制部分稍作修改即可。采用此方法后终端关机时实际测量的I/O和VCC波形图如图8所示。

图8中上面的波形为VCC管脚,下面的波形为IO管脚。从图中可知,虽然I/O管脚最后仍存在和VCC一致的信号毛刺,但其电压水平始终处于I/O-High-Min门限以下,故不会再次回到逻辑高电位,也就不存在和VCC_VHMIN同时回落到逻辑低电位的问题。该方案可解决SIM/UICC去激活测试失败的问题,经过实际测试验证能正常通过相关测试例,同时也不会对其他测项带来负面影响。

4 结束语

综上所述,SIM/UICC去激活测试例中的关键时序参考点为VCC管脚逻辑电位切换点,其高电位门限值VCC_VHMIN和I/O管脚逻辑门限I/O_LOG保持一致,通常由于I/O管脚在VCC掉电时也出现瞬时脉冲波形,I/O_LOG和VCC_VHMIN将同步回落至低电位导致测试例失败。而测试系统中指示的VCC逻辑信号VCC_LOG并非实际衡量的指标,也对失败测例的分析带来了一定的干扰。

去激活过程中VCC掉电信号毛刺会同步传导到I/O管脚而难以避免,也难以通过常规的改变滤波电容值或增加VCC掉电延时的方法来处理,且伴随的硬件设计变更将导致大批量样机处理成本的剧增,并会对其他正常信号产生影响。而本文中提出的通过软件控制的分段降压法则从根本上避免了此信号毛刺对I/O管脚逻辑电位的影响,从而可确保各管脚去激活的时序和电气特性完全符合SIM/UICC技术规范的要求,同时更低的峰值电压也降低了SIM/UICC电路芯片被损坏的风险。

图8 改进后实测波形图

1 ETSI TS 102 230 V10.1.1.Smart Cards;UICC-Terminal Interface;Physical,Electrical and Logical Test Specification. 4,2014

2 ETSI TS 102 221 V11.1.0.Smart Cards;UICC-Terminal Interface;Physical and Logical Characteristics.11,2013

3 3GPP TS 51.010-1 V12.0.0.Digital Cellular Telecommunications System(Phase 2+);Mobile Station(MS)Conformance Specification;Part 1:Conformance Specification.3,2014

4 3GPP TS 11.11 V8.14.0.Terminals Specification of the Subscriber Identity Module-Mobile Equipment(SIM-ME) Interface.6,2007

5 ISO/IEC 7816 Series(2006).Identification Cards-Integrated Circuit Cards-Part 3:Cards with Contacts-Electrical Interface and Transmission Protocols.11,2006

6 COMPRION IT3 Test Platform User Manual Version.2013

Analysis and Solution of Smart Card Deactivation Test Failure

Based on a class of common failure issue during SIM/UICC deactivation testing of mobile terminals,a dedicate testing tool and measurement method are used to analyze the fail logs and to compare the possible factors.This paper locates the root cause of the problem through in-depth analysis,and further proposes a software-controlled powerdrop method by two stages.With actual verification result,this method does not impact the hardware design and achives the advantage of consistent conformance testing.

smart card,Cu interface,deactivation,logical power level

2015-02-26)