采用正弦幅值积分器的单同步参考坐标系同步信号检测方法

2015-04-10刘延东王国宁孙鹏菊周雒维

杜 雄 刘延东 王国宁 孙鹏菊 周雒维

采用正弦幅值积分器的单同步参考坐标系同步信号检测方法

杜 雄 刘延东 王国宁 孙鹏菊 周雒维

(重庆大学输配电装备及系统安全与新技术国家重点实验室 重庆 400030)

三相并网变流器的控制需要提取电网电压同步信号,实现正、负序分量的分离。在电网电压不对称工况下,由于电压负序分量的影响,传统的单同步参考坐标系锁相环(SRF-PLL)性能受到影响。本文通过对不对称工况下SRF-PLL的性能分析,提出了一种基于正弦幅值积分器锁相环(SAI-PLL)的单同步参考坐标系正、负序分量分离方法。该方法利用正弦幅值积分器(SAI)消除了基波负序分量对正序分量提取的影响,并可同时实现负序分量的提取。详细介绍了SAI-PLL方法的工作原理,并建立了数学模型,讨论了相关参数的选取。与其他方法进行了比较,结果表明本文提出的方法在性能上具有一定的优势。仿真和实验结果均表明,所提出的方法能够消除电网不对称/畸变工况对同步检测的影响,准确快速地提取电网同步信号。

不对称 同步信号提取 锁相环 同步旋转坐标系 正弦幅值积分器

1 引言

并网变流器在光伏发电、风力发电等分布式电源中得到了广泛的应用,并网变流器的运行和控制需要准确得到电网电压的同步信号信息,如电网电压基波正、负序分量的幅值、相位等[1-6]。锁相环(Phase-Locked Loop,PLL)是一种能够实现两个电信号相位同步的自动控制闭环系统,其中以同步坐标系锁相环SRF-PLL(Synchronous Reference Frame-PLL)在电网电压同步信号提取中的应用最为广泛[7-8]。SRF-PLL在电网电压对称的情况下可以很好地实现基波正序分量的提取,但是在电网电压不对称情况下,由于基波负序分量的影响,会在 dq轴分量中产生2倍工频的交流分量,导致SRF-PLL难以取得令人满意的结果[7-8]。

为了消除不对称对SRF-PLL同步性能的影响,采用两种结构解决该问题:一是“先滤波,后 dq变换”;二是“先dq变换,后滤波”[4,7]。“先滤波,后dq变换”结构为:在三相/两相静止坐标系中,使用不同的滤波方案将基波负序分量滤除或将基波正、负序分量分离,然后将得到的静止坐标系基波正序分量进行 dq变换,从而完成锁相。如文献[9]提出基于对称分量理论的延时相消法,文献[10-11]提出基于全通滤波器的瞬时对称分量法,这些方法均假设电网频率固定。文献[12]提出基于双二阶广义积分器锁相环方法,将锁相环得到的频率信息反馈到广义积分器中以解决电网频率变化的影响。文献[13]提出一种复数滤波方案,相比文献[12],可以不用对称分量分解实现正、负序分离,同步性能相近。“先dq变换,后滤波”结构为:利用已经锁住的基波正序相角,对电网三相输入信号进行Clarke/Park变换,得到同步参考坐标系下的基波正、负序分量,然后利用不同的滤波方案将基波负序分量滤除或将基波正、负序分量分离,将得到的基波正序分量送进PLL完成锁相。如常见的加低通滤波器方案,降低PLL环路滤波器带宽方案[8],但这并不能完全消除负序分量的影响,还会降低系统的动态响应速度。对此,文献[14]提出一种解耦双同步参考坐标系锁相环方案,利用正、负序两个同步旋转坐标系和解耦网络,实现了同步坐标系基波正、负序分量的分离,双同步坐标变换以及解耦网络式的结构复杂,且低通滤波器的使用一定程度上降低了系统的动态响应速度,文献[15]采用多通道方案以减小谐波的影响。

以上方案是通过PLL来获得电网角频率、基波正序相位角等信息,锁频环(Frequency-Locked Loop,FLL)也可用于同步信号检测,且不需要进行dq变换[16-21]。如基于自适应陷波器的ANF-FLL(Adaptive Notch Filter-FLL)法[16-17],改进的增强型锁相环EPLL(Enhanced-PLL)法[18],双二阶广义积分器锁频环DSOGI-FLL(Double Second Order Generalized Integrator-FLL)法[19-20],文献[21]为多通道方案以减小谐波的影响,这些方法均借助对称分量计算单元实现基波正序分量的提取,然后利用FLL得到电网频率,但使用非线性单元使得结构较复杂,瞬时对称分量计算单元使得计算量较大。

本文以目前广泛采用的 SRF-PLL为基础,采用“先dq变换,后滤波”的结构,将特定谐波提取单元——正弦幅值积分器(SAI)和 SRF相结合,实现了单同步坐标系基波正、负序分量的分离;在电网不平衡/畸变工况下,还可以采用多通道方案(即采用多个提取频率不同的特定谐波提取单元)实现基波正、负序分量及谐波分量的无衰减分离,从而消除电网不平衡/畸变对同步性能的影响。与传统的低通滤波器方案相比,该方案不仅可以获得基波正序分量同步信息,还可以获得基波负序分量和谐波分量的同步信息,并且不影响系统的动态响应速度。仿真对比和实验结果表明,所提方案稳定且动态性能好。

2 采用正弦幅值积分器的单同步坐标系正、负序分量分离方法

2.1 输入电压不对称时SRF-PLL的性能分析

图1所示为传统单同步参考坐标系锁相环SRFPLL的结构框图[7]。当三相电网电压不对称时,忽略零序分量,电网电压可写成基波正序、负序分量之和。即

式中,V+1、V-1分别为基波正、负序分量的幅值;φ+1、φ-1分别为正、负序分量的初相位;ω为电网基波角频率。

图1 SRF-PLL结构框图Fig.1 The diagram of the SRF-PLL

三相电压va、vb、vc通过Tαβ和 Tdq矩阵分别进行Clarke变换和 Park变换,得到

式中,θ+1为锁相环输出的基波正序分量相位角。当稳定锁相后有 θ+1≈ωt+φ+1,式(2)可化简为式中,φ=φ-1-φ+1。可以看出,在经过同步旋转坐标变换后,电网电压基波正序分量变成了直流量,而电网电压基波负序分量则变成了 2倍工频交流分量,这将会对 SRF-PLL的输出性能产生影响[14]。

2.2 SAI-PLL结构

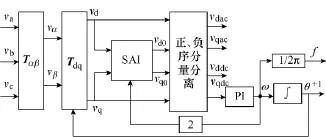

为了消除同步坐标系下电网电压负序分量产生的2倍工频分量的问题,本文提出了一种基于正弦幅值积分器锁相环(SAI-PLL)的同步坐标正、负序分量分离方法。其结构框图如图2所示。

图2 正弦幅值积分器锁相环示意框图Fig.2 The block diagram of SAI-PLL

图2 在图1的基础上增加了SAI单元来分离提取 dq轴分量 vd、vq中的交、直流分量(基波正、负序分量)。这里 SAI的输入量为 vd、vq,输出量为 vd0、vq0,通过正、负序分量分离单元来分别得到正、负序分量 vddc、vqdc、vdac、vqac。下面将分别对SAI单元和正、负序分量分离单元的工作原理进行介绍。

2.3 正、负序分量的提取与分离

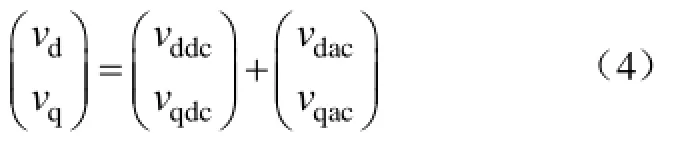

式(3)可以表示为直流分量和交流分量之和的形式,即

式(4)采用复数形式可表示为

本文借助 SAI对vdq中的交、直流分量进行分离。SAI在理想情况下可以实现特定频率交流分量的无衰减、无相差提取[22]。其实现电路如图3所示。图3中输入信号为 vd、vq,输出信号为 vd0、vq0,其中2ω为 PLL得到的角频率信号,k为调节参数。图3中SAI单元复数传递函数可描述为[22-23]

图3 SAI单元Fig.3 The SAI structure

从式(6)可以看出,当 s=-j2ω时,HSAI(-j2ω)= 1,表明图 3可以实现对 dq轴交流分量的无静差跟踪,即

然而,图3所示的SAI单元的输入信号中除含有交流分量外,还含有直流分量,直流分量可以看成频率为0的交流分量,其经过SAI后的响应为

因此,SAI单元的输出中除含有和输入交流分量相同的交流分量外,还含有和输入直流分量线性相关的直流分量。

根据式(5)、式(6)、式(8),可得到dq变换后的直流分量为

根据式(5)、式(9),可以得到交流分量

从而实现了直流分量和交流分量的分离,即提取出了正、负序分量。式(9)、式(10)可以采用图4所示的正、负序分量分离单元来进行实现。

图4 正、负序分量分离单元Fig.4 The separation structure for the fundamental positive and negative sequence components

通过图4实现式(9)、式(10)的线性运算,实现了与正、负序分量相对应的直流分量和交流分量的分离。可以根据分离出的交、直流分量分别得到正、负序分量的幅值和相位信息。

正序分量的幅值为

正序分量相位θ+1由锁相环积分器的输出得到。负序分量的幅值和相位分别为

2.4 电网不对称/畸变工况下的SAI-PLL结构

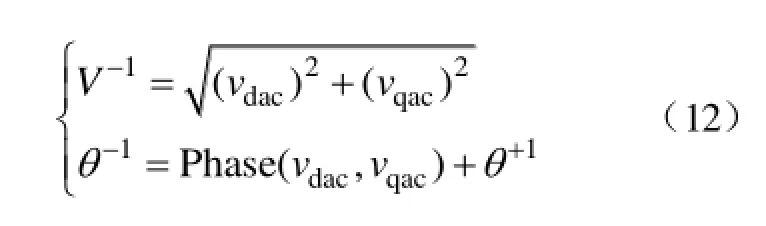

针对电网不平衡/畸变问题,可以采用多通道同步方案,即采用多个提取频率不同的 SAI单元,借助相应的分离结构实现基波正、负序分量和谐波分量的分离,图 5给出了多通道同步方案的整体结构。

图5 电网不对称/畸变工况下同步方案Fig.5 The synchronization method for unbalanced/harmonic condition

实际电网中高次谐波含量一般较小,因此一般可只考虑低次谐波影响,本文主要考虑-5、+7次谐波的影响,根据实际需要还可以加入其他谐波的影响。由图5结构可得到各个分量的具体表达式为

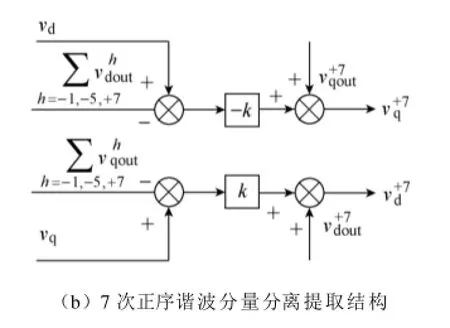

式(13)表明,基波正、负序分量和谐波分量实现了分离。借助式(13)可以构建相应的谐波分离提取结构单元,如图 6所示。

图6 谐波分量分离提取结构Fig.6 The separation/extraction structure for the harmonic components

3 SAI-PLL的数学模型和参数设计

3.1 数学模型

SAI-PLL相对SRF-PLL增加了SAI单元和正、负序分量分离单元,该两部分单元的传递函数为

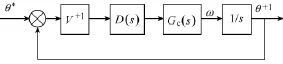

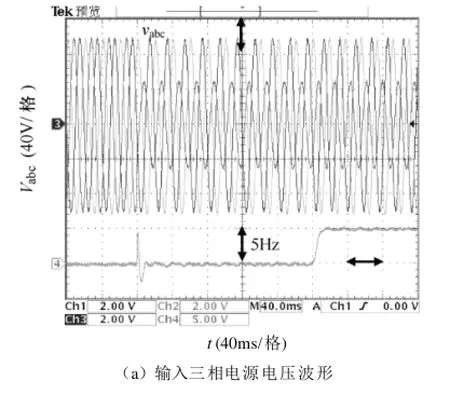

结合SRF-PLL的交流小信号模型[7],可以得到SAI-PLL的线性化闭环控制框图如图7所示。

图7 线性化SAI-PLL控制框图Fig.7 The linearized control block of SAI-PLL

从图 7可以看出,SAI-PLL的数学模型只在SRF-PLL的基础上增加了D(s)环节,其中Gc(s)为待设计的补偿器

系统开环传递函数为

3.2 参数设计

3.2.1 参数k的选取

锁相环的输出角频率与实际角频率会存在一定偏差,由式(6)可以看出,当锁相环输出角频率为mω时(m≈1)

其模和相角为

从式(18)可以看出,存在频率偏差时,若 k越大,则100Hz的交流分量的衰减程度会越小,但从式(16)可以看到,k值越大,开环传递函数的相角裕度会越小,不利于系统的稳定。所以综合考虑衰减程度和相角裕量,取

3.2.2 PI调节器的设计

图8 未补偿开环传递函数伯德图Fig.8 The Bode plot of the uncompensated open loop transfer function

从图8可以看出,未补偿前的低频段增益低,而且为了消除由锁频误差所带来的100Hz交流分量的影响,选定补偿后系统开环传递函数 Tc(s)的带宽为40Hz,相角裕度45°,PI调节器的参数计算如下经过计算,可以得到PI调节器的参数为

依据上述参数,可得出补偿后的开环传递函数伯德图如图9所示。

图9 补偿后的开环传递函数伯德图Fig.9 The Bode plot of the compensated open loop transfer function

从图9可以看出,补偿后的开环带宽为40Hz,相角裕度为45°左右。

4 仿真性能分析

为了验证本文所提方法的性能,以两相电压跌落工况为例(其中 B、C两相电压跌落 50%),将其和三种代表性的同步检测方法——三相 ANF-FLL[16]、DDSRF-PLL[14]及 DSOGI-PLL[12]进行了对比仿真研究。主要仿真参数见表1。仿真结果如图 10所示,图 10a为三相输入电压波形,图 10b~10e分别为三相ANF-FLL、DDSRF-PLL、DSOGI-PLL和 SAIPLL的输出结果。图中分别表示正、负序分量的电压幅值和相位。

表1 仿真参数Tab.1 The simulation parameters

图10 仿真结果对比Fig.10 The comparison of simulation results

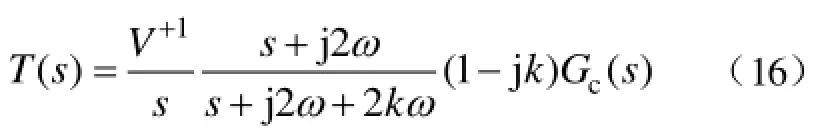

从图10的仿真结果对比可以看出,本文所提出的方法的动态响应速度优于文献中的三种主要同步检测方法,具体动态响应速度对比如表 2所示。

表2 四种同步检测方法的动态响应速度对比Tab.2 The comparison on dynamic response for four synchronization signal detection methods

5 实验验证

通过实验对本文提出的同步信号检测方法的性能进行验证。输入电源电压信号由可编程序三相交流电源61703提供。实验参数为:三相输入交流电源对称情况下的相电压幅值为 V+1=100V,频率为50Hz。SAI单元参数锁相环 PI调节器使用3.2节中的设计参数。

本文对两种工况进行实验,分别为:①单相电压跌落及不平衡下频率跳变实验;②含谐波的单相电压跌落实验;其中电源中所注入的谐波含量为 5次、7次谐波各为 20%。实验波形主要包括三相输入电压波形,电压基波正、负序幅值与相位角。

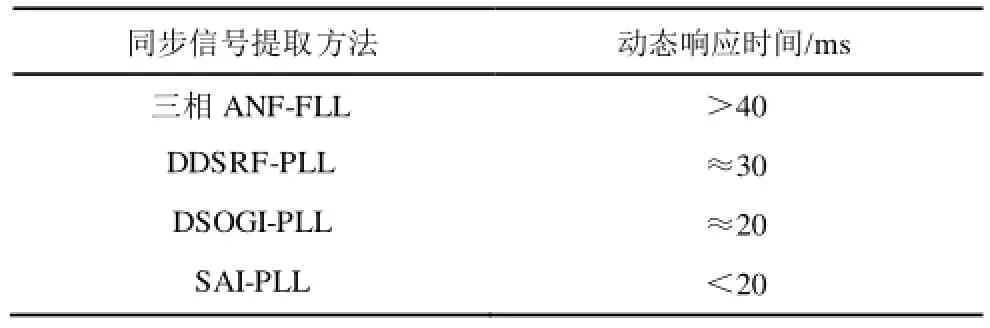

5.1 单相电压跌落及不平衡下频率跳变实验

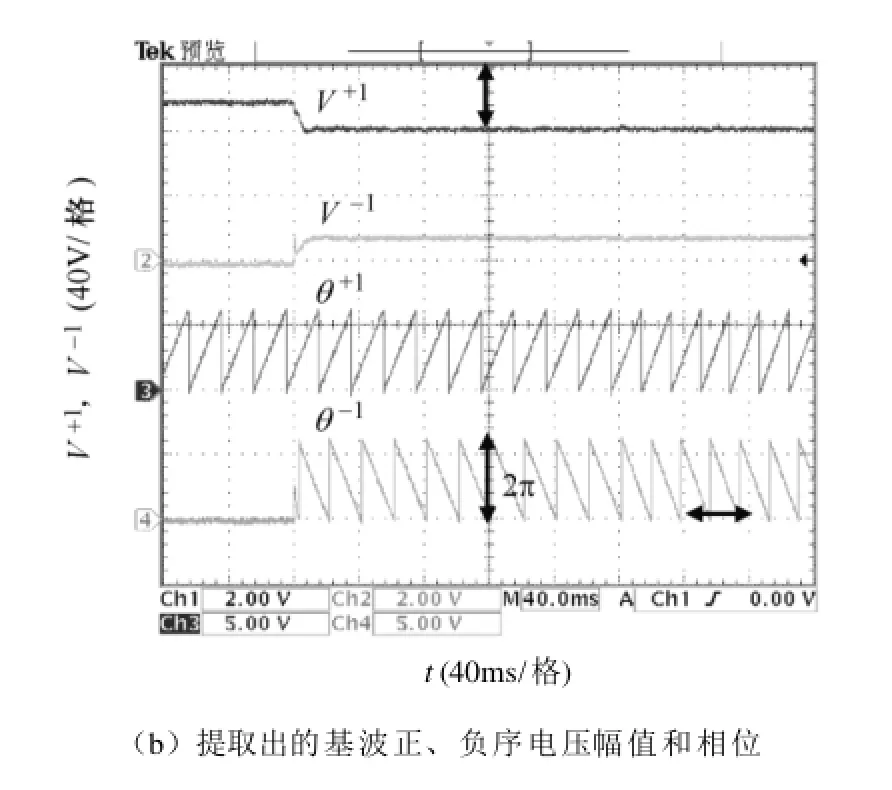

单相电压跌落及不平衡下频率跳变时的实验结果如图11所示。图11a为单相电压跌落及不平衡下频率跳变时的三相输入电压波形,可以看出,C相电压幅值跌落50%,电网频率升高5Hz。图11b为提取出的基波正、负序分量的幅值和相位。

图11 单相电压跌落及不平衡下频率跳变实验结果Fig.11 Experimental results under single phases drop and frequency jump conditions

由图 11可以看出,在发生单相电压跌落时,该同步信号检测方法能够准确地提取出基波正、负序的幅值和相位,但检测出的频率存在波动,可以通过进一步优化设计结构中参数及 PI调节器参数来予以消除,整体响应时间小于1个工频周期;在发生不平衡下频率跳变时,该方法能够准确地检测出频率的变化,且检测出的基波正负序幅值和相位几乎没有波动,整体响应时间小于1个工频周期。

5.2 含谐波单相电压跌落实验

为了提高输入电压含谐波情况下的同步性能,本文借鉴多通道的思路[15,21],构造了多通道同步方案结构。含谐波情况下单相电压跌落时的实验结果如图12所示。图12a为三相输入电源电压,其中C相电压跌落50%。图12b所示为提取出的基波正、负序幅值和相位,可以看到,本文所提方案可以消除谐波的影响,准确地提取出基波正、负序分量的幅值、相位角,且响应时间在 1个工频周期左右。

图12 含谐波单相电压跌落情况下实验结果Fig.12 Experimental results under single phase drop condition and containing harmonics

6 结论

针对电网不对称工况下基波负序分量对 SRFPLL的影响,以 SRF-PLL为基础,提出一种基于SAI-PLL的dq轴基波正、负序分量分离方法。该方法无需复杂的正、负序解耦或对称分量计算,在单同步坐标系下就实现了不对称工况下基波正、负序分量的分离提取,与同类方法相比,动态响应速度较快。本文给出的实验结果表明所提方法可以在电网不对称、频率跳变、电网电压畸变等工况下快速准确地提取电网 dq轴基波正、负序分量的幅值和相位角。对比研究表明,本文提出的方法具有动态响应速度快的优点,但当考虑电网畸变问题时,采用的多通道同步方案使得该方法结构稍显复杂。

[1] 涂春鸣, 李慧, 唐杰, 等. 电网电压不对称对D-STATCOM 的影响分析及抑制[J]. 电工技术学报, 2009, 24(8): 114-121.

Tu Chunming, Li Hui, Tang Jie, et al. Analysis and suppression of influence on D-STATCOM under unbalanced voltage of power system[J]. Transactions of China Electrotechnical Society, 2009, 24(8): 114-121.

[2] Teodorescu R, Blaabjerg F. Flexible control of small wind turbins with grid failure detection operating in stand-alone or grid-connected mode[J]. IEEE Transactions on Industrial Electronics, 2004, 19(5): 1323-1332.

[3] Song H-S, Nam K. Dual current control scheme for PWM converter under unbalanced input voltage conditions[J]. IEEE Transactions on Industrial Electronics, 1999, 46(5): 953-959.

[4] Blaabjerg F, Teodorescu R, Liserre M, et al. Overview of control and grid synchronization for distributed power generation systems[J]. IEEE Transactions on Industrial Electronics, 2006, 53(5): 1398-1409.

[5] Svensson J. Synchronisation methods for grid-connected voltage source converters[J]. IEE Proceedings of Generation, Transmission and Distribution, 2001, 148(3): 229-235.

[6] Guo X, Wu W, Chen Z. Multiple-complex coefficientfilter-based phase-locked loop and synchronization technique for three-phase grid-interfaced converters in distributed utility networks[J]. IEEE Transactions on Industrial Electronics, 2011, 58(4): 1194-1204.

[7] Kaur V, Blasco V. Operation of a phase locked loop system under distorted utility conditions[J]. IEEE Transactions on Industry Applications, 1997, 33(1): 58-63.

[8] Timbus A, Liserre M, Teodorescu R, et al. Synchronization method for three phase distributed power generation systems——an overview and evaluation [C]. IEEE 36th Power Electronic Specialist Conference, 2005: 2474-2481.

[9] Alepuz S, Busquets S, Bordonau J, et al. Fast on-line symmectrical components separation method for synchronization and control purposes in three phase in distributed power generation systems[C]. European Conference on Power Electronics and Applications, 2007: 1-10.

[10] Lee Sang-Joon, Kang Jun-Koo, Sul Seung-Ki. A new phase detecting method for power conversion systems considering distorted conditions in power system[C]. IEEE 34th Industry Application Conferences, 1999, 4: 2167-2172.

[11] Kim Yun-Hyun, Kim Kwang-Seob, Kwon Byung-Ki, et al. A fast and robust PLL of MCFC PCS under unbalance grid voltage[C]. IEEE Power Electronics Specialists Conference, 2008: 4712-4716.

[12] Rodriguez P, Teodorescu R, Candela I, et al. New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions [C]. IEEE 37th Power Electronics Specialist Conference, 2006: 1-7.

[13] 王宝诚, 伞国成, 郭小强, 等. 分布式发电系统电网同步锁相技术[J]. 中国电机工程学报, 2013, 33(1): 50-55.

Wang Baocheng, San Guocheng, Guo Xiaoqiang, et al. Grid synchronization and PLL for distributed power generation systems[J]. Proceedings of the CSEE, 2013, 33(1): 50-55.

[14] Rodriguez P, Pou J, Bergas J, et al. Decoupled double synchronous reference frame PLL for power converters control[J]. IEEE Transactions on Power Electronics, 2007, 22(2): 584-592.

[15] 李珊瑚, 杜雄, 王丽萍, 等. 解耦多同步参考坐标系电网电压同步信号检测方法[J]. 电工技术学报, 2011, 26(12): 183-189.

Li Shanhu, Du Xiong, Wang Liping, et al. A grid voltage synchronizaiton method based on decoupled multiple synchronous reference frame[J]. Transactions of China Electrotechnical Society, 2011, 26(12): 183-189.

[16] Yazdani D, Mojiri M, Bakhshai A, et al. A fast and accurate synchronization technique for extraction of symmetrical components[J]. IEEE Transactions on Power Electronics, 2009, 24(3): 674-684.

[17] Yazdani D, Bakhshai A, Joos G, et al. A nonlinear adaptive synchronization technique for grid-connected distributed energy sources[J]. IEEE Transactions on Power Electronics, 2008, 23(4): 2181-2186.

[18] Karimi-Ghartemani M, Iravani M R. A method for synchronization of power electronic converters in polluted and variable-frequency environments[J]. IEEE Transactions on Power Systems, 2004, 19(3): 1263-1270.

[19] Rodriguez P, Luna A, Ciobotaru M, et al. Advanced grid synchronization system for power converters under unbalanced and distorted operating conditions [C]. IEEE 32nd Annual Conference on Industrial Electronics, 2006: 5173-5178.

[20] Rodr´ıguez P, Luna A, Mu˜noz-Aguilar R S, et al. A stationary reference frame grid synchronization system for three-phase grid-connected power converters under adverse grid conditions[J]. IEEE Transactions on Power Electronics, 2012, 27(1): 99-112.

[21] Rodrí guez P, Luna A, Mujal R, et al. Multiresonant frequency-locked loop for grid synchronization of power converters under distorted grid condition[J]. IEEE Transactions on Industrial Electronincs, 58(1): 127-138.

[22] Yuan X, Merk W, Stemmler H, et al. Stationary frame generalized integrators for current control of active power filters with zero steady-state error for current harmonics of concern under unbalanced and distorted operating conditions[J]. IEEE Transactions on Power Electronics, 2002, 38(2): 523-532.

[23] Martin K. Complex signal processing is not complex [J]. IEEE Transactions on Circuits and System I: Regular Papers, 2004, 51(9): 1823-1836.

Synchronization Signal Detection Method in Synchronous Reference Frame Through Sinusoidal Amplitude Integrators

Du Xiong Liu Yandong Wang Guoning Sun Pengju Zhou Luowei

(State Key Laboratory of Power Transmission Equipment & System Security and New Technology Chongqing University Chongqing 400030 China)

The synchronization signal is necessary for the control of three-phase grid-tied converters, and so also is for the separation of positive and negative sequence components. Under unbalanced grid condition, the traditional synchronous reference frame phase-locked loop(SRF-PLL) can not work well because of the influence of the fundamental negative sequence component. By analyzing the characteristic of the SRF-PLL under unbalanced grid voltage condition, this paper proposes a separation method for the fundamental positive and negative sequence components which is based on the sinusoidal amplitude integrator phase-locked loop(SAI-PLL). Not only can this method eliminate the influence of the fundamental negative sequence component, it also can obtain the negative sequence component at the same time. In this paper, an overall block diagram of the SAI-PLL is shown, on the basis of its operation principle, a mathematical model is built and the parameters are designed. Compared with other existed methods, this method has advantages in the performance. The simulation and experimental results show that the proposed method can extract the synchronization signal quickly and precisely under the unbalanced and distorted conditions.

Asymmetric, synchronization signal extraction, phase-locked loop, synchronous reference frame, sinusoidal amplitude integrator

TM46; TM71

杜 雄 男,1979年生,教授,博士生导师,研究方向为变换器拓扑与控制,可再生能源发电。

国家自然科学基金项目(51277191),重庆市杰出青年科学基金项目(CSTC2012JJJQ90004)和输配电装备及系统安全与新技术国家重点实验室重点项目(2007DA10512711101)资助。

2013-07-11 改稿日期 2013-09-01

刘延东 男,1988年生,硕士研究生,研究方向为三相变流器控制。