一种基于FPGA的高精度同步信号生成设计与实现

2015-04-01陈昱均孙希延纪元法

陈昱均,孙希延,纪元法

(桂林电子科技大学 信息与通信学院,广西 桂林541004)

随着科学技术的日新月异,时间同步精度要求越来越高,而高精度的时间同步是国家时间服务的基本技术支撑。大多数实际工程应用并不要求系统所有终端的时间信息与国际标准时间相同,仅要求系统内各点的时间相同。从这个角度来看,时间同步可分为绝对时间同步和相对时间同步。绝对时间同步是指本地时间与国际标准时间同步[1],相对时间同步则只在某一工作系统中完成时间同步。绝对时间同步系统的实现方法较多,如北斗授时、GPS授时、搬运钟法。相对时间同步系统中,时间的基准由系统内部产生,经时间比对,将系统终端的时间与时间基准对齐,完成时间同步。

本研究设计一种实现相对时间同步的系统,以FPGA平台为基础,包含信号发射部分和信号接收部分。所采用的时间同步标准根据其发射部分与接收部分输出的秒脉冲信号是否同步来判断,信号发射部分生成基准的秒脉冲信号,信号接收部分生成同步的秒脉冲信号。由于系统采用扩频通信体制进行时间信号的传递,系统不仅可实现秒脉冲信号的同步,还可实现数据的传输。

1 时间同步原理

时间同步是一个时间传递的过程,在此过程中,调整任一端输出时刻的位置,可使时间达到同步状态。通过对时间信号的调制发送与捕获跟踪,可实现时间的传递。在接收机中,对时间信号的实时跟踪是一个与该接收信号同步复制过程,跟踪环路由载波跟踪环路与码跟踪环路2部分组成,它们分别跟踪接收信号中的载波与伪码。

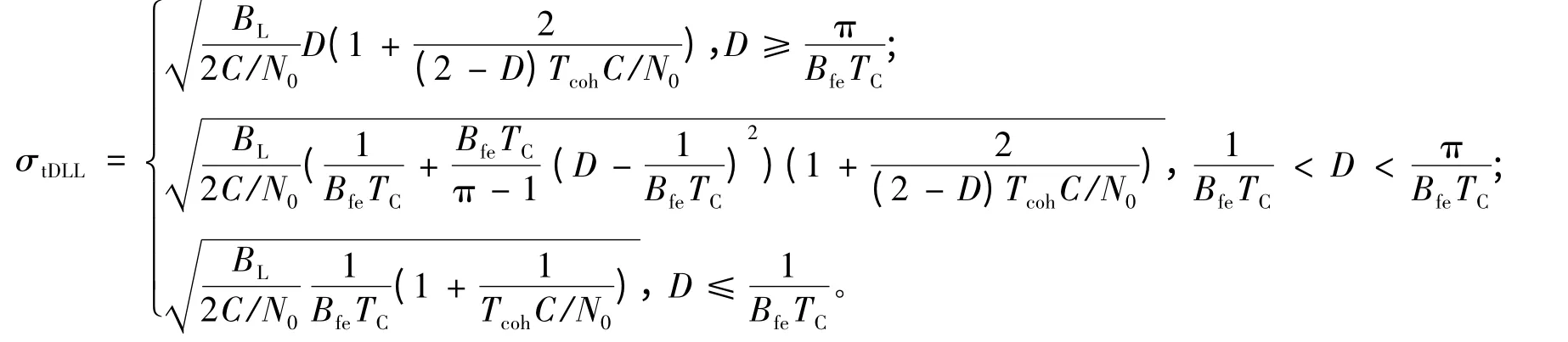

码跟踪环路的主要功能是保持复制的C/A码与接收的C/A码之间的相位一致。因此,对C/A码周期数累加,可输出时间信息,然后根据码环相位的测量误差估算时间同步的精度。排除多径和其他干扰后,码环的测量误差主要包括热噪声所致的码相位抖动,σtDLL为热噪声引起的码相位测量均方误差,则对于非相干前减后功率鉴相法,以伪码码片为单位的值σtDLL[2]可用下式进行估算:

其中,TC为伪码码宽。虽然减小相关器间距D可降低码环的热噪声,但其降低程度与射频前端带宽Bfe有关。若提高信号载噪比C/N0,并增加相干积分时间Tcoh,减小环路噪声带宽BL,则σtDLL越小,时间同步精度越高。

2 系统结构

2.1 信号生成模块

信号的调制发送主要在FPGA中进行,上位机通过串口或其他接口将数据信号发送至FPGA,在相同的工作时钟下,载波、伪码和数据信息同时产生。首先将数据信息与伪码进行模二加运算,实现数据码的扩频调制,再对载波进行BPSK调制[3],得到数字中频信号。

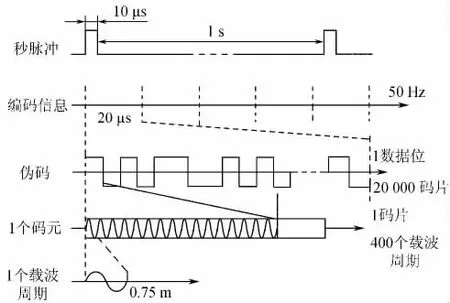

信号主体结构由载波、伪码、数据码3部分组成,外部提供10 MHz晶振输入,系统的整体工作时钟通过PLL环倍频到64 MHz。信号编码示意图如图1所示,其中串口输入的数据为32 bit,扩频码采用码速率为1 MHz的Gold码,伪码周期为1 ms,选择载波频率为400 MHz,是伪码速率的400倍。

图1 信号编码示意图Fig.1 Schematic diagram of signal coding

在FPGA平台内,秒脉冲(1 pulse per second,简称1PPS)信号的生成通过对码周期计数产生,码速率则通过码NCO[4]控制。码NCO的结构实质上是由一个加法器和寄存器组成的相位累加器,对于一个N位的码NCO,每秒增加的相位量会造成寄存器Mfc/2N次溢出,即周期信号的频率为:

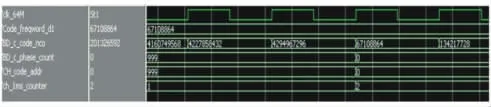

图2为码NCO累加仿真图,取N=32时,码频率控制字(即Code_freqword_d1)M=67 108 864,在寄存器BD_c_code_nco中对频率控制字进行累加,则一个码片所持续的时间是从累加到寄存器溢出时所持续的时间。当码片个数BD_c_phase_count累计到1000时,毫秒计数ch_1ms_counter加1。

图2 码NCO累加仿真图Fig.2 Code NCO cumulative simulation map

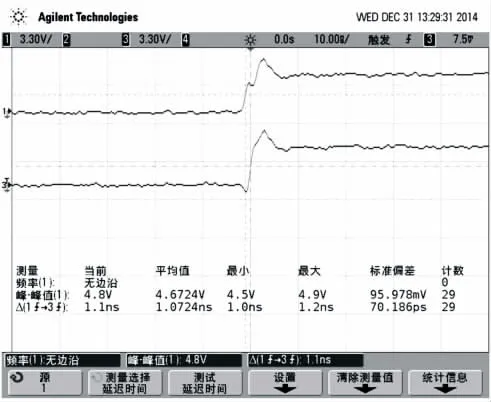

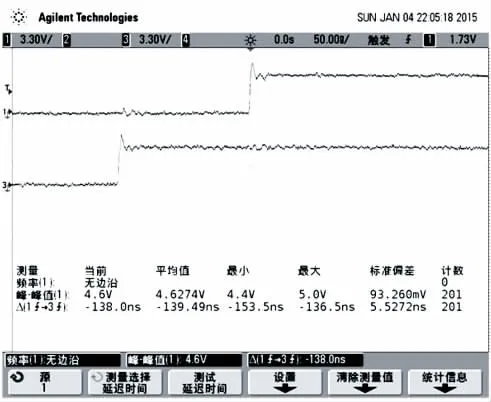

对码频率控制字累加溢出,寄存器内残余值为0的情况下,本地时钟计数产生1PPS信号。图3为信号产生端1PPS信号对比图,其中源1是对本地时钟计数,源3是对扩频码周期计数。信号输出通过不同的IO口导致硬件延时,绝对位置差值为1 ns,在示波器上输入2种方式产生的1PPS信号,结果表明信号分辨率基本无差别。

2.2 信号接收模块

图3 信号产生端1PPS信号对比Fig.3 1PPS signal comparison of signal modular

信号接收模块在硬件上通过DSP+FPGA共同完成,主要功能是实现基带信号的捕获与跟踪。捕获的目的是估算接收信号的载波频率和伪码相位,然后将这2个参数发送至跟踪环路,再对其进行初始化处理。根据伪码的良好自相关和互相关特性,信号捕获采用并行码相位捕获算法[5],数字中频信号与本地载波产生的正弦与余弦信号混频后,将混频后的值进行FFT处理,同时本地复制的C/A码也作FFT处理,然后将处理后的C/A码的值取其共轭复数并乘以混频作FFT处理的值,将所得的乘积经傅里叶反变换,得到在时域内的相关结果,最后对这些相关值进行检测,以判断信号是否存在。

由于需要对信号中的载波频率和伪码相位进行实时跟踪,跟踪环路以闭路反馈的方式运行。信号跟踪主要包括载波跟踪环路和伪码相位跟踪环路。载波跟踪的目的是实时产生与接收信号中载波信号相位一致的本地载波,然后与接收到的信号进行混频,实现对接收信号中的载波剥离。因为捕获的载波频率只是估计值,其精度较差,所以需要进入一个锁频环,使本地载波频率尽量与接收信号的频率接近,然后再结合锁相环进行载波相位的调整。可见,载波跟踪环路的设计是二阶锁频辅助三阶锁相环路[6]。码跟踪的目的是产生与接收信号中伪码相同码相位的本地伪码信号,然后对接收信号进行解扩,得到信号调制的数据码信息。跟踪时,首先根据捕获所得的伪码相位估计值生成超前、即时、滞后3路本地伪码信号,3路信号依次相差半个码片,然后分别与经正弦和余弦混频后的信号进行相关运算,并将相关后的信号进行积分,可得6路积分结果,将该结果送入码环鉴相器,鉴相器的值再经环路滤波后,调整数控振荡器的输出,进而调整本地伪码输出的频率和相位,最终形成闭环的伪码跟踪环路。

接收机的1PPS信号输出与信号产生端的1PPS信号输出是同一原理,不同之处是信号产生端码速率固定不变,而在接收端,由于受热噪声、晶振稳定度等影响,码跟踪环路中的相位值有差异,导致码频率控制字的生成不固定,继而影响码NCO的溢出时间。因为溢出时间不同,所以接收端的C/A码周期与生成端的C/A周期不完全相同。在帧同步后,DSP发送标志位给FPGA,让其开始对码周期数进行累加后输出1PPS信号。信号强度良好的情况下,伪码跟踪环路码相位测量误差均方差约为0.01个码片,码速率为1 Mchip/s时,距离误差为3 m左右,对应时间为10 ns,并在示波器上输出产生端与接收端1PPS信号。时间同步精度示意图如图4所示,在同源情况下,同步精度最大值为17 ns。

图4 时间同步精度示意图Fig.4 Schematic diagram of time synchronization accuracy

3 同源1PPS信号调整

接收端1PPS信号的输出通过C/A码周期计数产生,其本质是对C/A码码片计数。在码NCO中,32位寄存器溢出1次,码片数加1。1PPS信号输出时刻原理图如图5所示,M为码频率控制字,当寄存器的值处于A、B之间的X点时,下一个时钟上升沿到来后,寄存器的值将溢出,寄存器当前值会小于M,处于B、C之间的Y点。从X到Y所历经的时间为1个工作时钟,因为信号产生端寄存器的溢出值为0,所以B、Y所历经的时间也等同于B、Y两处的码相位,其时间段可看作码环相位的测量误差的主要部分,减小该部分误差即可提高同步信号的精度。

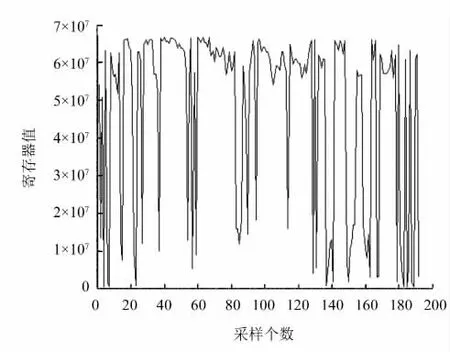

同源情况下,1PPS信号输出时对寄存器溢出后的当前值进行采集。寄存器溢出后的采集值如图6所示,其中寄存器值采集个数为192个,寄存器值的大小只在上下两端波动。根据这个特点,调整1PPS信号的输出时刻,即在寄存器的值小于1/2个码频率控制字时,输出1个1PPS信号,或在溢出后的第一个时钟时,输出1个1PPS信号,这样输出的1PPS信号就会在图5的B点左右波动很小的相位,进而提高了时间的同步精度。

图5 1PPS信号输出时刻原理图Fig.5 1PPS signal output timing diagram

图6 寄存器溢出后的采集值Fig.6 The acquisition value after register overflows

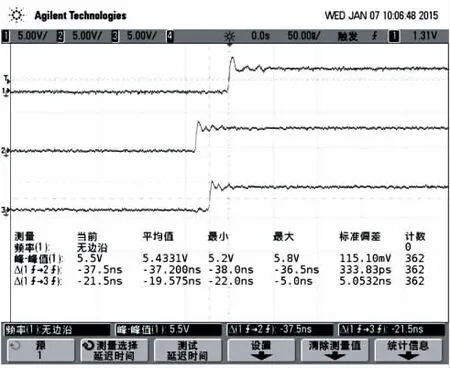

利用寄存器值的特点输出秒脉冲信号,并将信号输入至示波器。改进后的时间同步精度如图7所示,其中源1为信号产生端生成的标准秒脉冲信号,源2为接收机端改进后的秒脉冲信号,源3为未改进的秒脉冲信号,改进后的秒脉冲信号同步精度1.5 ns,未改进的秒脉冲信号同步精度仍为17 ns,精度得到了显著的提高。

图7 改进后的时间同步精度Fig.7 The improved time synchronization accuracy

4 结束语

利用伪码跟踪环路中本地复制的码相位与信号产生端码相位的对齐作为时间同步,设计了一种基于FPGA实现时间同步的系统结构。实验结果表明,在同源情况下,根据码NCO溢出值的特点对秒脉冲信号的输出时刻作调整,以提高同步精度,秒脉冲信号同步精度达到了1.5 ns。对于不同源的情况,可在寄存器的值溢出前延迟一定时间,使其处于寄存器的最大值时输出秒脉冲信号,则时间同步精度能提高到1个时钟内。

[1]王鹏.基于FPGA的绝对时间同步系统的设计研究[D].哈尔滨:哈尔滨工程大学,2007:2.

[2]谢钢.GPS原理与接收机设计[M].北京:电子工业出版社,2011:317-320.

[3]刘焕淋,向劲松,代少升.扩展频谱通信[M].北京:北京邮电大学出版社,2008:121-136.

[4]张进,苏凯熊.基于FPGA的数控振荡器的设计与实现[J].福州大学学报,2005,33(5):585-586.

[5]Van Nee R,Coenen A.New fast GPS code-acquisition technique using FFT[J].Electronics Letters,1991,278(2):39-40.

[6]Kaplan E.Understanding GPS:Principles and Applications[M].Second Edition California:Artech House,INC,2006:306.