激光雷达窄脉冲回波信号采集系统设计

2015-03-30杨腾蛟史建业叶凌云

杨腾蛟,史建业,丁 尚,叶凌云

(浙江大学 生物医学工程与仪器学院,浙江 杭州310027)

0 引 言

激光雷达具有视野宽、分辨率高、观测实时性好等优势,光电传感器将激光雷达脉冲回波转换为电脉冲。为了能最大程度地提取波形信息,建立被测目标的物理模型,需要对光电传感器产生的窄脉冲电信号进行高精度采样,为后续的目标回波识别打下基础。

目前,对于光电传感器窄脉冲信号的采集方案主要有光信号时间展宽、峰值保持、高速并行采样等技术。2012 年,盛桂珍等人通过门控峰值保持电路实现10~20 ns的电脉冲信号采集处理[1];2013 年,李嘉鸿等人运用8 片500 MSPS 模/数转换芯片,设计出分辨率12 位,采样率为4 GSPS的并行采样系统,应对8 ns 的传感器窄脉冲信号采集[2];2010 年,李玉生等人运用光信号时间展宽技术与高速并行采样技术,实现高达16 GSPS 的实时采样率,能够对4 ns 窄脉冲信号进行实时采样[3]。

峰值保持技术难以再现窄脉冲信号的细节,光信号时间展宽技术会使光信号产生一定失真。本文设计系统选用雪崩型光电传感器为前端,制定分辨率12 位,采样率8 GSPS的并行高速采样系统为设计目标,提出8×1 GSPS 的8 通道时间并行交错(time interleaved ADC,TIADC)信号采集方案,并利用数字补偿手段对TIADC 系统的采样通道进行校正。

1 激光雷达回波信号采集系统设计

激光雷达窄脉冲回波经过光学带通滤波器滤除掉光信号杂波,进入光电传感器转换为电信号,前端信号调理电路对该信号进行放大或衰减,以满足后续处理电路输入要求。功分电路负责将单端信号转换成多路差分信号输出,输入到各个采样通道。低抖动多相时钟发生器结合PCB 延时线建立系统时钟网络,保证采样通道间时钟相位差固定。高速缓存负责将高速数据流实时并行存储,实现信号重构与数字校正,将完整的数字波形输出。整个激光雷达窄脉冲回波采集系统如图1 所示。

图1 光电传感器窄脉冲采集系统Fig 1 Photoelectric sensor narrow pulse acquisition system

1.1 光电传感器选型

针对4 ns 脉宽,1 064 nm 波长的激光脉冲回波信号响应目标,本系统采用Thorlabs 公司的光电传感器APD310,其内部的主要光敏原件是雪崩型二极管,具备灵敏度高、暗电流小、线性度好等特点,各项指标均优于光电二极管与光电倍增管[4]。APD310 能够快速响应1 GHz 带宽的激光脉冲信号,其电脉冲输出具备连续的增益调节能力,免除后续设计前端信号调理电路的必要。前端带有光学带通滤波器,对850~1650 nm 波长范围内的激光有较好的响应能力,在1 064 nm 波长处,量子效率为40%。APD310 将SiAPD与低噪声的GaAs 场效应前置放大器相结合组成一体化光电传感器,探测灵敏度达到3×10-10W,非常适合窄脉冲激光测量。

1.2 并行采样设计

APD310 转换后的电脉冲信号,首先经过功分器转换成4 路单端信号,再通过传输线变压器(Balun)实现单端信号转差分信号。运用双传输线变压器串联方式来减轻相位失衡与幅度失衡对信号的影响。最后4 路差分信号通过差分T 型匹配节实现8 路分配,差分T 型匹配节模型如图2所示。

图2 差分T 型匹配节Fig 2 Differential T type matching section

8 路差分信号分别输入4 片双通道1 GSPS 采样率12 位分辨率的A/D 转换芯片ADC12D1000RF。该芯片拥有I 通道与Q 通道,可以工作在片内并行采样模式,将单片采样率提升为2 GSPS。系统硬件上以菊花链的方式组织4 片A/D 转换芯片,软件上通过配置一片A/D 转换芯片为主模式,其他A/D 转换芯片为从模式,实现多片A/D 转换芯片自同步。参考时钟(RCLK)从主A/D 转换输出去控制从A/D 转换数据时钟的相位,使得TIADC 系统中每一片A/D 转换芯片的数据输出都能与数据时钟对齐。多相时钟产生电路输出4 个相位相差45°的1 GHz 时钟,分别作为4 个A/D 转换芯片采样时钟,每一片A/D 转换芯片将获得的采样时钟一路送入I 通道,另一路反相后送入Q 通道。单片A/D 转换后端产生2 通道1GHz 并行12 位LVDS 数据,通过DEMUX 方式扩展为2 通道500 MHz 并行24 位LVDS 数据,即4 路12 位的并行LVDS 数据。系统采用Virtex5 FPGA 接收并缓存,4 片A/D 转换芯片分别由4 片FPGA 管理,每片FPGA 同时管理4 片16 位宽250 MHz DDRII芯片颗粒,保证数据流传输通道无瓶颈,实现采样数据实时存储。板上实时数据存储深度高达1G 采样点。并行采样设计方案如图3 所示。

图3 并行采样设计方案Fig 3 Parallel sampling design scheme

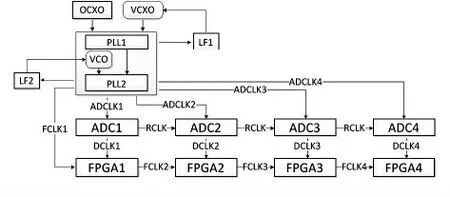

1.3 低抖动时钟网络设计方案

时钟网络核心芯片选取TI 的LMK04828B,支持JESD204B 时钟规范,拥有业界最低的时钟抖动性能,在带宽12 kHz~20 MHz 内仅有88 fs 的RMS 抖动。LMK04828B支持双锁相环设计,系统中第一级锁相环输入信号为恒温晶振(OCXO)的10 MHz 稳定时钟与压控晶振(VCXO)的100 MHz 不稳定时钟,第一级锁相环(PLL1)实现时钟的初步倍频,将100 MHz 时钟相位锁定到10 MHz 时钟相位上,为第二级锁相环(PLL2)参考输入端提供相位噪声极低的高频时钟源。第二级锁相环将芯片内部压控振荡器(VCO)产生的3 GHz 时钟与100 MHz 稳定时钟锁相,最后将相位稳定的3 GHz 时钟三分频输出,获得系统1 GHz 目标采样时钟。LMK04828B 具备输出14 路差分时钟的能力,选取片内同一时钟树下4 路ADCLK 差分时钟作为系统4 片A/D 转换芯片的时钟输入,选取一路FCLK 差分时钟作系统4 片FPGA 共用的同相位时钟。低抖动时钟网络设计方案如图4 所示。

图4 低抖动时钟网络设计方案Fig 4 Design scheme of low jitter clock network

其中RCLK 是相邻采样通道数据输出的参考时钟,DCLK 是A/D 转换芯片与FPGA 同步的数据时钟,LF 是环路滤波器。

相邻采样通道之间的固定相位差主要由采样时钟PCB延时线控制,时钟芯片内部提供可编程延时功能,但是受温度影响存在较大漂移,而且只能精确到10 ps 级,线性度不如PCB 延时线。对于固定微带线几何模型,PCB 走线延时仅为介电常数εr而非走线维度的函数[5]。当给定PCB 基板并给定εr条件下,不同阻抗线路的传播延迟常数是固定的。本文设计的并行采样系统具有8 通道,1 GHz 采样时钟频率,依据并行交错采样原理,需要设计相邻通道间隔125 ps固定相位差,结合微带线PCB 走线延时公式[6](1)可以计算出相邻通道采样时钟延时线的长度差

对于介电常数为4.0 的PCB 微带线,需要设计相邻通道采样时钟延时线长度差为0.919 in(1in=25.4 mm)。

2 信号采集通道时间失配校正方案

由于通道之间采样时钟相位控制偏差,导致采样时间的非均匀,这是并行高速采样中最重要的误差来源。时间失配意味着相邻采样点的采样时钟相位不是等间隔,会引入有规律的噪声频谱。本节通过后端数字校正手段来补偿时间失配误差。

在通道数为M 的TIADC 系统中,输入信号频率为f0的理想单音信号x(t)=ejω0t到TIADC 系统中。TIADC 系统的采样频率为fs,相邻通道间的采样周期为Ts,每个通道的采样周期为MTs。利用该TIADC 系统对输入信号x(t)进行采样,得到各个通道的采样数据xi(n),i=0,1,...,M-1,对拼接还原为单音信号的采样序列x(n)进行FFT。FFT结果中,在频率为ifs/M±f0处取值FAi,该值由时间通道失配产生的[7]。对FAi进行IFFT,得出M 个复数IAi。抽取复数序列IAi相角获得时间误差Δti。设Δti=riTs,ri为第i通道的时间误差与取样周期的比值,由于取样周期远大于时间误差,ri为分数。

时域变化值为ri,对应频域变化值为ejωri,并且经过该滤波器滤波后信号的幅值不能发生变化。基于此,需要设计一种频响为e-jωri的全通滤波器对时域的分数延时实时补偿。通过高速示波器精确测量各通道的采样时钟误差,据此就可以得到每一通道相应的全通滤波器ri值,但该滤波器无法直接在数字型器件FPGA 中实现。从物理可实现性角度出发,采用I 阶FIR 滤波器逼近目标,则传递函数为

ri<1,目标滤波器实际是一个分数延时滤波器。由于电子器件存在老化、温度变化等因素的影响,分数延时滤波器的系数具有不确定性。用多项式来逼近每一个分数延时滤波器的系数,将I 阶滤波器进一步分解成I 个p+1 阶子滤波器,如式(3)所示

3 仿真与实验验证

3.1 farrow 级联分数滤波器仿真与实验验证

系统设计的4 阶farrow 滤波器与级联仿真结构如图5所示。其中,Vi(i=0,1,2,3)为直接型FIR 滤波器。

图5 四阶farrow 滤波器与farrow 滤波器级联仿真Fig 5 Fourth order farrow filter and farrow filter cascaded simulation

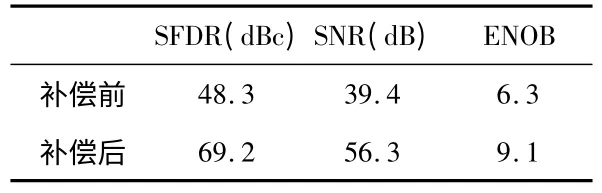

在simulink 中将4 个4 阶farrow 结构滤波器级联仿真,仿真条件:F(n)信号周期T=600 s,F(n)信号采样周期Ts=10 s,每个周期内60 个采样点,输入分数延时0.5Ts=5 s,得到仿真结果如图6 所示。图7 是系统输入498 MHz标准正弦波的条件下,引入farrow 分数延时滤波器补偿前后系统频谱图,在表1 中列出了分数延时补偿前后系统性能参数比较。

图6 分数延时补偿效果Fig 6 Fraction delay compensation effect

图7 分数延时补偿前后系统频谱图Fig 7 System spectrum before and after fraction delay compensation

表1 分数延时补偿前后系统性能比较Tab 1 System performance comparison before and after fraction delay compensation

3.2 激光窄脉冲回波采集实验验证

激光雷达样机验证阶段,系统采用MPL—III—1064 型脉冲激光器作为激光雷达激光源,产生1 064 nm 波长,4 ns 脉宽的激光脉冲。将激光打向平面墙体,激光雷达窄脉冲采集系统捕获如图8 所示脉冲回波,在4 ns 的有效脉宽内捕获了32 个采样点。

图8 4 ns 激光脉冲回波实时采样Fig 8 4 nanosecond laser pulse echo real-time sampling

4 结 论

针对激光雷达窄脉冲回波信号的检测与采集,本文设计并实现了一种解决方案,引入差分T 型匹配节、多片A/D 转换芯片自同步、级联型farrow 分数延时滤波器等手段,帮助8GSPS 并行采样系统的最终实现。仿真与实验结果表明:经过数字补偿后,该系统可以实现对4 ns 激光雷达窄脉冲回波信号的实时采样,在498 MHz 标准正弦波输入下,系统信噪比可以达到56.3 dB。

[1] 盛桂珍,赵 妍.超高速窄脉冲纳秒信号采集的实现与应用研究[J].长春工程学院学报:自然科学版,2012,13(2):31-32.

[2] 李嘉鸿,叶凌云,宋开臣.传感器窄脉冲信号的超高速采集系统[J].传感器与微系统,2013,32(12):104-106,109.

[3] 周 浩.基于数字后处理算法的并行交替采样ADC 系统[J].数据采集与处理,2010,25(4):537-543.

[4] Nassalski A.Silicon photomultiplier as an alternative for APD in PET/MRI applications[C]∥IEEE Nuclear Science Symposium Conference Record,2008:1620-1625.

[5] Muraoka S.PCB trace modeling and equalizer design method for 10 Gbps backplane[C]∥Electrical Design of Advanced Packaging and Systems(EDAPS)Symposium,IEEE,2011:1-4.

[6] 孟垂建.基于信号完整性的PCB 仿真设计与分析研究[D].哈尔滨:哈尔滨工程大学,2013.

[7] Sun H,Cao P.Researches on channel mismatch effects in timeinterleaved ADC system[C]∥Trans Tech Publications,Beihai,China,2013:655-657.

[8] Hunter M T,Mikhael W B.A novel farrow structure with reduced complexity[C]∥IEEE Circuits and Systems,2009:581-585.