基于可编程逻辑器件的计分器系统设计

2015-03-27琚新刚郭海鸥

琚新刚, 郭海鸥

(河南教育学院 电路与系统重点学科组,河南 郑州 450046)

基于可编程逻辑器件的计分器系统设计

琚新刚, 郭海鸥

(河南教育学院 电路与系统重点学科组,河南 郑州 450046)

用可编程逻辑器件设计的计分器,本质上是一个具有高集成度的单芯片系统.考虑到实际操作中按键抖动问题,采用了易控制的计数器延时方案,实现防抖,时序仿真显示,系统可以很好地完成计分功能.

计分器;单芯片系统;防抖

在许多比赛中,常用到计分器.计分器包括计数器和用于数码显示的驱动电路,这两个电路可以用单片FPGA实现,即一个小型的SOC.

根据需要,以2位数(十进制)计分器为例,计分器计数范围0~99,其输入包括增、减、复位等控制.增控制信号为高电平时,计分器显示的数字加1,减控制信号为高电平时,计分器显示的数字减1,复位控制信号为高电平时,计分器复位,显示数字为00.

图1 计分器系统框图Fig.1 System block diagram of scoring device

1 系统构成

计分器电路由计数器和一个7段数码管驱动电路,即译码器组成.增、减、复位、时钟4个1位的输入端,两组4位的输出端如图1.

2 系统设计原理

两位BCD数字计数器用以记分,两个7段数码管用于显示分数,两个译码器把每个BCD转换为7段数码显示.考虑到使用中的误操作情况,复位信号可设计为长按一段时间后作用,故复位用一个3位复位计数器[1].

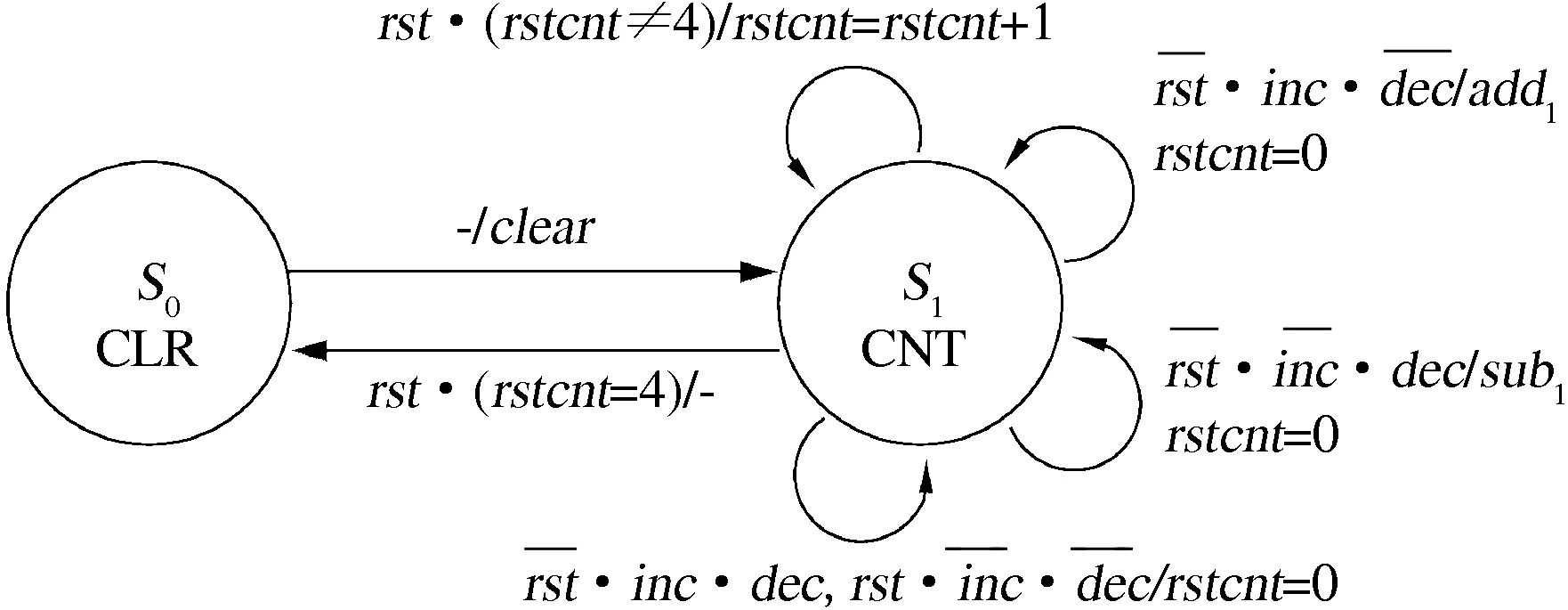

该计分器系统的状态图见图2,控制器是一个有限状态机,只有两个状态S0和S1,初始状态S0时,BCD计数器清零,复位计数器也清零,随后进入下一个状态S1,此状态中计数器开始计数.在每个时钟周期,根据输入信号计数器加1或减1;如果有复位信号rst,则复位计数器rstcnt加1;若rstcnt已经为4,且在第5个时钟周期时仍存在复位信号,则系统由状态S1变为状态S0,当inc信号出现,而dec信号未出现时,BCD计数器递增计数,图中右上角弧线处的add1表示BCD计数器递增计数;当dec信号出现,而inc信号未出现时,BCD计数器递减计数,图中右下角弧线处的sub1表示BCD计数器递减计数.在任何时钟周期内,只要rst信号没有出现,则rstcnt计数器就清零.如果inc信号、dec信号同时出现或同时不出现,则rstcnt计数器也清零,而BCD计数器则不变.

3 仿真结果分析

计分器电路的仿真结果如图3所示,Segment7dl和segment7d2分别表示两个7段显示器,为无符号7位向量.系统具备计分功能.对于不可避免的毛刺信号,考虑到手动按键的抖动和其他干扰,系统需引进去抖动和干扰的功能模块.

图2 系统状态图Fig.2 System status diagram

图3 仿真结果Fig.3 Simulation result

4 去抖动

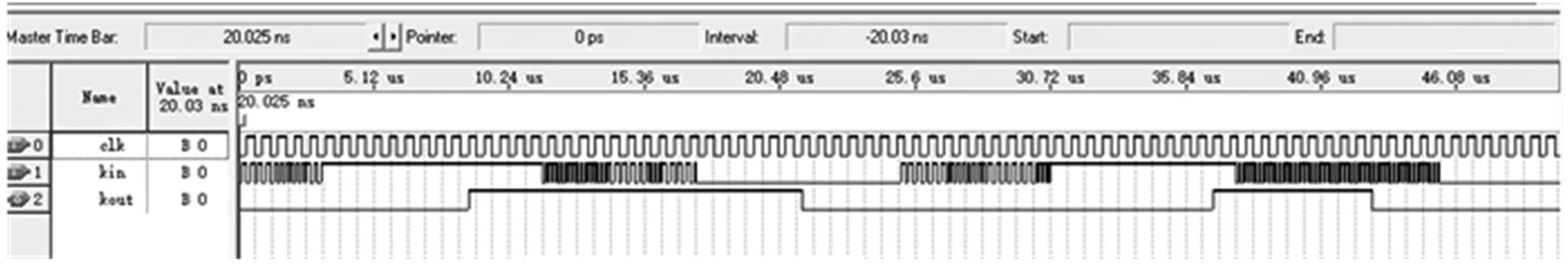

分别用两个计数器对输入信号的高电平和低电平的持续时间(脉宽)进行计数(在时间上是同时但独立计数)[2].只有当高电平的计数时间大于某值(比如9),才判为遇到正常信号,输出1;若低电平的计数时间大于某值(比如7),则输出0(图4).由波形可见,输出信号脉宽比逻辑方式输出的信号要宽得多,实现了通过计数延时,消除抖动和干扰的影响.

图4 防抖结果Fig.4 Result of anti shake results

5 结论

计分牌按键防抖的延时采用计数器的方式,计分电路获取增减信号由正常信号高电平的脉宽和工作时钟频率共同决定,不单纯由时钟决定,易控制,效果好,只是耗用资源较多.工作时钟CLK的频率大小要视干扰信号和正常信号的宽度而定,对于类似键抖动产生的干扰信号,频率可以低一些,几十kHz赫兹即可;若是比较高速的时钟信号,则可利用FPGA内的锁相环,使CLK能达到400 MHz以上.此外,用于延时的计数器位宽和计数值都可以根据具体情况调节,很好地实现了实际计分功能.

[1] CHARLES H R, JR LIZY K J. Digital Systems Design Using VHDL[M].2nd Ed. Beijing:Cengage Learning,2008:156-157.

[2] 潘松,黄继业.EDA技术实用教程[M].4版.北京:科学出版社,2010:259-261.

Design of Scoring System Based on Programmable Logic Device

JU Xin-gang, GUO Hai-ou

(KeyDisciplineGroupofCircuitandSystem,HenanInstituteofEducation,Zhengzhou450046,China)

The scoring system based on programmable logic device is essentially a system on a chip with a high degree of integration. Considering that the key problem of jitter in the actual operation, an easily controlled counter delay scheme is used, and anti shake is achieved. The timing simulation shows that the system can complete the scoring function well.

scoring device; SOC; anti shake

2014-12-20

河南省科技攻关重点项目(142102210422)

琚新刚(1973—),男,河南辉县人,河南教育学院电路与系统重点学科组副教授,主要研究方向:EDA技术.

10.3969/j.issn.1007-0834.2015.01.002

G642.0

1007-0834(2015)01-0004-02