基于FPGA的工业数字摄像机系统的设计

2015-03-21刘慧忠连钰洋裴之勇

汤 伟,刘慧忠*,连钰洋,王 震,裴之勇

(1.陕西科技大学 电气与信息工程学院,陕西 西安710021;2.陕西科技大学 轻工与能源学院,陕西 西安710021)

1 引 言

在当今的信息化社会里,工业数字摄像机不仅应用于工业检测、印制板检测、食品饮料检测等工业行业,也应用于交通、电子警察系统、医学影像采集等生活中,更可以在危险场合中进行视频监控等。工业数字摄像机是通过外部信号触发采集,实现实时的现场图像采集,它具有采集图像方便、传输迅速、成像清晰等特点。传统的工业摄像机利用计算机对图像传感器进行配置控制,有着灵活性差、实时性差和可靠性差等缺点[1]。将工业数字摄像机和飞速发展的FPGA(Field-Programmable Gate Array)理论结合起来,形成新的工业数字摄像机,具有高精度、速度快和灵活性强的优势,在采集原图像信息的同时还可以对原图像信息进行处理[2]。

2 系统原理及总体设计结构

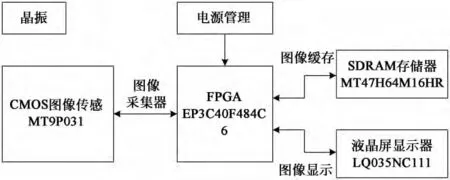

基于FPGA 的工业数字摄像机系统主要由3部分组成:图像采集部分、FPGA 核心控制、图像实时显示。图像采集就是把光信号转换为电信号,将模拟图像转化为数字图像,常见的图像传感器有CMOS 图像传感器和CCD 图像传感器。CDD 图像传感器一般用于对图像要求比较高的场合,其价格昂贵;CMOS 图像传感器采集的图像清晰,价格便宜。FPGA 完成对图像传感器的控制、图像的转化、图像缓存、接口控制以及显示控制。图像的输出结果通过液晶屏显示出来。

本设计选用美国美光(Micron)公司的CMOS图像传感器MT9P031。FPGA 采用Altera公司的EP3C40F484C6芯片,SDRAM 存储器选用Micron 公司的MT47H64M16HR 存储器,液晶屏显示器选用SHARP 公司的3.5in(1in=2.54cm)液晶屏LQ035。工业数字摄像机的硬件系统结构如图1所示。

图1 工业数字摄像机的系统结构图Fig.1 System structure of industrial digital cameras

3 工业数字摄像机的系统设计

工业数字摄像机的系统的主要设计集中在FPGA 的编程开发上,FPGA 主要有以下4个模块:图像传感器的配置模块、图像数据格式转化模块、SDRAM 存储器的控制模块和液晶屏的控制模块。

3.1 图像传感器电路设计及其FPGA配置模块

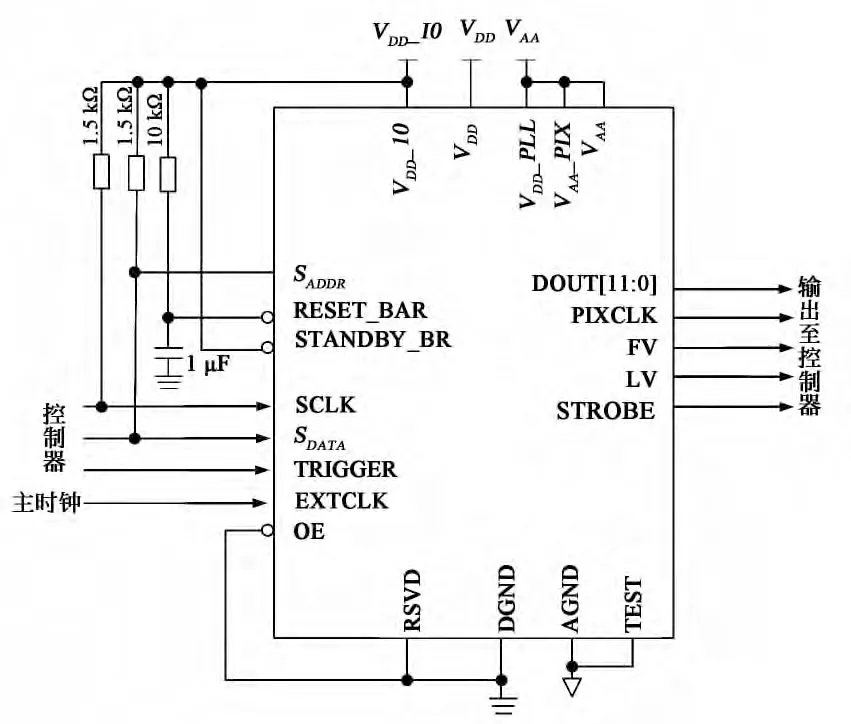

本设计采用Micron公司的MT9P031CMOS图像传感器,其是一种具有2 592H×1 944V 有源像素阵列的1/2.5in的CMOS图像传感器,采用10mm×10mm 尺寸的iLCC-48引脚封装,有48个引脚。MT9P031 的外围电路如图2 所示,控制器通过SCLK、S_DATA、TRIGGER 引脚配置图像传感器,12位像素数据通过D_OUT[11∶0]引脚输出[3-4]。

图2 图像传感器MT9P031的外围电路图Fig.2 External circuit of the image sensor MT9P031

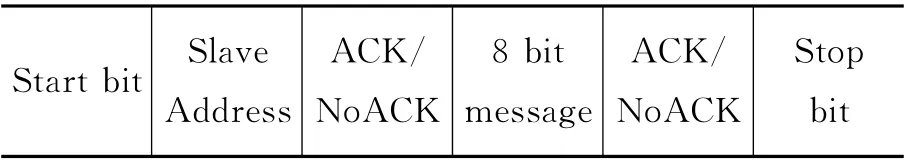

图像传感器MT9P031 的相关操作是通过I2C(Inter-Integrated Circuit)串行接口总线读/写对应寄存器来完成操作的。I2C 总线是飞利浦公司推出的一种总线技术,它有两根双向信号线,一根是数据线SDA,另一根是时钟线SCL。I2C 接口总线定义了几种不同的传输代码,如表1。

Start bit是起始位,时钟线为高电平,数据线由高电平转低电平时有效;Slave Address是器件地址,包括7个地址位和1个方向位,最低有效位为“0”时表示写模式,为“1”时表示读模式;ACK/NoACK 是应答位,每一个被传送的字节后面都必须跟随一位应答位;8bit message是数据,每次传送8 位数据,其后是应答位;Stop bit是停止位,时钟线为高电平,数据线由低电平变为高电平时有效[5-6]。

表1 I2C串行接口传输代码Tab.1 Serial interface transmission code

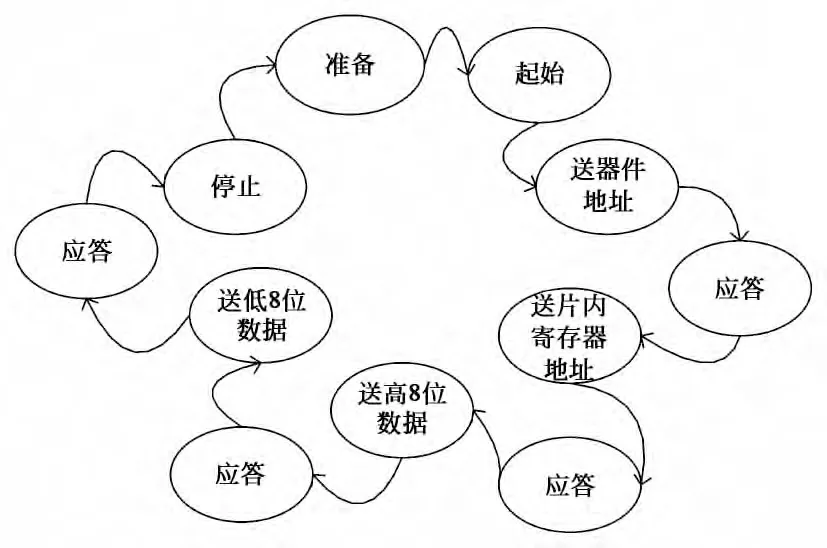

图像传感器MT9P031 输出12 位像素数据时,同时输出帧有效信号和行有效信号,当二者都是高电平时,像素数据有效。MT9P031图像传感器中共有256个寄存器,寄存器的设置决定了图像传感器的工作状态。图像传感器配置模块通过I2C总线接口的SCL 信号和SDA 信号设置图像传感器中寄存器的值,进而控制图像传感器的工作状态。状态机转换如图3所示。

图3 图像传感器配置模块状态机转换图Fig.3 Image sensor configuration module state machine transition diagram

图4 I2 C串行总线写操作时序仿真图Fig.4 Simulation diagram of I2 C serial bus write operation

图像传感器与总线之间通过高阻态的形式相连,故应答也是高阻。图像传感器的地址是BAH,向寄存器R0x2D 中写入数据0x0000F,其时序仿真图如图4所示。

3.2 图像数据转换模块

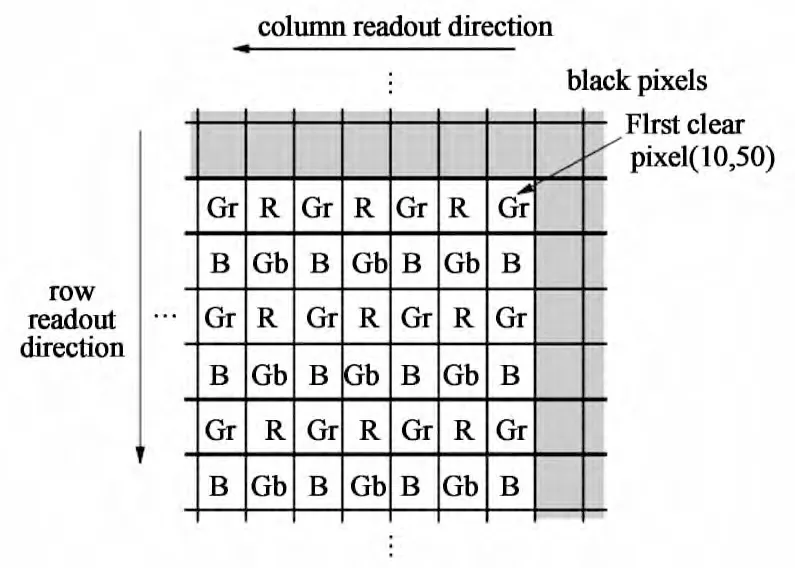

图像传感器MT9P031输出的每个像素点是12bits的Bayer格式数据。Bayer数据格式是一种未经过处理加工的数据格式,每个像素点只包含RGB颜色空间中的一种颜色分量。其颜色分布形式如图5所示。为了得到RGB图像,需要利用其周围像素点的相关性估算出缺少的颜色分量,本设计中采用线性插值算法的方式估算缺少的颜色分量。Bayer格式中,奇数行是G、B 分量,偶数行是B、G 分量,偶数列是G、B 分量,奇数列是R、G 分量。对于一个2×2的插值窗口,有四种可能的插值情况,分别为:

(1)R=R12, G=G11+G22, B=B21;

(2)R=R11, G=G21+G12, B=B22;

(3)R=R22, G=G12+G21, B=B11;

(4)R=R21, G=G22+G11, B=B12。

算法的实现采用Altera公司的行缓存区IP核Altshift_taps实现。具体思路就是设置两个行列计数器,列计数器从场有效信号到达后第一个有效数据开始计数,计数到一行数据后,行数器加一,列计数器重新计数。由行列计数器的奇偶判断4种插值情况。

图5 Bayer图像数据格式Fig.5 Bayer image data format

3.3 SDRAM 存储器配置模块

本设计采用Micron公司的MT47H64M16HR DDR2SDRAM(Double Data Rate 2SDRAM)。

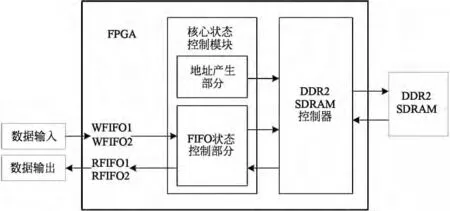

该存储器的位宽为16 位,单个BANK 有8M个 单 元,共 有8 个BANKS[7]。存 储 器 配 置 模块主要包括以下几个部分:DDR2SDRAM 控制器IP核、状态控制模块和缓存模块。其原理图如图6所示。

图6 SDRAM 存储器配置模块原理图Fig.6 SDRAM memory configuration module schematics

模块输入数据时截取图像转换模块输出数据中的高10 位,这样每个像素的RGB 宽度为30位。采用两个写FIFO(WFIFO1和WFIFO2)将每个像素的数据写入DDR2 存储器中,其中WFIFO1的WR1_DATA[15∶0]数据总线的[9∶0]位数据送红色分量(R[9∶0]),[14∶10]位数据送绿色分量的高5位(G[9∶5]),WFIFO2的WR2_DATA[15∶0]数据总线的[9∶0]位数据送黑色分量(B[9∶0]),[14∶10]位数据送绿色分量的低5位(G[4∶0])。从DDR2器件读取数据时,RFIFO1中RD1_DATA[15∶0]的[9∶0]位送红色分量通道,RFIFO2 的RD2_DATA[15∶0]的[9∶0]位数据送黑色分量通道,RD1_DATA[15∶0]的[14∶10]位与RD2_DATA[15∶0]的[14∶10]位合并成10位送绿色分量通道,最后将这3个R、G、B颜色分量送LCD 控制器模块,供LCD 液晶屏显示。DDR2控制器哥。

ALTERA 公司提供的IP核DDRII SDRAM controller with ALTMEMPHY,读写FIFO 存储器通过Quartus II软件中MegaWizard 工具生成,时钟由PLL倍频所得。

3.4 液晶屏显示及FPGA配置模块

LQ035一 款3.5in 彩 色TFT LCD,具 有320RGB×240的高分辨率,接口支持数字24位RGB/串行RGB/CCIR656/CCIR601等标准。

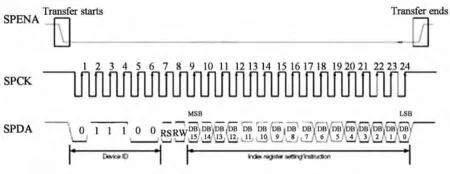

LQ035 的 控 制 采 用SPI(Serial Peripheral Interface--串行外设接口)总线,其时序如图7。液晶屏控制器通过SPI接口对LQ035的内部寄存器进行读写,从而控制LQ035液晶屏的显示模式。完成一次SPI接口总线的读写需要24个时钟周期,前6个位数据为设备号,第7位为数据与命令的区分位,第8位为读写位,[15∶8]位为寄存器地址位,[7∶0]位为数据位。SPI接口与I2C接口总线不同,其没有应答位。其状态转换图与图像传感器的配置类似,由于篇幅原因,不再详细叙述。

图7 SPI接口时序图Fig.7 SPI Interface Timing Diagram

4 系统测试结果

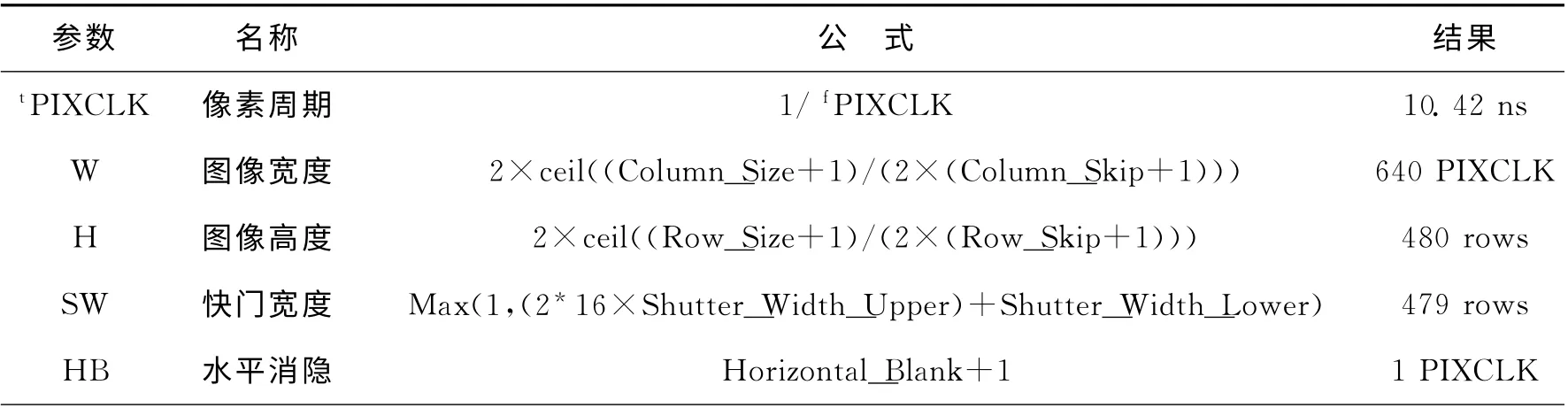

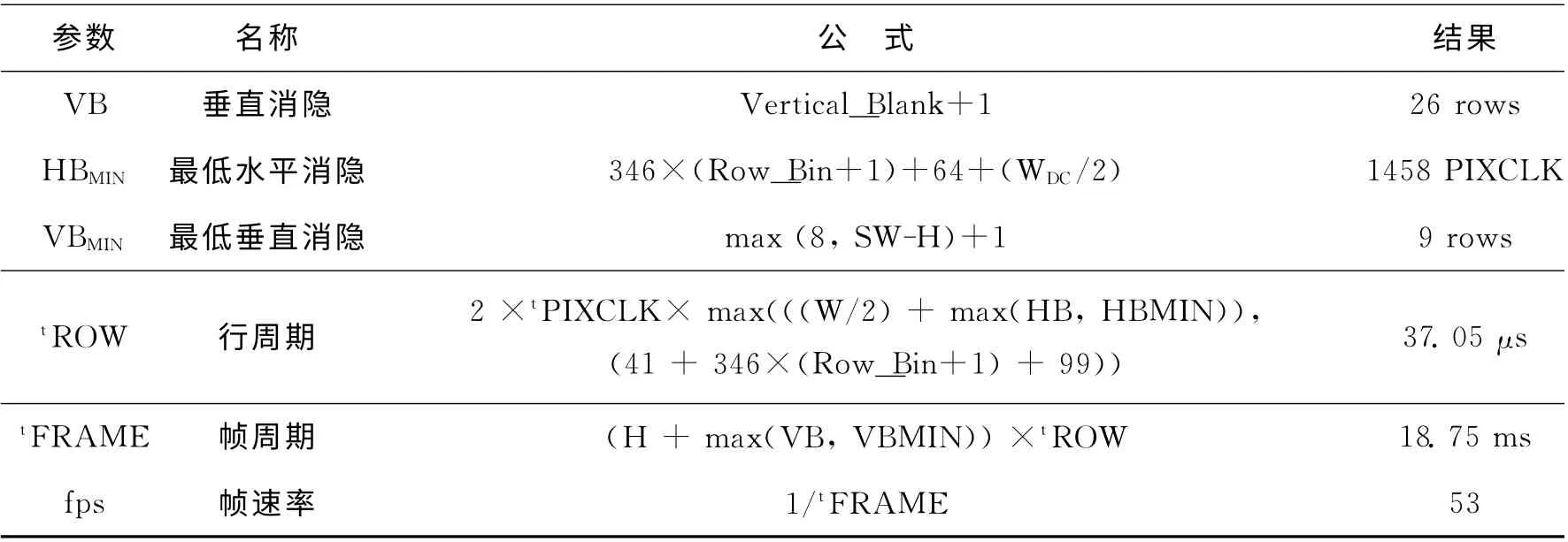

本设计中图像传感器MT9P031的工作模式采用VGA 640×480 分辨率binning模式,向图像传感器寄存器写入数据控制MT9P031的工作状态。图像传感器MT9P031外部输入25 MHz的时钟,其通过片上锁相环倍频达到96 MHz。图像传感器工作时各数据计算结果如表2。

表2 MT9P031行周期和帧周期Tab.2 Row time and frame time of MT9P031

续表

其列有效像素(Column_Size)有2 599个,行有效像 素(Row_Size)有1 919 个,Column_Skip 和Row_Skip寄存器为3,Horizontal_Blank寄存器为0,Vertical_Blank为25,Row_Bin与Column_Bin确定HBMIN为1 458PIXCLK。最后得出其行周期为37.05μs,帧周期为18.75ms,每秒可产生53帧图像。

图8 系统测试结果图Fig.8 System test results figure

完成系统设计后,使用Quartus II软件编译设计代码。本测试采用Altera 公司的Cyclone III系列芯片EP3C40F484芯片,编译结果显示共需约5 000个逻辑单元,占芯片总量的13%,3 704个寄存器和117个引脚,占芯片总量的35%。将设计代码下载到FPGA 芯片中后,系统开始采集并显示图像。图8为系统所拍摄的室内图像,测试结果可看到系统实时图像显示清晰,画面稳定,功能符合设计要求。

5 结 论

基于FPGA 的工业数字摄像机系统采用FPGA 芯片作为数据核心处理单元,CMOS 图像传感器负责获取图像数据,FPGA 完成对图像传感器芯片的控制、数据转换、数据缓存及接口控制,VGA 控制器完成实时图像的输出和显示。一个完整的工业数字摄相机不仅包括图像的采集显示,还包括图像的及时处理算法(如滤波处理等),这些处理算法数据运算量大,同时实时性要求高,基于FPGA 的工业数字摄像机可满足以上传统摄像机达不到的要求。同时该系统设计灵活,在设计过程中采用了Altera IP核,简化了设计过程,还可将不同的处理算法移植到该系统,满足不同的场合不同的算法处理,适合应用到多种工业现场。

[1] 樊博,王延杰,孙宏海,等.FPGA 实现高速实时多端口图像处理系统的研究[J].液晶与显示,2012,28(4):620-625.Fan B,Wang Y J,Sun H H,et al.High speed real-time multiport image processing system realized on FPGA[J].Chinese Journal of Liquid Crystals and Displays,2012,28(4):620-625.(in Chinese)

[2] 刘波文,张军,何用.FPGA 嵌入式项目开发[M].北京:北京航空航天大学出版社,2012:117-331.Liu B W,Zhang J,He Y,et al.FPGA Embedded Project Development[M].Beijing:Beihang University Press,2012:117-331.(in Chinese)

[3] 刘延飞,郭锁利,王晓戎,等.基于Altera FPGA/CPLD 的电子系统设计及工程实践[M].北京:人民邮电出版社,2009:252-288.Liu Y F,Guo S L,Wang X R,et al.Electronic System Design and Engineering Practice Based on Altera FPGA/CPLD [M].Beijing:Posts &Telecom Press,2009:252-288.(in Chinese)

[4] 朱奕丹,方怡冰.基于FPGA 的图像采集与VGA 显示系统[J].计算机应用,2011,31(5):1258-1261.Zhu Y D,Fang Y B.Image acquisition and VGA display system based on FPGA[J].Journal of Computer Applications,2011,31(5):1258-1261.(in Chinese)

[5] 左事君,刘新朝,何巧珍,等.基于FPGA 的高清视频采集与显示系统设计[J].电子技术应用,2011,37(06):56-58.Zuo S J,Liu X C,He Q Z,et al.Design of high definition video acquisition and display system based on FPGA[J].Application of Electronic Technique,2011,37(06):56-58.(in Chinese)

[6] 郭永彩,苏渝维,高潮.基于FPGA 的红外图像实时采集系统设计与实现[J].仪器仪表学报,2011,32(3):514-519.Guo Y C,Su Y W,Gao C.Design and implementation of real-time infrared image collection system based on FPGA[J].Chinese Journal of Scientific Instrument,2011,32(3):514-519.(in Chinese)

[7] 郑佳,李永亮,李娜.基于FPGA 的DDR 控制器的实现[J].无线电工程,2007,37(10):23-25.Zheng J,Li Y L,Li N.Implementation of DDR controller based on FPGA[J].Radio Engineering,2007,37(10):23-25.(in Chinese)