一种基于FPGA的DDS信号源实现

2015-03-15张林行尚小虎赵美聪

张林行,尚小虎,赵美聪,刘 阳

一种基于FPGA的DDS信号源实现

张林行,尚小虎,赵美聪,刘阳

摘要:鉴于信号源在测试和实验领域的广泛应用,设计了一种基于现场可编程门阵列(FPGA)的直接数字合成(DDS)信号源。设计中单片机作为控制芯片,完成输入和显示操作并把波形操作指令传输给运算器FPGA。在运算器FPGA中,通过查找表产生数字波形编码,经过D/A和滤波电路实现波形的模拟输出。经测试,该信号源输出幅值精度达到1mV,频率输出范围1MHz-1MHz,频率控制精度0.01%,控制灵活,满足设计要求。

关键词:直接数字合成;现场可编程门阵列;锁相环

0 引言

信号发生器在测试和实验领域有着广泛的应用,特别在通信、电子测量仪表、雷达等电子系统的研发和设计过程中有着不可替代的作用,因此,设计制作一台高性能的信号发生器具有很高的实际价值。直接数字频率合成(Direct Digital Synthesis,DDS)技术最开始由美国学者J. Tierney,C. M. Rader和B. Gold在1971年提出[1],它是以数字信号为基础,从相位的角度出发直接合成所需波形的一种新的全数字频率合成技术。与传统的频率合成技术相比,DDS具有频率分辨率高、频率切换速度快和相位连续变化等优点。

现场可编程门阵列(Field Programmable Gate Arrays,FPGA)是目前被广泛采用的一种可编程信号处理器件[2]。FPGA具有设计灵活性大、开发周期短、集成度高、可重复编程、内部资源丰富等优点。利用DDS原理在FPGA平台上开发高性能的信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,还能根据要求在线更新配置,系统开发趋于软件化、自定义化[3-4]。

本文使用Altera公司的Cyclone IV系列FPGA芯片实现信号发生器的设计,方便的实现常用波形的输出,且频率,幅度,相位和占空比调节准确方便。

1 DDS工作原理

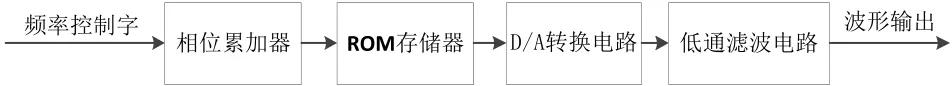

DDS是从相位概念出发直接合成所需要波形的一种新的频率合成技术。一般包括系统时钟、相位累加器、ROM查找表、D/A转换器和低通滤波器(Low Pass Filter,LPF)。根据ROM表存储的不同波形数据可以产生任意的波形,其原理如图1所示:

图1 DDS原理图

输入的频率控制字K称为相位步进量,作为相位累加器的增量,系统时钟则对相位累加器、ROM查表和D/A转换器提供时序控制。相位累加器由N位全加器和N位累加寄存器级联而成,在系统时钟的控制下对频率控制字的二进制码进行累加运算,将累加器的值作为ROM查找表的地址数据,相位累加器每一个周期的累加便完成一个波形采样值的查表和输出,这个周期就是DDS产生波形的频率周期。由此可知DDS的信号输出频率为公式(1):

频率分辨率为公式(2):

由公式(1)可以看出,输出频率与频率控制字和系统时钟成正比,为增大频率的输出范围,本设计通过改变频率控制字K和系统时钟来改变输出频率[5]。

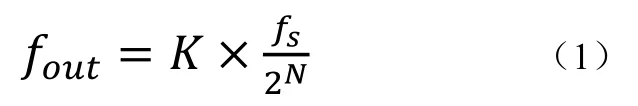

2 信号发生器系统组成

本设计整体原理如图2所示:

图2 信号发生器整体原理图

2.1控制电路设计

本设计采用STC12LE5A60S2单片机作为主控芯片。如图2所示,为交互方便,采用4*4按键和TFT彩屏来设置和显示当前信号波形、频率、幅度、占空比等信息。单片机通过串行传输数据控制FPGA,传达波形、频率、幅度、占空比等控制指令。

2.2运算电路设计

FPGA使用Cyclone IV E系列的EP4CE10E22C8芯片,在芯片内部编程完成PLL模块、相位累加器模块、ROM模块和幅度控制模块等的构建。

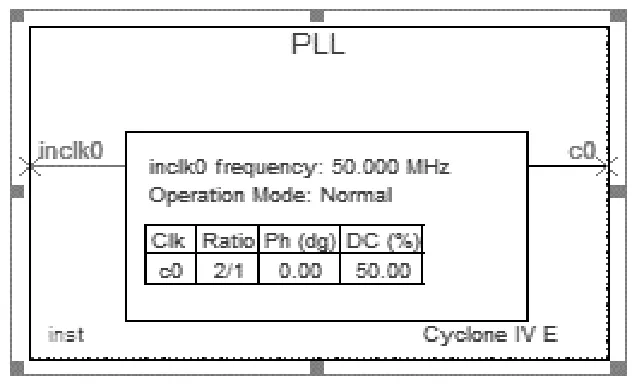

2.2.1PLL模块

由公式(1)可知,想要提高输出频率的上限值,必须要提高系统的运行时钟。本系统的外部晶振频为是50M,为提高系统内部运行时钟,本设计中调用quartus II软件内的宏功能模块ALTPLL来实现时钟的倍频,考虑到后级D/A芯片的反应时间,PLL的设计为2倍频,输出时钟为100M。根据奈奎斯特准则,允许输出的最高频率为,但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际输出的最高频率仅能达到0.4[6]。最终生成的PLL电路如图3所示:

图3 PLL电路

仿真结果如图4所示:

图4 PLL仿真图

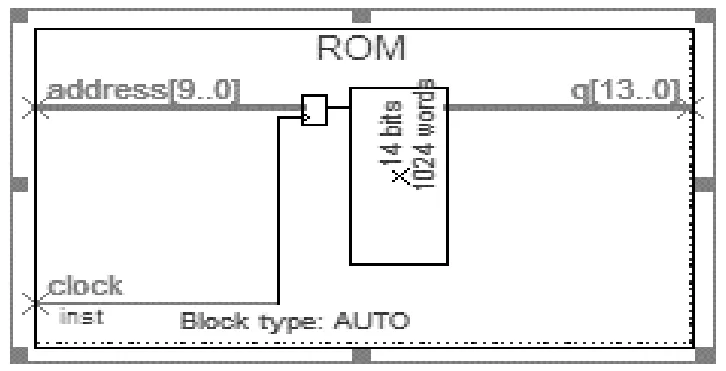

2.2.2ROM模块

首先,是按照一定的采样点数(用M表示)将一个周期波形的数据存于ROM表中,表中的数据代表着一个周期波形的幅度信息,每个地址对应一个相位点的幅度值。采样值可以通过MATLAB软件实现,正弦波采样程序如下所示。

index=linspace(0,2*pi,1024);

a=fix(8191*(sin(index)+1)+0.5);

plot(index,a);

本设计选取采样的点数,由公式(1)可知。

利用quartus II软件中的宏功能模块ROM 来实现ROM的设计,将MATLAB生成的波形数据保存为.mif格式,加载到ROM中,最终生成的ROM电路如图5所示:

图5 ROM电路

2.2.3相位累加器

相位累加器是信号发生器设计中最主要的部分。由公式2可知,在系统时钟为100M时,输出频率最小为100K,考虑到D/A需要输入一定量的采样点数才能还原出数字化的波形,因此频率控制字K不能取的很大,本设计输出频率最高为1M,即K最大取10。这样的话,频率输出范围是100K到1M,显然范围太小。在设计相位累加器时,本系统取N和K为30位,其中N的高10位作为地址数据进行寻址,频率控制字高10位作为整数部分,低20位作为小数部分[7],这样频率分辨率就达到0.0931Hz,结合控制精度需要达到0.01%,规定系统时钟为100M时的频率输出范围是1K到1M。

当然,增加N和K的位数还可以继续扩大频率的输出范围,但同样也会占用系统大量的资源,为了获得较大的频率输出范围,本设计通过不同频段的输出频率来调整系统时钟。即在输出频率为1K到1M时,系统时钟选择100M;在输出频率为1Hz到1K时,系统时钟选择100K;输出频率为1mHz到1Hz时,系统时钟选择100Hz。系统时钟的选择通过一个选择器分频实现。这样,总的频率输出范围就是1mHz到1M,控制精度达到0.01%。由公式(1)可知公式(3):

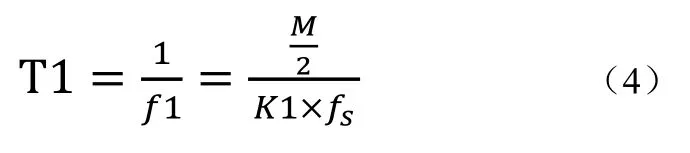

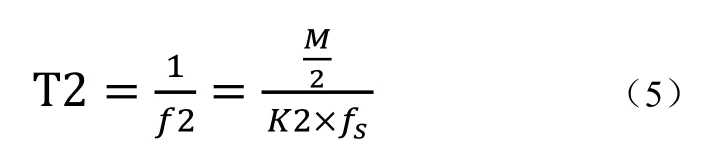

以上讨论的是正弦波、三角波、方波的频率改变。对于占空比可调的锯齿波,由于增加了一个输入量占空比(用字母D表示),需要单独考虑。本设计采用两个频率控制字K1,K2来实现占空比的可调,寻址ROM使用三角波定制的ROM,三角波ROM的前个点是上升点,寻址周期为公式(4):

可得整个ROM的寻址周期为公式(6):

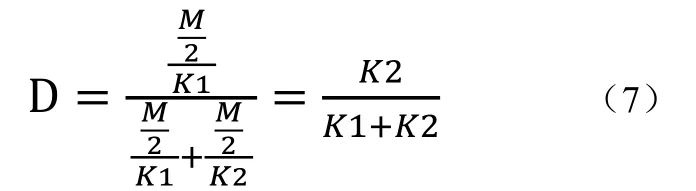

根据锯齿波占空比定义知为公式(7):

由公式4、5、6、7得公式(8)、(9):

此时,相位累加器N的高十位充当一个2选择器的触发开关,当N的高十位小于时,频率控制字K取K1;当N的高十位大于时,频率控制字K取K2。

2.2.4幅度控制模块

ROM存储的数据是输出幅度为最大幅度的波形数据,通过给ROM寻址输出的数据乘以一个系数来实现幅度的调节。记ROM寻址输出的波形幅度数据为q1,经幅度模块的输出的幅度数据为q2,波形的最大幅度为A,输出幅度为V,则有公式(10):

q2就是幅度调节后输送给D/A的幅度数据。

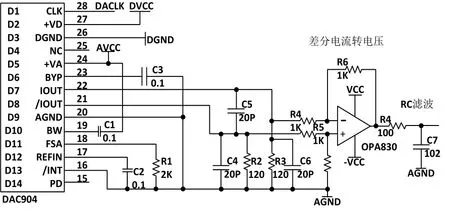

2.3模数转换设计

D/A芯片使用DAC904。DAC904是一款14位分辨率165MSPS采样率的高速并行DAC,可以将FPGA输出的波形数字信号转换为电流信号[8]。DAC904输出的差分电流信号经过后一级OPA830电路转化成初级波形输出信号,再经RC低通滤波器输出最终信号。其电路如图6所示:

图6 D/A转换电路图

3 软件设计和仿真

3.1软件设计

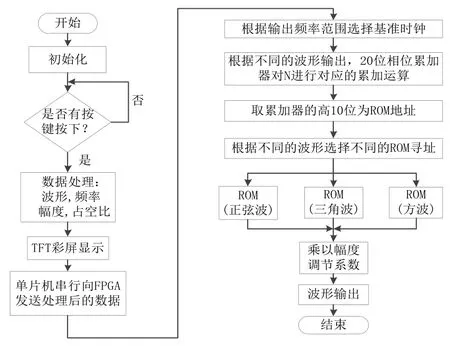

系统软件设计流程如图7所示:

图7 系统软件流程图

软件设计的主要思路是,通过单片机检测键盘输入,经初步数据处理,把输入信息显示到TFT彩屏上并串行发送指令到FPGA;FPGA根据输入的频率范围调整参考时钟,根据输入的波形选择相应的ROM存储器和相位累加器,再通过幅度控制实现调幅。

3.2系统仿真

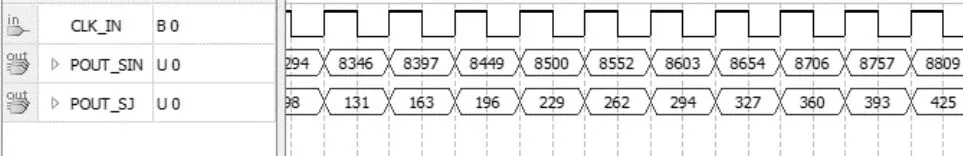

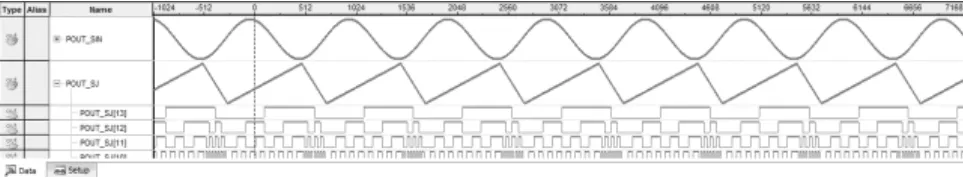

在Quartus II13.0和KEIL环境下,实现了软件部分的设计。对程序进行编译后,进行时序仿真以验证设计的正确性,正弦波和三角波的时序功能仿真图,输出端数据与ROM存储器数据完全一致,如图8所示:

图8 波形时序图

图9是使用Quartus II自带的嵌入式逻辑分析仪SignalTap II观察到的波形数据。逻辑分析仪SignalTap II可以捕捉目标器件FPGA内部任何节点处信息,信号发生器正弦波和锯齿波输出节点的信息,如图9所示:

图9 使用逻辑分析仪SignalTap II仿真波形图

4 信号发生器的实现

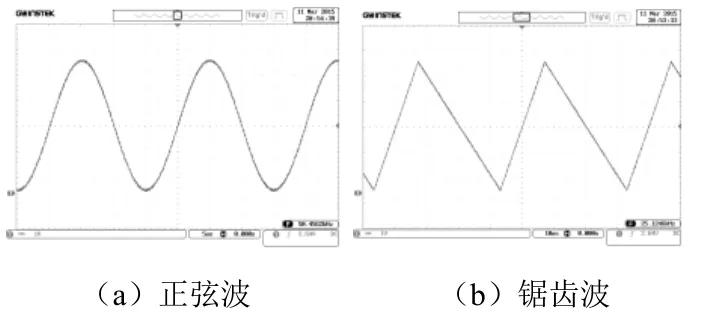

经过仿真和验证,将编译文件下载到核心板中,FAGA的幅度数据输入到D/A电路模块,在示波器上观察输出波形,波形输出结果与设计输出一致,符合设计要求。正弦波和锯齿波的波形图,如图10所示:

图10 示波器观察波形图

5 总结

基于FPGA的DDS波形发生器实现了正弦波、三角波、方波和锯齿波四种波形的频率可调、幅值可调和锯齿波占空比可调的信号输出。结果表明,本设计简单合理,波形转换速度快,输出波形质量好,而且本设计还能根据要求在线调试,通过改变ROM存储器的数据可以实现任意波形的输出,软件化程度高,具有良好的性价比。在本设计的基础上,相位累加器之后级联一个加法器,就可以实现相位的可调,被加数就是需要调整相位的矢量地址。

参考文献

[1] Tierney, J.; Rader, C.; Gold, B. A digital frequency synthesizer [J].Audio and Electroacoustics, IEEE Transactions on.1971, 19(1):48-57.

[2] 杨海钢,孙嘉斌,王慰. FPGA 器件设计技术发展综述[J].电子与信息学报,2010(3 ): 714-727.

[3] 李雪梅,张宏财,王学伟.基于DDS技术的信号源设计[J].电测与仪表,2012(01):55-56,66.

[4] 郝建卫.基于FPGA的脉冲宽度调制信号发生器[J]. 计算机工程,2013(2):260-264,269.

[5] 汉泽西,张海飞,王文渤,李国栋等.基于DDS 技术正弦波信号发生器的设计[J].电子测试,2009(08):65-69,77.

[6] 施羽暇,吕威,李一晨.基于DDS 技术的正弦信号发生器设计[J] .信息技术, 2007(1):17-20 .

[7] 向 伟,沈诗律,查 智,耿文豹等. 无相位截断误差DDS的设计与FPGA 实现[J].微型电脑应用,2013(10):1-4.

[8] 陈章余. 基于FPGA的DDS正弦信号发生器设计[J].电子技术与软件工程,2014(12):136.

收稿日期:(2015.03.26)

作者简介:张林行(1977-),男,吉林大学,仪器科学与电气工程学,院副教授,博士,研究方向:地震勘探方法与仪器研究,长春,130021尚小虎(1992-),男,吉林大学,仪器科学与电气工程学,大学本科,研究方向:地震勘探方法与仪器研究,长春,130021赵美聪(1993-),女,吉林大学,仪器科学与电气工程学,大学本科,研究方向:地震勘探方法与仪器研究,长春,130021 刘阳(1992-),女,吉林大学,仪器科学与电气工程学,大学本科,研究方向:地震勘探方法与仪器研究,长春,130021

基金项目:吉林大学2013年度创新训练国家级项目(2013A65238)

文章编号:1007-757X(2015)12-0016-03

中图分类号:TN791

文献标志码:A