基于中和电容的60 GHz CMOS功率放大器设计*

2015-02-28邸士伟李志强张海英中国科学院微电子研究所北京100029

邸士伟,王 硕,张 健,刘 昱,李志强,张海英(中国科学院微电子研究所,北京 100029)

近年来,众多国家相继开放了60 GHz附近5 GHz~7 GHz连续频谱资源,能够实现高达数Gbit/s的数据传输速率,是无线通信领域最具潜力的技术之一。

作为通信系统前端非常关键的模块,功率放大器的性能影响着整个系统。目前,应用于毫米波频段的功率放大器大多使用成本较高的化合物半导体集成[1]。随着CMOS工艺的不断发展和成熟,特征尺寸不断缩小,晶体管截止频率已经超过200 GHz,具有实现60 GHz放大器的能力,CMOS工艺相比于其他工艺具有集成度高,大规模量产价格低等优点,引发了国内外学术界和产业界的研究热潮。

由于工作在60 GHz频段的CMOS晶体管栅漏寄生电容(Cgd)影响增大,电路最大稳定增益降低,稳定性变差,应用受到了限制。针对该问题,本文设计了一款两级差分功率放大器,采用交叉耦合中和电容技术抵消Cgd的影响,提高了增益;同时,通过优化级间匹配网络和有源器件尺寸、偏置等参数,实现了较高的输出功率、增益、效率的功率放大器。

1 交叉耦合电容中和技术原理

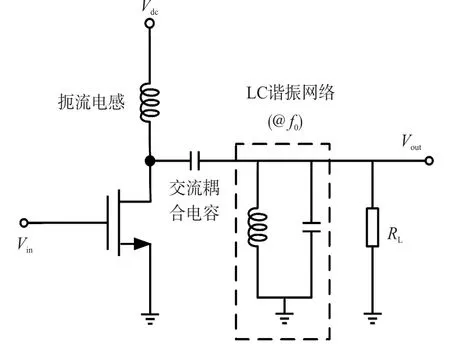

图1是传统功率放大器的电路图,工作频率较低时,晶体管栅漏寄生电容(Cgd)对电路影响较小。当工作频率和晶体管特征频率(fT)可比拟时,Cgd引入的反馈回路使得功率放大器增益降低,反向隔离变差,电路不稳定。

为了抵消Cgd的影响,采用交叉耦合电容中和技术,电路结构如图2(a)所示,图2(b)是其小信号等效电路。

图1 传统功率放大器

图2 交叉耦合电容中和技术电路

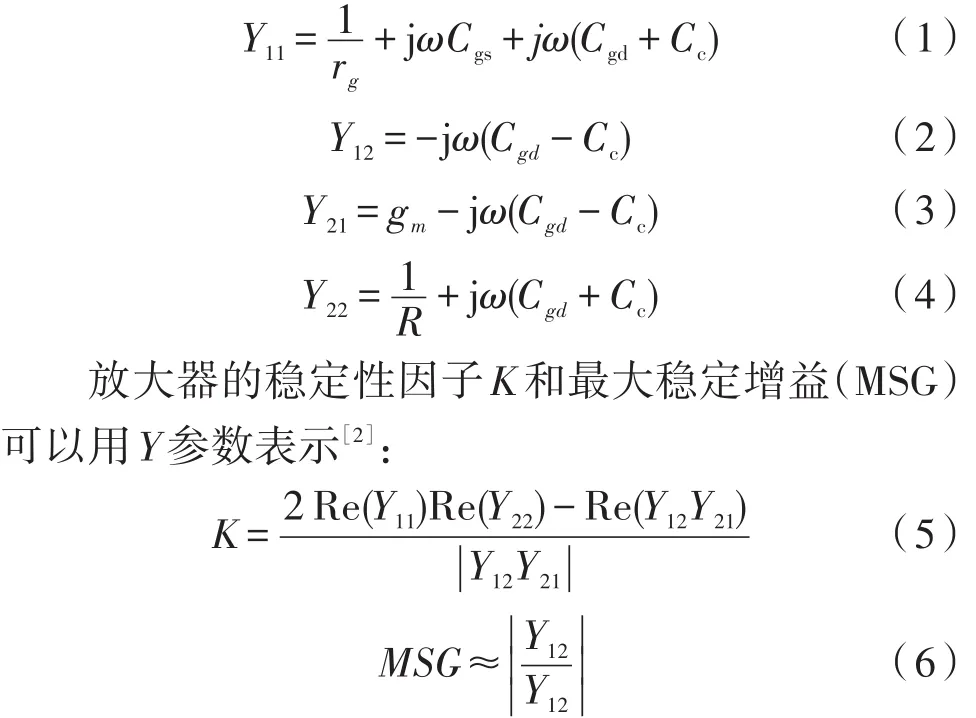

其中,Cc为交叉耦合中和电容,Cgs为晶体管栅源寄生电容,rg为栅极电阻,gm为小信号跨导。利用小信号电路得到Y参数:

从式(7)、式(8)可以看出,当交叉耦合中和电容Cc和晶体管栅漏电容Cgd大小相等时,稳定性最好,稳定增益最大。因此在电路设计时,交叉耦合电容Cc的选取应等于晶体管栅漏寄生电容Cgd。图3对比了有中和电容与无中和电容情况下,稳定性因子K和最大稳定增益(MSG)随频率的变化。从图中可以看出,中和电容的采用使得最大稳定增益和稳定性显著提高,在60 GHz时,最大稳定增益提高了5.3 dB。

图3 中和电容对最大稳定增益和稳定性的影响

2 电路设计

2.1 原理图设计

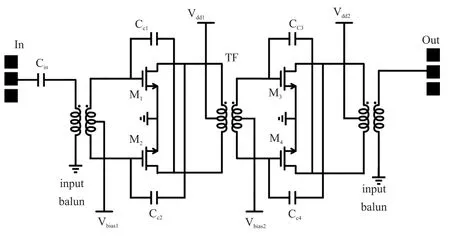

本文设计了一款2级差分功率放大器,第1级为驱动级,主要提供信号增益;第2级为放大级,在保证功率输出的基础上尽量提高增益和效率。两级均采用交叉耦合电容中和技术提高增益和隔离度;级间能量耦合和阻抗匹配采用变压器实现,片上巴伦完成输入端和输出端单端信号与差分信号的转换。电路结构如图4所示。

图4 功率放大器原理图

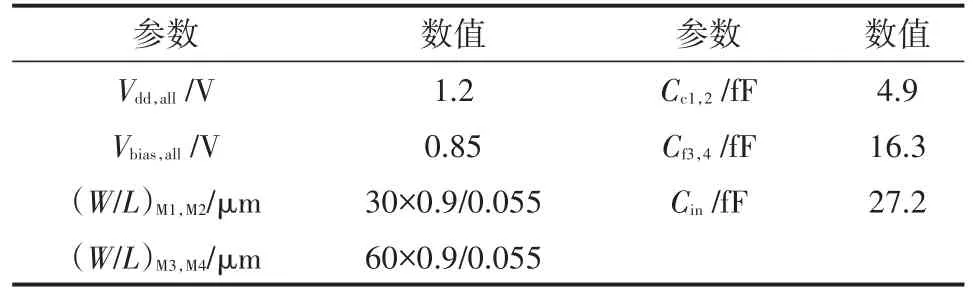

2.2 有源器件设计

为了提高功率放大器输出功率、增益和效率,电路设计过程中必须合理选择有源器件的偏置和尺寸。最大振荡频率(fmax)是表征工作在毫米波频段晶体管性能的主要指标,根据文献[3],当晶体管电流密度为0.2 mA/μm时,fmax最大。因此通过直流仿真得到晶体管偏置电压为0.85 V。晶体管宽度优化需要考综合两个方面,晶体管尺寸越大,输出功率越大;另一方面,寄生效应和衬底耦合损耗也越大,需要折中考虑。表1给出了原理图中各器件的参数值。

表1 功率放大器原理图器件参数信息

2.3 变压器设计

多级功率放大器需要匹配网络实现两级之间的阻抗变换,常用图5(a)所示的电感电容网络实现[4]。在毫米波频段,电感和电容品质因子Q通常较低,损耗较大,严重降低了功率放大器的增益和效率。为了减少无源器件电感电容的使用,本设计采用变压器结构实现级间匹配,如图5(b)所示。

图5 级间匹配网络

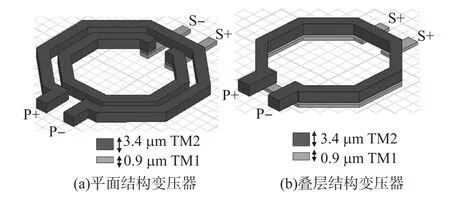

变压器的实现有两种结构形式:前后级线圈使用同一层金属的平面结构和使用两层相邻金属的叠层结构,分别为图6(a)和6(b)。

图6 片上集成变压器结构

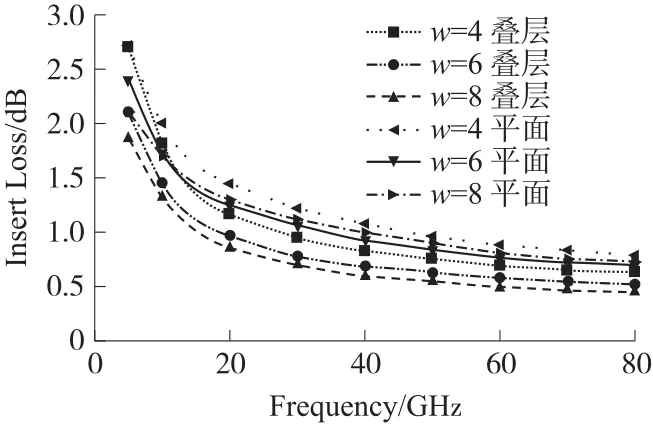

变压器的设计参数主要有线宽w和线圈半径r。线宽增大,直流电阻降低,损耗减小,但耦合变差。衡量变压器性能的最重要的参数是插入损耗,所谓插入损耗是变压器输出端功率和输入端功率之比的分贝数,在数值上等于前向传输系数(S21)的绝对值。利用电磁仿真软件Sonnet对两种结构不同线宽的变压器仿真,线宽w=4 μm,6 μm,8 μm,半径为25 μm的变压器插入损耗随频率的变化关系如图7所示。

图7 变压器插入损耗与线宽和结构的关系

由图可以得出,在毫米波频段,平面结构的变压器插入损耗比叠层结构变压器插入损耗大;在线宽w=4 μm,6 μm,8 μm的叠层结构中,w=8 μm插入损耗最小。因此在电路设计时,变压器采用线宽8 μm的顶层金属铜(TM1和TM2)实现。

线圈半径r的变化引起变压器输入端口和输出端口阻抗的变化。通过改变半径r,变压器可以将功率放大器驱动级输出阻抗变换到放大级输入阻抗的共轭,实现功率最大化传输。为了避免频繁地电磁仿真,节省设计时间。在设计过程中,将Sonnet电磁仿真得到的S参数文件导入ADS中进行建模。在进行原理图仿真时,使用参数化的变压器模型[5]代替实际的电磁仿真结果,通过调谐模型中的元件数值,经过迭代,实现变压器线圈半径的最优值。

3 版图设计及仿真

功率放大器芯片版图如图8所示。在设计过程中,综合考虑了以下因素:(1)电路是差分结构,版图严格保证对称性[6],避免失配的发生;(2)相邻信号线采用不同的金属层,减小信号线间的干扰;(3)充分考虑各层金属电流密度的限制,对电流较大的走线采用加宽金属线或多层金属堆叠的措施;(4)器件与变压器线圈保持一定距离,避免受到变压器电磁特性的影响。芯片上除放置器件的区域外均用底层M1和M2金属铺地。芯片面积为380 μm×570 μm。

图8 PA芯片版图

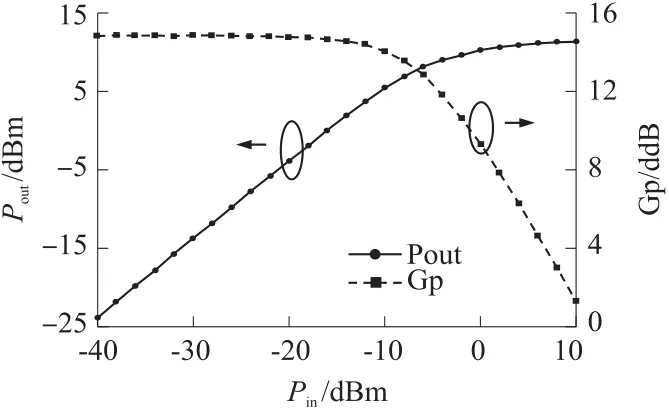

采用Cadence Spectre对电路进行了后仿真。仿真结果如图9和图10所示。饱和输出功率(Psat)11.2 dBm,在60 GHz处功率增益达到最大值16.2 dB,功率附加效率(PAE)最大值为17.0%。功耗55.2 mW。表2给出了本设计与其他文献的性能对比,可以看出,本文设计的功率放大器提高了输出功率,增益和效率。

图9 PA输出功率(Pout)和功率增益(Gp)

图10 PA功率附加效率(PAE)

表2 本文功率放大器性能与文献对比

4 结论

本文基于SMIC 55 nm RF CMOS工艺设计了一种应用于60 GHz频段的差分功率放大器。由于CMOS晶体管栅漏寄生电容(Cgd)影响了功率放大器性能,引入交叉耦合电容中和Cgd。为了减少无源器件对增益和效率的影响,采用变压器结构同时实现级间阻抗匹配和能量耦合。优化版图设计减小寄生效应,失配和干扰。版图后仿真结果表明:60 GHz功率放大器输出功率为11.3 dBm,功率增益为16.2 dBm,功率附加效率(PAE)为17.0%,功耗为55.2 mW。与其他文献对比,本设计实现了输出功率大,增益和效率高的设计目标。

[1]Hsien C,Bo K.High Performance V-Band GsAs Power Amplifier and Low Noise Amplifier Using Low-loss Transmission Line Tech⁃nology[C]//High Speed Intelligent Communication Forum.Nan⁃jing:IEEE,2012:1-4.

[2]Hiroki A,Kota M,Keigo B,Kenichi O,Kenichi O,Akira M.A 60 GHz CMOS Power Amplifier Using Capacitive Cross-coupling Neutralization with 16%PAE[C]//Microwave Integrated Circuits Conference.Manchester:IEEE,2011:1115-1118.

[3]Ali M,Niknejad H,Hashemi.Mm-Wave Silicon Technology 60 GHz and Beyond[M].Cambridge:Springer,2008.81-83.

[4]Ki J K,Lim T H,Ahn K H.The Transformer Coupled mm-Wave CMOS Power Amplifier[C]//Circuits and Systems.Kuala Lumpur:IEEE,2010:276-279.

[5]Bernardo L,Eric K,Jean B,Didier B.An Analytical Broadband Model for Millimeter-Wave Transformers in Silicon Technologies[J].Electron Devices,2012,59(3):582-589.

[6]宗国翼,朱恩,李智群.可用于无线局域网802.11a标准的5 GHz CMOS功率放大器设计[J].电子器件,2005,28(1):49-52.

[7]Debopriyo C,Patrick R,Ali M N.Design Considerations for 60 GHz Transformer-Coupled CMOS Power Amplifiers[J].Jour⁃nal of Solid-State Circuits,2009,44(10):554-564.

[8]Sofiane A,Eric K,Robert P,Didier B.A 59 GHz to 67 GHz 65 nm CMOS High Efficiency Power Amplifier[C]//New Circuit and Systems.Bordeaux:IEEE,2011:225-228.

邸士伟(1989-),男,汉族,甘肃武威人,中国科学院微电子研究所硕士研究生,研究方向为毫米波集成电路设计,dishiwei@ime.ac.cn;

刘 昱(1975-),男,哲学博士,研究员。主要研究方向为高性能模拟/射频CMOS集成电路,硅基毫米波集成电路,超低功耗短距离无线通讯系统等,liuyu5@ime.ac.cn。