基于FPGA的断电续传存储系统的设计与实现*

2015-02-26李加超孟令军周之丽韩朝辉

李加超,孟令军,周之丽,韩朝辉

(中北大学,电子测试技术国家重点实验室,太原030051)

基于FPGA的断电续传存储系统的设计与实现*

李加超,孟令军*,周之丽,韩朝辉

(中北大学,电子测试技术国家重点实验室,太原030051)

摘要:针对遥测领域中数据记录器面临的高速输入数据连续存储和断电续传的技术难题,详细介绍了NAND型Flash交替双平面页编程方式,分析了3种常用的NAND型Flash剩余容量检测方法的特点,提出了一种基于二分法和带系统识别码交替双平面页编程技术的NAND型Flash剩余容量快速检测的方法,检测结果高效准确,检测误差可以达到10-4,并在此基础上设计了具有断电续传功能的数据存储系统,设计方法简单可靠,具有较好的应用前景。

关键词:NAND Flash;交替双平面;页编程;二分法;存储系统

项目来源:基金项目:国家自然科学基金资助项目(51275491)

目前,NAND型Flash是一种在EEPROM基础上发展而来的新兴的存储器件,具有非易失性、掉电后数据不丢失、存储容量大等特点,比较适合于数据存储设备,广泛应用于工业自动化、医疗卫生、航空航天等各个行业[1]。

随着遥测领域信息技术的高速发展,信息的需求量急剧增加,也对数据存储系统提出了更高的要求。在一些特殊的应用场合中,有时需要在系统断电又重新上电的情况下继续实时地存储系统接收的关键性的数据,并最终能够实现数据的回放,用于后续的数据分析和处理。因此,在现代数据存储系统研究中,如何检测存储系统的剩余容量以实现数据的高速存储与断电续存,已经成为研究的热点问题[2-3]。

1 系统总体结构及组成

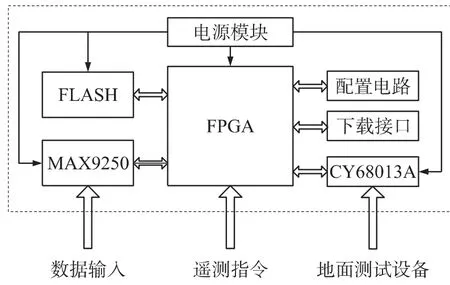

该数据存储系统硬件部分主要包括FPGA主控模块、MAX9250数据接收模块、FLASH存储器模块、CY68013A接口模块、电源模块、配置电路模块、下载接口模块等,图1为系统结构框图。FPGA主控模块负责接收遥测设备下发的操作指令,将MAX9250接收到的数据存储在FLASH存储器中,或者将FLASH存储器中的数据经过CY68013接口模块上传给地面测试设备,用于数据分析处理。

图1 系统结构框图

数据接收模块主芯片采用27 bit,速度最高可达42 MHz的MAX9250 LVDS解串芯片,该芯片可以解串发送端串化芯片对应引脚上所串化出来的电平特性,其具体数据传输位数可以根据设计需求以及发送端进行配置。

CY7C68013A芯片是赛普拉斯半导体公司USB2.0控制器中的产品,支持速率为12 Mbit/s的全速传输和速率为480 Mbit/s的高速传输,用于数据存储系统与地面测试设备之间的通信。

存储器模块选用SAMSUNG公司的NAND型Flash K9WAG08U1M芯片,其单片容量为2 Gbyte,其内部是由两片容量为1 Gbyte的K9K8G08U0M叠装而成,并通过两个CE端口进行选通控制[4-5]。单片K9K8G08U0M由8192个存储块(Block)组成,每个存储块由64个页(Page)组成,而每页是由2k+64 byte组成,其中64个字节为空余区,通常可用于错误检测和记录特定信息[6]。

2 系统软件设计

2.1交替双平面页编程

K9K8G08U0M芯片内部阵列结构如图2所示,K9WAG08U1M可以看成是两片K9K8G08U0M组成,分别记为片1与片2,通过芯片的CE1、CE2引脚进行选通控制,当CE1为低时,可以认为是对片1进行读、写或者擦除等操作,当CE2为低时,可以认为是对片2进行相关操作[7-9]。

图2 K9K8G08U0M型芯片内部阵列结构图

交替双平面页编程是利用芯片内部不同平面可以单独操作的特性,对平面进行流水线操作能够大幅度提高单片Flash的写入速度[10-12]。如令片1中plane0和plane1为A组;片1中plane2和plane3为B组;片2中plane0和plane1为C组;片2中plane2 和plane3为D组,片内写操作流水线工作原理如图3所示,在任何一个时间片上,总有若干个操作同时进行,即实现了时间片上的复用,从而实现高速数据的连续存储,存储速度达到35 Mbyte/s。

图3 流水线工作原理

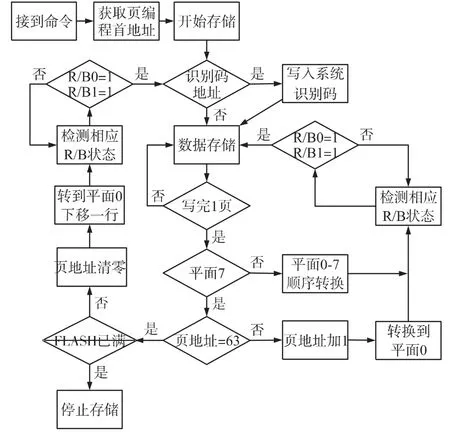

带系统识别码的交替双平面页编程方式为规定在片1平面0中所有块的第1页的第1个地址作为系统识别码地址,在每次交替双平面页编程的过程中寻址到系统识别码的地址时写入系统识别码(如0xDB),用来指示与平面0平行的块中是否已经写入了数据,因此,已经写入数据的存储单元对应的系统识别码的地址存储的数据为0xDB,反之为0xFF,相应的交替双平面页编程流程图如图4所示。

图4 带系统识别码的页编程方式

2.2断电续传功能的实现

要实现数据存储系统的断电续传的功能,系统必须在意外断电又重新上电时自动准确识别出数据存储系统在断电前一刻记录的位置,并将有效的编程地址反馈给主控制器,作为连续记录时的首地址。由于数据存储系统的存储单元为NAND型Flash,因此Flash剩余容量的检测显得至关重要。

2.2.1逐字节检测法

实现Flash剩余容量检测有多种方法,最简单的方法是对Flash内存储的数据进行逐个字节检测。由于Flash未写入数据时读回来的数据是0xFF,因此只要检测Flash内从哪个地址开始到最后一个地址的数据全是0xFF,就可以计算出剩余容量。这种方法虽然可行,但检测过程中需要大量读取Flash内的数据,甚至是所有数据,检测效率低。此外,如果由于某种特殊的需要,写入Flash内的数据就是0xFF,那么这种方法的检测结果是不准确的。

2.2.2信息记录法

信息记录法是规定Flash的第1块第1页中特定的存储单元用来记录上次页编程的最后地址,系统上电后通过读取该存储单元的数据计算Flash的剩余容量,并更新下一次的页编程地址,在数据存储结束后,再将最后的页编程地址更新到这个特定的存储单元中。相比于逐个字节检测的方法,这种方法不用大量检测Flash内的数据,只需在每次数据记录结束后更新第1块第1页中特定存储单元即可,简单易行。但这种方法也有一个弊端,如果Flash在断电前没有退出数据存储状态,也就没有机会把最后的页编程地址更新到特定的存储单元中,在下一次系统上电后获取的页编程地址必然是错误的,此后的数据存储过程中必然会出现大范围误码或数据丢失。

2.2.3逐行检测法

逐行检测法是在带系统识别码的交替双平面页编程方法的基础上进行的,设计中所使用的NAND 型Flash K9WAG08U1M共2048个由存储块组成的行,共2 048个系统识别码,读取每个系统识别码的时间约25 μs,如果Flash为空,检测过程需要25 μs,如果Flash已写满,检测过程需要51.2 ms,检测过程需要的时间由Flash内存储数据的量决定。这种方法虽然可行,但略显笨拙,且检测过程所需时间是一个不确定的值,如果存储器件由多个Flash串联构成,检测时间成倍增长。

2.2.4基于二分法的Flash剩余容量检测

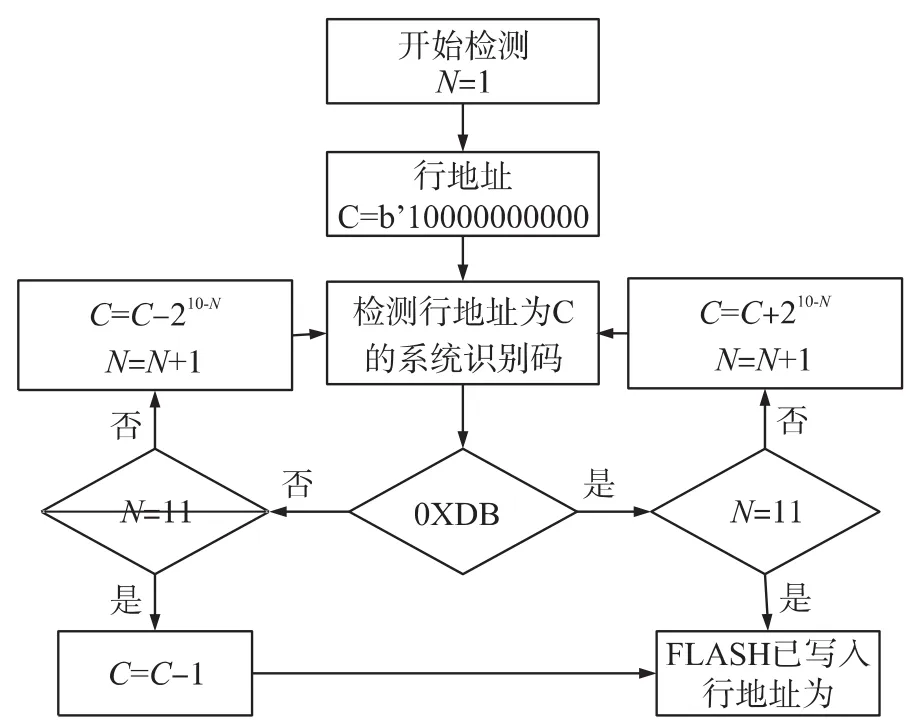

基于二分法的Flash剩余容量检测方法是在带系统识别码的交替双平面页编程基础上的进行的,对于NAND型Flash K9WAG08U1M芯片,二分法不是从第1行开始检测系统识别码的,而是先从地址为b'10000000000的行(十进制为1024,总行数的一半)开始检测系统识别码。如果检测结果为0xDB,表明已写入数据的行地址超过了b'10000000000,下一次检测系统识别码的位置将选择在从地址为b'10000000000的行到地址为b'11111111111的行的一半,即地址为b'11000000000的行;如果检测的结果为0xFF,则表明数据未写入到地址为b' 10000000000的行,下一次检测系统识别码的位置将选择在从地址为b'00000000000的行到地址为b'10000000000的行的一半,即地址为b'01000000000的行。依次类推,每一次检测都将检测范围缩小一半,不管Flash已写入多少数据,只需检测11次 (275 μs)就能确定其剩余容量,并将有效的编程地址反馈给主控制器,作为连续记录时的首地址,检测流程如图5所示。

图5 二分法检测流程

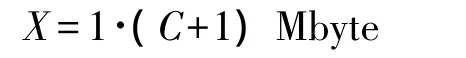

NAND型Flash K9WAG08U1M总容量为2 048 Mbyte,每行包含8块,共1 024 kbyte,则已写入的数据量X为:

式中: C为按图5所示检测流程检测后得到的行地址,其剩余存储容量为:

3 测试结果

图6为用上位机对NAND型Flash K9WAG08U1M进行剩余容量检测的结果。NAND型Flash K9WAG08U1M总容量为2 Gbyte,每块的存储容量是128 kbyte,每一行包含8个块(128×8=1 024 kbyte),因此基于二分法的Flash剩余容量检测方法的最小检测单位为1 Mbyte,检测误差度可以达到10-4。

图6 检测结果

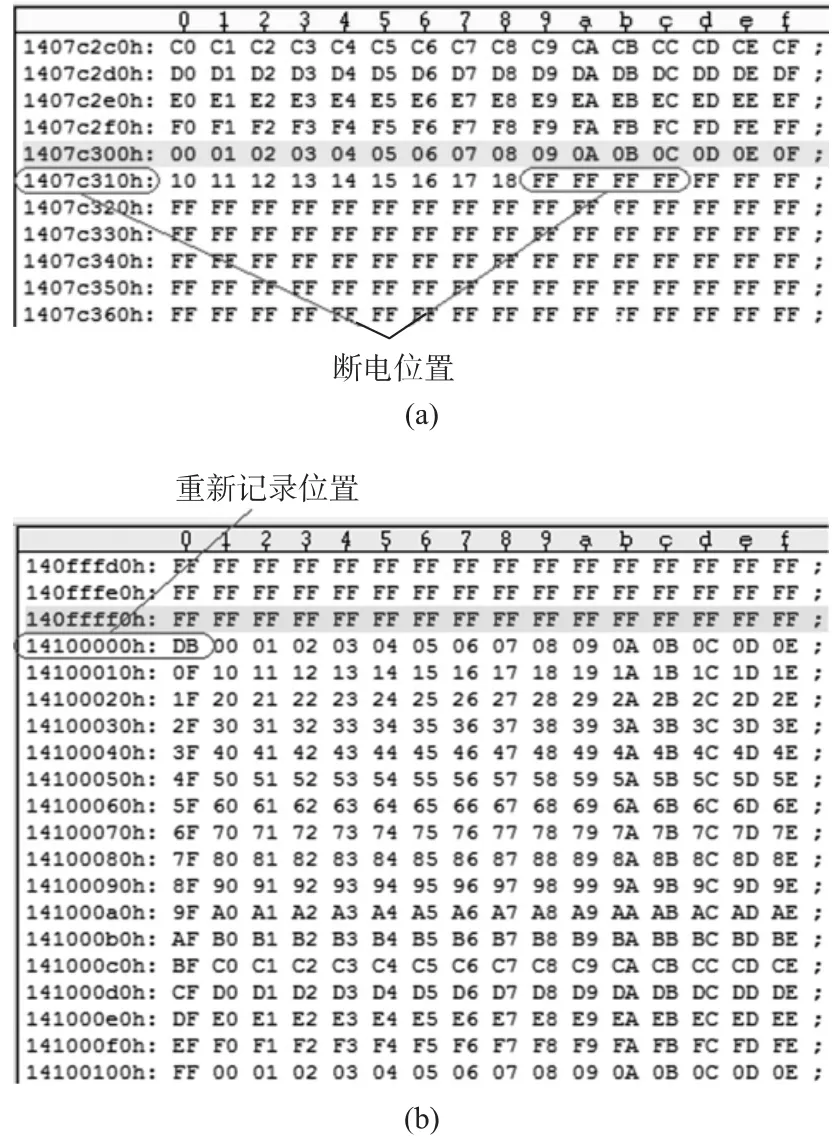

为了验证该数据存储系统的可行性与稳定性,在读取存储器中的数据时,系统识别码(0XDB)也一起读出,在正式工程中,系统识别码是会被自动忽略的。图7为该数据存储系统在存储过程中意外断电,然后重新上电后继续记录时存储的数据,其中图7(a)为意外断电时记录的数据,图7(b)为重新上电后继续记录的数据,从实验结果可以看出该数据存储系统达到了预期的目标。

图7 存储系统存储的数据

4 结论

本文在基于二分法和带系统识别码交替双平面页编程技术的NAND型Flash剩余容量快速检测的方法的基础上设计的具有断电续传功能的数据存储系统在数据存储速度和可靠性方面有了很大提高,在系统意外断电、重新上电的情况下能继续工作,完成数据的连续存储,该数据存储系统的实现将在要求高速、高可靠性的存储领域有广泛的应用前景。

参考文献:

[1]Qin Xi,Feng Changqing,Zhang Deliang.A Low Dead Time Vernier Delay Line TDC Implemented in an Actel Flash-Based FPGA[J].Nuclear Science and Techniques,2013,24(4) : 61-67.

[2]何剑锋,李大晖,李祥.基于ARM嵌入式uClinux下NANDFlash的应用设计[J].自动化与仪表,2009,24(3) : 53-56.

[3]王顺,戴瑜兴,段小康.基于FPGA的NAND Flash控制接口电路设计[J].计算机工程与科学,2010,32(7) : 80-82.

[4]沈浩,付宇卓.NAND Flash存储控制器的软硬件划分设计[J].计算机工程,2004,30(24) : 168-171.

[5]吴鹏.高速实时Flash阵列数据采集系统研究与实现[D].南京:南京理工大学,2007.

[6]唐磊,周旋,吴瑶,等.基于FPGA的K9F4G08 Flash控制器设计[J].电子技术应用,2010,36(5) : 57-59.

[7]张胜勇,高世杰,吴志勇,等.基于FPGA的NAND Flash坏块处理方法[J].计算机工程,2010,36(6) : 239-243.

[8]晏敏,龙小奇,章兢,等.开放式大容量NAND Flash数据存储系统设计与实现[J].微电子学与计算机,2009,26(11) :13-16.

[9]舒文丽,吴云峰,孙长胜,等.基于NAND Flash的海量存储器的设计[J].电子器件,2012,35(1) : 107-110.

[10]舒文丽,吴云峰,赵启义,等.NAND Flash存储的坏块管理方法[J].电子器件,2011,34(5),580-583.

[11]刘东海,任勇峰,储成君.基于FPGA控制的NAND Flash存储设计[J].科学技术与工程,2013,13(34) : 10349-10353.

[12]刘泳锐,刘文怡,张彦军.声无线传感网络节点数据高速存储实现[J].电子器件,2013,36(5) : 696-699.

李加超(1988-),男,汉族,山东临沂人,硕士研究生,主要研究方向为微纳仪器及测试技术、集成测试系统及仪器;

孟令军(1969-),男,汉族,博士,副教授,硕士生导师,主要研究方向为动态测试技术与智能仪器、微系统集成、无线传感器。

The Design of Solid-State Memory Having the Function of Power Down-Surviving*

JIAN Shaokun1,2,ZHANG Huixin1,2*

(1.National Kay Laboratory For Electronic Measurement Technology(North University of China),Taiyuan 030051,China; 2.Kay Laboratory of Instrumentation Science and Dynamic Measurement of Ministry of Education,Taiyuan 030051,China)

Abstract:For aircraft during flight due to accidental instantaneous power-down and led to the stored data being overwritten,so a design of solid-state memory has been forward for holding the function of power down-surviving.Taking FPGA as the main control chip,RS-422 and LVDS as the hardware communication means,NAND FLASH as the memory core.The function of power down-surviving is realized by programming based on the storage mode of interleave two-plane.The large number of scientific analysis of measured data show that the design of solid-state memory having the function of power down-surviving has been realized,solving the problem because of instantaneous power down led to record data being overwritten,meeting the needs of a particular model of aircraft.

Key words:solid-state memory; power down-surviving; FPGA; LVDS; FLASH

中图分类号:TN402

文献标识码:A

文章编号:1005-9490(2015) 03-0588-04

收稿日期:2014-07-11修改日期: 2014-08-10

doi:EEACC: 6230B10.3969/j.issn.1005-9490.2015.03.023