基于FPGA的多通道模拟信号源设计

2015-02-26贾兴中张凯华任勇峰

贾兴中,张凯华,任勇峰

(中北大学电子测试技术国家重点实验室,太原030051)

基于FPGA的多通道模拟信号源设计

贾兴中,张凯华,任勇峰*

(中北大学电子测试技术国家重点实验室,太原030051)

摘要:针对航天测试领域对模拟信号源的设计要求,提出一种新的信号源实现方法。该方法借助计算机软件能实时编程生成波形数据,通过对波形重构电路,调理电路和多通道电路的合理设计,由FPGA控制逻辑实现波形重构和多通道输出。由于方波信号沿变时具有的特殊性,设计专门的方波产生电路,通过实验验证,对原先设计电路的阻尼特性加以改进,实现了方波信号高精度的可靠输出,满足技术指标要求。目前,该信号源已广泛应用于多项航天测试项目。

关键词:模拟信号源;实时编程;多通道; FPGA;方波信号

信号源作为航天器配套测试的重要环节,需要具备高精度、高可靠性、易操作等特点。传统信号源由于输出精度不高,波形较为单一,参数不可调控等缺点,已经无法满足航天测试需求。本文设计的信号源以FPGA为主控芯片,结合计算机软件的强大功能,实现信号源的多通道可靠传输。克服了传统信号源的不足,能够为被测设备提供满足要求的参数可调信号。

1 技术要求及系统方案

该模拟信号源的设计及应用属于某型号地面测试台的研究任务,主要技术指标如下:

(1)输出信号幅度:高低电平分别可在-1 V~+ 7 V之间调节;

(2)输出信号精度:优于±0.062 5%;

(3)相位调节能力: 1 ms~10 s可调,调节步长1 ms;

(4)矩形波边沿时间:≤1 μs。

测试台各功能板卡之间依靠背板总线建立起通讯和供电机制,测试台与上位机之间的连接则通过主控卡完成[1]。模拟信号源的设计采用模块化的思想,可分为电源模块、接口模块和信号源模块3个部分。电源模块负责转化背板提供的电源;接口模块建立背板与信号源之间的通信[2];信号源模块包含了主控制器FPGA,信号存储,信号调理及信号输出,各部分在FPGA的协调控制下输出32路信号波形。总体方案设计如图1所示。

图1 总体方案设计

2 硬件电路设计

多通道模拟信号源的关键电路包括接口电路、波形重构电路、多通道输出电路、方波生成电路等。接口电路在背板与信号源数据传送的过程中起桥梁作用,由于背板采用LVDS总线协议,因此选用芯片DS92LV18实现数据流的串并转换,主控制器FPGA识别背板总线指令并执行操作[3]。

2.1波形重构电路设计

波形重构电路是一种新的信号源实现方法,该方法借助于直接数字合成技术(DDS)的思想原理[4],通过USB总线将软件技术融入到信号源的实现中,利用强大的语言编程功能将硬件设计软化,由软件实时产生波形数据。信号源由基于LVDS的接口从背板高速串行总线上接收计算机指令及波形数据,经FPGA判断并存储在波形存储芯片HM628512中,完成波形数据的下载[5]。当启动信号源后,加载波形数据产生的阶梯电压经低通滤波器平滑后得到需要输出的波形。

指标要求信号源的输出幅值精度达到0.062 5%,理论上选用具有14位分辨率的DAC即可实现,但由于电路本身具有的误差,实际的DAC电路无法达到理论精度。为此选用具有更高分辨率的AD768AR芯片。该芯片具有16位分辨率,30 Msample/s的输出更新速率,以及稳定的2.5 V的输出参考电压。其外围电路提供一种双极性的设计方案,用于产生对称幅值的输出电压。如图2所示。

AD811是一款具有较高动态性能的运放。DAC引脚REFOUT为输出参考电压,稳定输出2.5 V。计算流经电阻R108的电流稳定值为2.5 mA,称为补偿电流;引脚REFIN参考输入电流为5 mA,则DAC的满量程电流为4×5 mA = 20 mA。当AD768的输入为(1000 0000 0000 0000)时,IOUTA为满量程电流的一半10 mA,R105和R107产生分流,流经R105的电流为2.5 mA。此时流经R109的电流为0,输出电压也为0。当AD768的输入为全0或全1时,IOUTA分别为0 mA 和20 mA,流经R109的电流分别为2.5 mA和-2.5 mA,输出电压分别为2.5 V和-2.5 V。改变反馈电阻R109的大小即可改变输出电压的峰峰值。

图2 波形重构电路设计

DAC的输出级经两级AD824电压调理电路,可输出电压-1.25 V~+7.25 V,保留0.25 V的电压余量,满足指标-1 V~7 V的电压输出范围。

2.2多通道输出电路设计

波形数据经过DAC转换之后要输出64路模拟信号,如果每一路都采用一个DAC进行模数转换再调理输出,无法满足功能卡物理尺寸的要求,增加了系统开发成本,而且违背设计简洁的原则。因此设计采用电子开关控制及运放电路保持跟随把各路模拟信号切换到对应通道位置,实现多通道输出[6],设计电路如图3所示。

图3 多通道输出电路设计

ADG506是一款16位的模拟信号多路选通芯片,引脚EN使能,在输入端A0~A3的控制下实现单路选通,4片ADG506芯片可选择64路信号,输入VOUT为前端电压调理电路输出,输出端采用AD824对其进行采样保持及跟随输出。

2.3方波电路设计

按照上述原理实现多通道模拟信号输出时,采用的是将多路信号分时输出,每一路都有采样保持电路对输出信号进行采样保持,这样会使得输出信号的频率较低。当产生方波输出时,其边沿时间为采样保持电路的采样时间,通常为几微秒或几十微秒,远超过设计指标小于1 μs的要求。因此,提出采用单刀双掷模拟开关切换电平的输出方案,该方案输出的方波信号上升沿和下降沿时间主要取决于模拟开关的导通和关断时间。

设计原理如图4所示,U1、U2为不同电平幅度的直流信号,设U1<U2,开关从U1导通变为U2导通时,Uout产生方波上升沿;开关从U2导通变为U1导通时,Uout产生方波下降沿。

单刀双掷模拟开关选用ADG333A,典型导通和断开时间分别为90 ns和80 ns,导通电阻45 Ω。为提高信号源的驱动能力,单刀双掷开关后面使用高速运算放大器作为输出跟随。实验中发现,生成的方波伴随有“过冲”和“振荡”现象,而这样的方波无法作为标准信号源提供给外部被测设备,需要针对此提出可靠有效地解决办法。

图4 方波生成电路原理图

为了对输出波形的上升沿和下降沿进行瞬态分析,建立如图5所示的等效电路模型[7],输入电平U1=VCC,U2=GND。在测试时,示波器探头的等效电容视为负载电容CL,连接线等效成电感与电阻串联。

应用基尔霍夫定律建立方程:

图5 等效电路模型

根据阻尼系数的不同取值判断输出响应曲线: 当0<ξ<1时,输出响应为衰减振荡,称为欠阻尼系统,其暂态过程是在输出高电平上下振荡,出现“过冲”现象。振荡随时间衰减,与实验中出现的情况相同。当ξ>1时,输出响应为单调上升曲线,不伴随振荡现象,称为过阻尼系统。当ξ= 1时,是上述两种情况的临界状态,称为临界阻尼系统,输出没有“过冲”现象。在实验条件允许的情况下应当选择合理的阻容,使系统工作在临界阻尼状态。

由以上分析对原实验电路进行改进,调整其阻尼特性,设计电路如图6所示,其中电阻R取值2 kΩ,C取值10 pF。

图6 调整后的方波生成电路

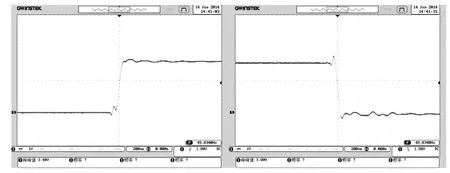

结果表明通过增加电阻、电容改变电路阻尼特性的方法,有效解决了电平切换输出方波时出现的过冲和振荡现象。只要电阻、电容取值恰当,使阻尼系数ξ接近于1,即可输出较为理想的方波。而且,输出波形的上升沿时间可以控制在200 ns之内,小于1 μs,满足技术指标要求。证明通过单刀双掷模拟开关切换电平产生方波的方案设计可行。

3 FPGA控制逻辑设计

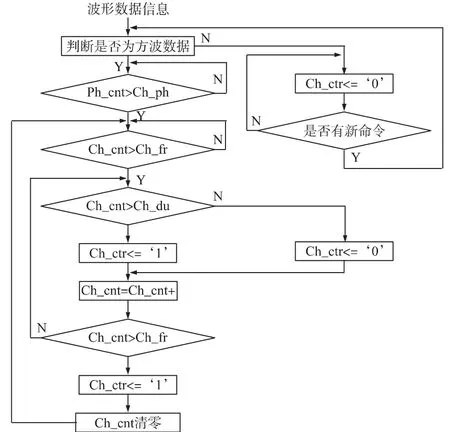

由于信号源生成方波信号的特殊性,需要在逻辑设计时,按照方波信号与非方波信号加以区分,主要体现在单刀双掷模拟开关的控制逻辑上[8]。如果输出非方波信号,单刀双掷模拟开关控制引脚置‘0’,B通道打开,A通道关闭,波形信号由B通道输出。如果输出信号为方波信号,单刀双掷模拟开关控制引脚周期性置‘0’,输入A通道的信号和输入B通道的信号(两路信号均为直流量)周期性的交替输出,生成方波。

控制逻辑分别采用计数周期为1 ms的15位计数器控制方波的相位(Ch_ph)、频率(Ch_fr)和占空比(Ch_du),实现波形相位1 ms~10 s可调、频率0.1 Hz~500 Hz可调和占空比可调。信号源启动后相位计数器Ph_cnt开始计数,并与Ch_ph比较,达到其相位值时启动频率占空比计数器(Ch_cnt),开关控制引脚逻辑置‘1’;当Ch_cnt等于波形占空比数值时,控制引脚逻辑置‘0’;当Ch_cnt计满一个波形周期时,计数器清零重新开始计数,控制引脚逻辑置‘1’。从而在输出端产生连续的方波信号。控制逻辑流程图如图7所示。

图7 控制逻辑流程图

4 实验结果

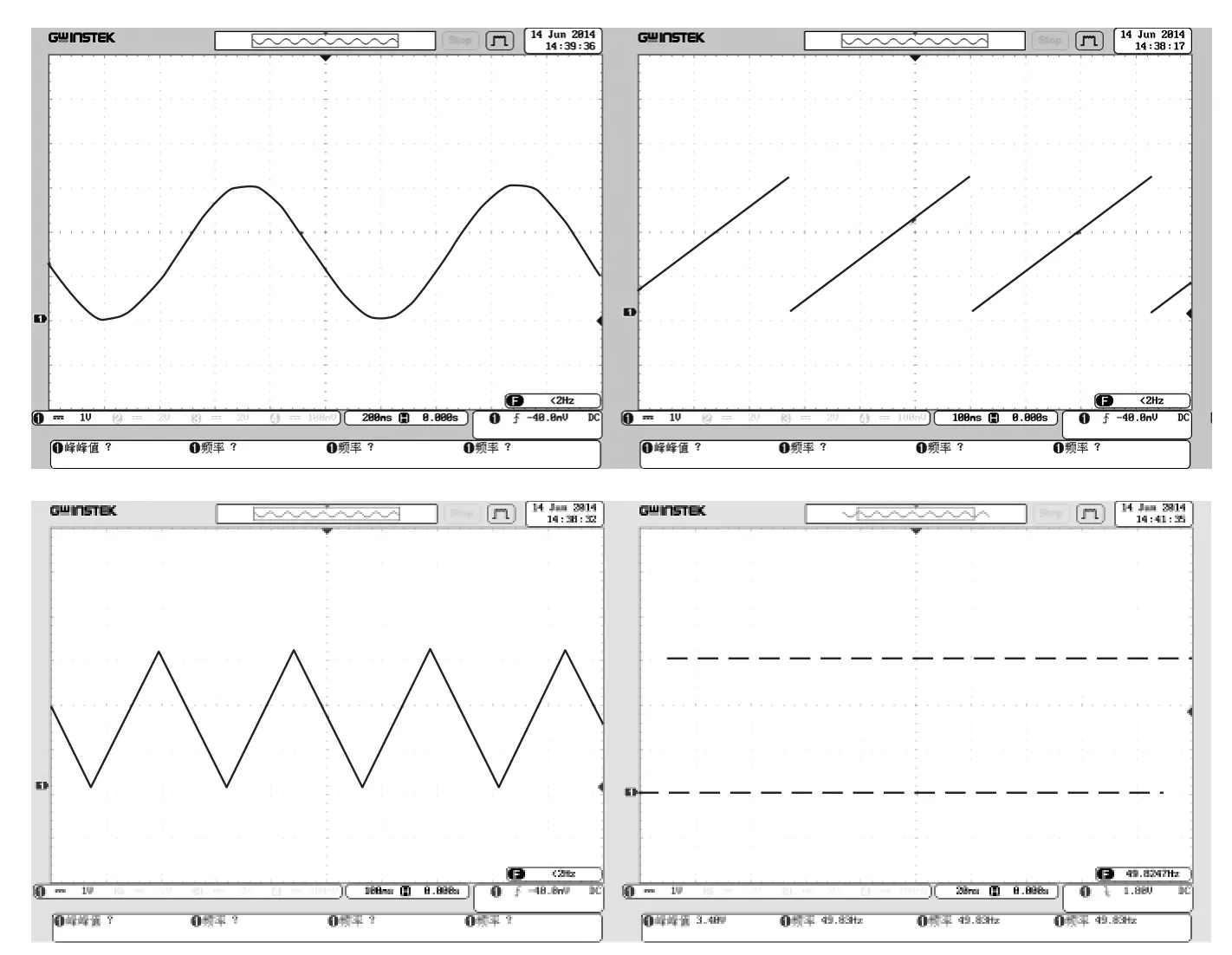

利用计算机软件实时设置各通道输出波形及参数,并生成相应的数据文件,加载至信号源。启动信号源发送命令,在输出通道测量波形输出如图8所示,分别为正弦波、锯齿波、三角波和方波。其中,方波频率为50 Hz,频率参数可调。针对方波信号上升沿和下降沿的时间要求,对其进行测量如图9所示:上升沿和下降沿时间均为200 ns左右,小于1 μs,完全满足技术指标要求,输出信号稳定、可靠。

图8 信号源输出波形测量

图9 方波信号上升沿和下降沿测量

5 总结

本文设计利用计算机软件编程技术产生信号源波形数据,结合以FPGA为主控制器的硬件电路,利用AD768芯片对模拟波形进行重构,通过多路选用开关实现“一对多”通道的切换,合理有序输出32通道模拟信号。特别对要求较为严格的方波波形,提出针对性的设计电路,解决电路缺陷,完成设计指标要求。信号源输出信号具有稳定可靠,多通道,精度高,波形参数可调的优越性。在航天测试领域有广泛的应用前景。

参考文献:

[1]李晓明,盛琥,邓鹏飞.任意信号发生器的USB2.0接口设计[J].电子器件,2009,32(3) : 643-648.

[2]单彦虎.基于FPGA的通用测试台LVDS环网总线设计与实现[D].太原:中北大学,2010.

[3]甄国勇.雷达视频回波模拟设备关键技术研究[D].太原:中北大学,2009.

[4]黄志军,潘攀,赖振华.基于FPGA的多用信号源的设计与实现[J].天津大学学报,2006,39: 383-387.

[5]安震,张会新,卢一男.基于PCI总线与FPGA多通道模拟信号源的系统设计[J].计算机测量与控制,2012,20(9) : 2558-2560.

[6]王红亮,黄洋文.基于FPGA的可程控多路信号源设计[J].火力与指挥控制,2010,35(6) : 97-99.

[7]韩海涛.高速数字PCB板互连噪声建模与仿真研究[D].成都:电子科技大学,2006.

[8]胡小燕.基于PCI+FPGA的任意波形发生器的研究与设计[J].电子质量,2010(4) : 24-26.

贾兴中(1984-),男,汉族,山西太原人,硬件工程师,研究方向为电子测试仪器与系统;

张凯华(1991-),男,汉族,山西临汾人,中北大学测试计量技术及仪器专业在读硕士研究生,研究方向为电子测试仪器与系统,kai.hua2008@ 163.com;

任勇峰(1968-),男,汉族,山西省中阳县人,教授、博士生导师,主要从事弹载固态记录器和自动测控台等方向的研究工作。

Data Acquisition System of Various Communication

Methods Based on LabVIEW*

LIU Jingfeng1,YUE Fengying1*,FENG Xiaobin2,ZHANG Dengshan2

(1.School of Computer and Control Engineering,North University of China,Taiyuan 030051,China; 2.Da Liuta Coal of Shen Hua Shendong Coal Group Corporation Limited,Yulin Shenxi 7193315,China)

Abstract:In data acquisition,the performance of data collection systems like stability,speed quickly and control even from long recieving distance is very important.Aiming at these requirements,a research is made on a data acquisition and control system based on a software development platform called LabVIEW.Through,two kinds of communication methods,Ethernet and wireless,complete the PC and multi-channel data acquisition system of transmission and the remote control of the acquisition system.Furthermore,data preview,storage,playback and preprocessing can be completed in the system.In addition,the functions of self-inspecting,resetting and memory erasing are realized.Practical application proves that each of the operations above can be accomplished in the system.

Key words:data acquisition system; LabVIEW; ethernet communication; wireless communication

中图分类号:TN914.1

文献标识码:A

文章编号:1005-9490(2015) 03-0576-06

收稿日期:2014-06-25修改日期: 2014-07-18

doi:EEACC: 615010.3969/j.issn.1005-9490.2015.03.021