基于FPGA的通用PCM接收解码电路的设计

2015-02-26谢秀峰苏淑靖

谢秀峰,苏淑靖

(中北大学电子测试技术重点实验室,太原030051)

基于FPGA的通用PCM接收解码电路的设计

谢秀峰,苏淑靖*

(中北大学电子测试技术重点实验室,太原030051)

摘要:为了准确接收提取某遥测系统的PCM数据,设计了基于FPGA的通用PCM接收解码电路,该电路通过基于锁相环的位同步器实现不同码率的PCM数据流接收,通过三态搜索理论的帧同步器可判别不同帧结构数据,码型转换模块识别并转换NRZ-L/M/S、BiФ-L/M/S 6种码型,最后电路将解调出的数据通过USB接口传送至计算机进行存储、显示和处理。该电路可识别码型不同、码速率不同以及帧同步码组不同的PCM数据流,兼有单端和差分输入接口,在遥测领域具有很强的通用性。关键词:PCM; FPGA;通用;位同步;帧同步

脉冲编码调制(PCM)是一种将模拟信号转换为数字信号的基本方法,目前,它不仅用于通信领域,还广泛应用于计算机、数字仪表、遥控遥测等许多领域。而高速遥测PCM数据是遥测系统测量卫星、航天器及武器系统等内外部的环境参数[1-2],地面计算机通过被测目标传回的数据,确定其工作状态以及各项性能。为了弥补目前遥测接收装置只能读取参数固定、码型单一以及码率不变的PCM技术的不足,本文设计了基于FPGA的通用PCM接收解码电路,其中可靠的同步技术是实现数据准确接收的关键,该电路以Xilinx公司的Spartan3E系列FPGA芯片XC3S500E为核心,采用基于锁相环的精确位同步和基于三态搜索的双重校验判决帧同步方法,实现PCM码速率为1 Mbit/s~10 Mbit/s的可靠接收,并可对NRZ-L/M/S、BiФ-L/M/S 6种码型解码且无误码,可判别EB 90H和9A BC B5 2CH这两个常用帧同步码组,以上特点不仅满足了当前使用的背景要求,而且可应用于其他PCM通信领域。

1 总体设计方案

不同的场合所用的PCM数据流属性不同,为满足不同的场合的应用需求,设计了本通用接收解码电路,其总体方案如图1所示。其中接收解码电路主要由输入接口模块、FPGA逻辑控制模块及USB接口通信模块3部分组成,其中FPGA的功能包括位同步、码型转换、帧同步以及全局的逻辑控制和时序控制。总体工作流程为:通过单端或差分接口输入的PCM码流先经过位同步器实现不同码速率的精确位同步,并从中提取出数据流的时钟信息,经过码型转换的数据接着通过帧同步器确定其内容中的帧格式实现帧同步,在帧同步后将解码得到的有效数据打包并上传至计算机进行分析及处理。

图1 总体方案框图

2 FPGA模块设计

2.1位同步器

位同步是正确解码的基础,只有正确取得位同步之后,才能实现帧同步。位同步器主要功能是通过精确调整使得位同步脉冲与输入PCM码流实现同频同相,并输出定时脉冲序列[3]。

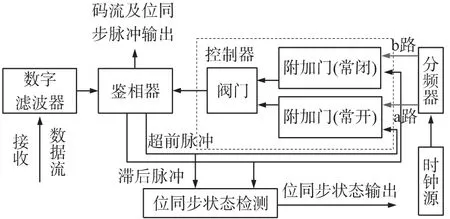

本文采用直接位同步数字锁相环方法实现位同步器设计。位同步器由时钟源、分频器、鉴相器、数字滤波器和控制器所组成,控制器又包括“或门”、附加门和扣除门(如图2)。时钟源为高稳定晶振,分频器采用直接数字频率合成技术产生1 MHz~10 MHz的时钟脉冲[4-5],这样在收到计算机下发的PCM码速率的频率控制字后,分频器就能产生对应的时钟脉冲来匹配不同码速率的PCM码流。由于噪声的存在和信道干扰,使接收码元产生抖动,每个码元的边沿幅度抖动是造成码元相位判断误差的直接原因,所以需要对输入的数字信号经过数字滤波器滤波,以利于对整个码元周期的判定。

图2 位同步器原理组成

位同步器工作原理如下:假设接收到的PCM码率为f0,时钟源输出的时钟信号经分频器分频后,再通过扣除门和或门,得到的位同步信号频率为f0,如果不能和收到的码元精确同频同相,就需要参考鉴相器输出的判断信号,通过控制器进行适当调整。当位同步脉冲比输入码元的相位超前时,鉴相器输出一个超前脉冲到扣除门(常开)扣除一个a路脉冲,使位同步脉冲的相位推迟1/n周期(2π/n);若分频器输出的位同步脉冲相位比输入码元的相位滞后,那么加于附加门(附加门常闭)的b路脉冲序列就会同时输出一个脉冲通过“或门”,由于b路与a路相位相差π,所以这个脉冲会插入在原a路脉冲中间,分频器就提前了1/n周期的相位输出。如此反复几次,输出的位同步脉冲就与PCM码流同频同相,即可被帧同步器用作时钟。

2.2码型转换

位同步后需要将不同码型的数据转换为NRZ-L码,这样可减小帧同步的资源占用,码型转换的原理如下:

设pcm_n为当前输入,pcm_pre为前一个输入,pcm_out为转换后的输出,对于NRZ-M:

对于NRZ-S:

而对于BIΦ码则需要先以原码率的二倍速率取得对应值,以此判断出码元的正确起始位置,然后再根据相应规则转换码型,转换公式分别如下:

BiΦ-L:pcm_out=pcm_in(3)

BiΦ-M:pcm_out=pcm_in XOR pcm_pre(4)

BiΦ-S:pcm_out=pcm_in XNOR pcm_pre (5)

图3为NRZ-L的数据为101100011010的各种码型的转换结果。

图3 码型转换图

2.3帧同步器

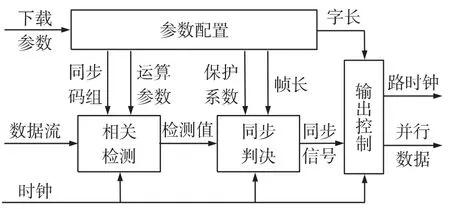

帧同步器的功能是从位同步器输出的PCM串行数据流中提取出帧同步码组,产生帧同步信号,从而完成数据分离。为了实现帧同步,发送端在数字信息流中插入一些特殊码组作为每帧的头尾标记,帧同步器需要准确无误的判断出这些码组,以确定帧结构[5-6]。目前较常用的同步码组主要有两组,一组是副帧标志为EB 90H,帧结束标志为14 6FH[7],另一组是9A BC B5 2CH与65 43 4A D3H的配合使用。在本设计中,帧同步器可根据参数配置模块下发的同步码组参数来选择对应码组进行帧同步。

帧同步器各功能模块主要有:参数配置模块,相关检测模块,帧同步状态控制模块和输出控制模块,其工作原理图如图4所示。

图4 帧同步原理图

帧同步器首先从计算机接收帧结构参数,由参数配置模块完成各参数配置,包括帧同步码组、帧长、同步容差和同步保护参数。然后当检测到串行数据流输入时,相关检测器进行相关运算,检测是否有同步码组出现,并将检测值实时送至同步判决电路;同步判决模块根据检测值完成对同步状态的控制,同步状态有搜索、校验、锁定3种状态,当状态机进入锁定态时,表示达到帧同步,输出帧同步信号;最后,输出控制模块在帧同步信号的控制下,将串行数据转换为并行数据和附带时钟信号一并输出,完成数据的提取。

同步判决模块的主体为一个状态机,它根据相关检测器的检测值控制状态机的状态转换,并控制产生帧同步信号。其状态转换关系如图5所示。s代表同步容差,当相关检测值d≤s时,便看作检测到帧同步码组。这样即使由于干扰造成s位的误码,也可以检测到帧同步码组。其余两个参数α(前向校验门限)和β(后向校验门限),为帧同步状态起到保护作用。

状态机的初始状态为搜索态,同步之前,判决模块会在每个时钟比较d与s的值,当检测到d小于s时,便可以判定为检测到帧同步码,并立即启动状态机转到入锁校验态。

在入锁校验态,为了避免受信号中假同步码的影响,当检测到帧同步字后,会每隔一帧长度对检测值进行判决。当连续α次判决正确时,则判定为找到帧同步信号,并控制状态机进入锁定态,否则,判定为假同步,并回到搜索态接着进行搜索。

图5 状态转换关系图

进入锁定态后,状态机开始输出帧同步信号到输出控制模块,同时判决模块每隔一帧对检测值进行判决,当丢失帧同步信息时,便进入失锁校验态。这时,如果连续β次丢失帧同步信号,则判定已经失步,控制状态机进入搜索态,重新开始搜索;如果期间又检测到帧同步码组,则回到锁定态。

双重校验的判决可在捕获或失步发生时相应的增加其置信度,当达到一定值时才认定捕获或失步事件发生,这样帧同步器具有较强的保护能力。在实际使用时,可以针对不同的帧结构和信道传输特性,采用合适的容差值和保护参数,最大限度的提升帧同步器的性能。

图6 接口电路原理图

3 输入接口电路

解码电路具有单端接口和差分接口,两个接口通过数字隔离器进行隔离及电平转换。单端接口输入的PCM数据流通过数字隔离器ADuM1201送入FPGA;差分数据流输入到差分芯片DS26C32,再通过隔离器送入FPGA。接口电路如图6所示。DS26C32的上升下降时间为4 ns,最大不超过9 ns,而PCM码输入信号速率最大为10 Mbit/s,脉宽为100 ns,可见DS26C32完全满足设计要求。

数字隔离器选用AD公司的ADuM1201芯片,该芯片采用iCoupler磁隔离技术,在性能、功耗、体积等各方面都比传统光电隔离器件(光耦)有巨大优势。ADuM1201隔离器在一个器件中提供两个独立的隔离通道。两端工作电压为2.7 V~5.5 V,支持低电压工作并能实现电平转换。传输速率可达25 Mbit/s,瞬态共模抑制25 kV/μs,最大脉宽失真<3 ns,它的转换原理是输入端与输出端使用不同电压供电,将它们作为参考电压实现电平转换。在本设计中芯片输入供电电压为5 V,输出供电电压为3.3 V时,信号可以实现由5 V到3.3 V的电平转换。

4 实测结果

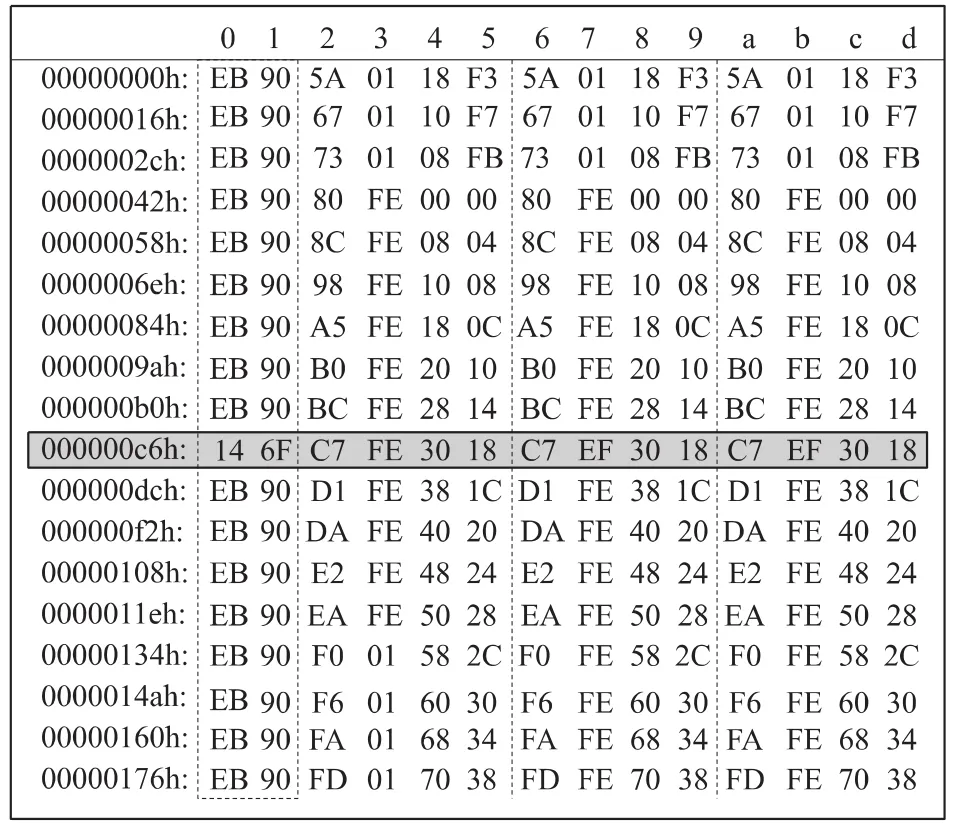

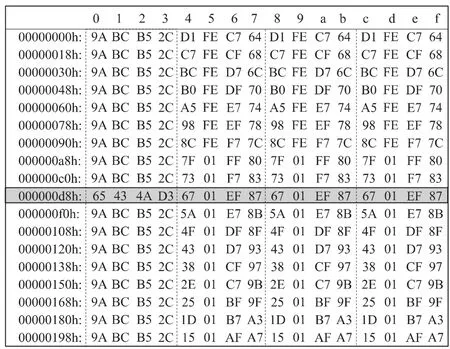

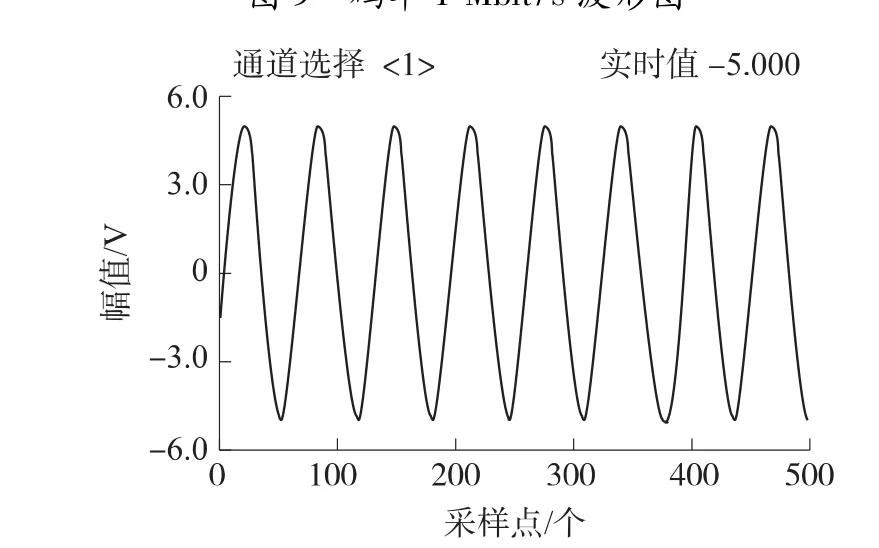

实测时利用一个PCM信号源输出一组固定帧结构的PCM数据流,使用单端接口接入本解码电路,最后通过上位机软件进行显示分析。图7为截取的部分数据,其中副帧的同步码组为EB 90H,帧结束标志码组为14 6FH,每一列的数据为一路,各路分别为正弦波,方波,三角波,锯齿波依次循环3组,加上码组共14列,图8中的数据帧同步码组为9A BC B5 2CH,帧结束标志码组为65 43 4A D3H,同样也是4种波形数据重复3组,共16列。为了验证不同码率的接收效果,用上位机绘图软件来根据不同码率进行波形图绘制,1 Mbit/s时绘图窗口每屏可显示50个采样点,2 Mbit/s可显示100个,依次类推,10 Mbit/s时每屏可显示500个采样点,这里截取了码率为1 Mbit/s (图9)和10 Mbit/s(图10)时绘出的正弦波。

图7 帧同步码组为EB 90H

图8 帧同步码组为9A BC B5 2CH

图9 码率1 Mbit/s 波形图

图10 码率10 Mbit/s波形图

5 结论

本文所设计电路使用FPGA实现PCM解码系统的关键部分,并具有通用单端及差分接,能接收不同帧结构,不同码速率的PCM数据流。经过实际测试,电路工作稳定,抗误码能力强,可根据实际情况灵活配置参数,根据以上特点,该设计对于遥测领域的测试仪器和其他领域的通信设备都具有很大的参考价值。

参考文献:

[1]张彦军,刘龙飞,刘薇.基于FPGA的通用PCM测试仪的设计[J].火力与指挥控制,2013,38(1) :145-148.

[2]张会新,刘波,孟令军.高速遥测PCM数据的AES加密存储系统设计[J].火炮发射与控制学报,2010,10:92-98.

[3]司莹莹.遥控副载波数字化解调器技术研究[J].电子器件,2012,35(2) :181-183.

[4]王耀琦,王小鹏,王静.基于CPLD/FPGA的任意分频器设计研究与仿真[J].兰州大学学报,2010,29(4) :9-13.

[5]习莹冰,杨健.基于FPGA的低杂散直接数字频率合成器设计与实现[J].电子器件,2011,34(2) :199-201.

[6]武向萍,李安宗,吴晓杰,等.PCM遥传信号数字解码方法的设计与实现[J].石油仪器,2004,18(5) :19-20.

[7]甄国涌,林华亮.串行PCM码流解码电路设计与应用[J].航空计算技术,2005,35(1) :79-81.

[8]林华亮,翟成瑞,甄国涌.串行高速差分PCM码流信号的解码电路设计[J].弹箭与制导学报,2005,25(1) :225-226.

谢秀峰(1989-),男,汉族,山西原平人,硕士研究生,主要研究方向为动态测试与智能仪器,xxfzb2008@ sina.com;

苏淑靖(1971-),女,汉族,山西吕梁人,副教授,硕士生导师,主要研究方向为感知与探测,信号处理sushujing @ nuc.edu.cn。

项目来源:河南省省院科技合作项目(131PYSGZ211);郑州市院士工作站建设计划项目(122106000049)

Design of Picosecond Short Pulse Based on Dual NOT Gates Structure*

ZHAO Hongmei*,WANG Yuanpu,CUI Guangzhao

(Institute of Electric and Information Engineering,Zhengzhou University of Light Industry,Zhengzhou 450002,China)

Abstract:Narrow pulse generation is a key technology in Ultra-wideband communication systems,and different applications have different requirements for pulse generation.This paper analyzes several conventional Ultra-wideband narrow pulse generation methods in Ultra-wideband indoor positioning system.Their advantages,disadvantages and the existing problems are discussed.On this basis,a pulse generator is designed based on digital method firstly.Then propose a novel Ultra-wideband narrow pulse generation method which based on dual NOR gates structure by analyzing the simulation results of the designed pulse generator.The simulation results show that pulse repetition frequency obtained by using the method is 10 MHz,and the duration time is 150 ps.The experimental circuit test results are basically consistent with the theoretical analysis and simulation results.Compared with the conventional narrow pulse generation method of digital circuit,this method is simple,low cost and the requirement is not high to the devices.Moreover,the obtained pulse width is narrower than dozen times and higher positioning accuracy.

Key words:Ultra-wideband; picosecond level short pulse; digital circuit; the race and competition phenomenon; dual NOT gate

中图分类号:TN707

文献标识码:A

文章编号:1005-9490(2015) 03-0543-05

收稿日期:2014-06-06修改日期:2014-07-10

doi:EEACC:1230J10.3969/j.issn.1005-9490.2015.03.015