一种高精度无运算放大器带隙基准源

2015-02-26朱铁柱张明星王良坤马成炎

朱铁柱,张明星,王良坤,马成炎

(中国科学院微电子研究所,北京10092)

一种高精度无运算放大器带隙基准源

朱铁柱,张明星,王良坤,马成炎*

(中国科学院微电子研究所,北京10092)

摘要:设计并实现了一种新型无运算放大器的高精度带隙基准源。该带隙基准源在设计中避免使用了运算放大器,减少了系统失调,降低了功耗;利用二次补偿温漂电路,减少了温漂系数。采用0.35 μm BCD工艺模型进行仿真设计,结果表明,常温下输出电压为1.194 V,PSRR在1 kHz下达-74 dB;在-40℃到100℃变化时,基准电压的温漂系数低达2.57×10-6/℃。关键词:BCD;带隙基准源;无运算放大器;二阶补偿

带隙基准源是集成电路的重要单元模块,是许多模拟和混合电路系统的基本组成部分[1]。高性能的数据转换器、电源管理和无线接收机等电路系统要求基准源具有高的温度稳定性、高的电源抑制比和良好的环路稳定性。

为了提高带隙基准源的电源抑制比和降低温度系数,复杂电路结构层出不穷,使得带隙基准源的设计变得越来越复杂,功耗和稳定性等问题也随之产生。

本文提出了一种改进的带隙基准源电路。该基准源在传统的Brokaw带隙基准源[2]电路基础上,避免使用运算放大器,对温漂进行了二次补偿,电路结构简单,具有更好的特性参数,满足了高精度要求,目前,已成功应用于一款步进电机驱动芯片。

1 传统带隙基准电路

传统的带隙基准电路[3]如图1所示。

图1 传统带隙基准源

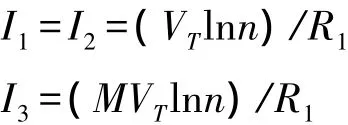

晶体管Q1和Q2工作在不同的电流密度下,它们的基极-发射极电压的差值为ΔVBE=VTlnn,与绝对温度成正比。运算放大器A1使得节点X和Y由于运算放大器A1的作用,具有相同的电位,即VX≈VY。因此,流过M1、M2和M3管的源漏电流分别为

PTAT电流I3流过电阻R2,即可产生PTAT电压I3·R2,将PTAT电压与双极晶体管Q3的基极-发射极电压相加,得到了基准电压

适当选取R1、R2、M和n的比例关系,得到T = 300K时的零温度系数电压基准源。

2 新型高精度带隙基准源

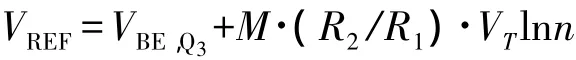

新型无运算放大器电路如图2所示,其中Ⅰ为电路启动部分,Ⅱ为基准核心部分,Ⅲ为二阶补偿电路。电流偏置采用折叠式共源共栅结构,提高了电路的电源抑制比。

图2 新型无运算放大器带隙基准源

2.1启动电路

启动电路如图2中I部分所示,其中M24采用倒比管,宽长比很小,具有非常大的导通电阻。当电源电压VDD上电之后,晶体管M24导通,拉高M25栅极电压,M25导通,使得M26也导通,从而使得双极晶体管Q2、电阻R2、R3和MOS管支路形成导通支路,启动PTAT基准电流的电流镜电路。当电路启动后进入正常工作模式,产生基准电流,流过晶体管M27、M28和M22的电流被M23镜像,又由于M24宽长比很小,从而使得M23工作于线性区,漏极电压接近为零,从而关闭晶体管M25,不对其他电路部分造成影响。

2.2无运算放大器电路的实现

传统的带隙基准电路中,运算放大器使得双极晶体管Q1和电阻R1上的压降之和等于双极晶体管Q2的压降,这要求运算放大器具有较高的增益、较小的输入失配,加上运算放大器本身的频率补偿,使得电路的环路稳定性降低,电路设计变得复杂。本文提出了一种新的结构,引进了晶体管M1、M2和M3,其中M2的栅极与漏极短接,M3提供了流过Q1和Q2的基极电流,同时M3决定了双极晶体管Q1和Q2的集电极电压。

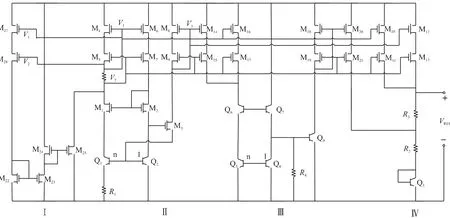

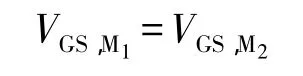

由于M4和M6的电流镜像作用,流过M1和M2的电流大小相等,即

忽略晶体管的沟道长度调制效应,即有

M3提供了流过晶体管Q1和Q2的基极电流,所以

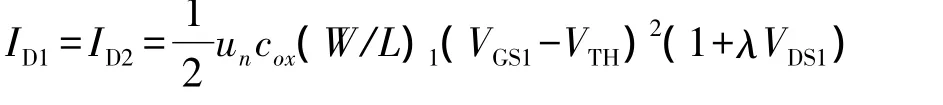

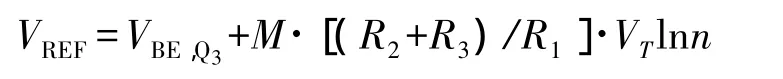

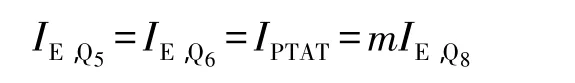

将IPTAT电流流过电阻R2、R3和双极晶体管M3,即得到

合理设置M大小、电阻比例即可得到300 K时温度系数为零的带隙基准源。

2.3二次温漂补偿电路设计

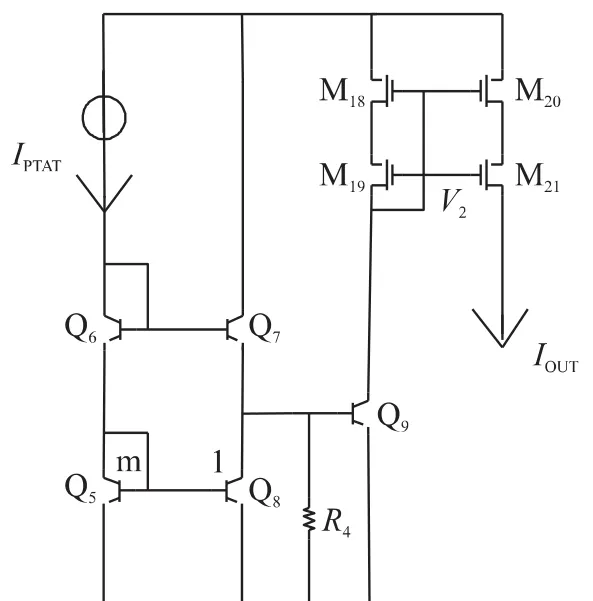

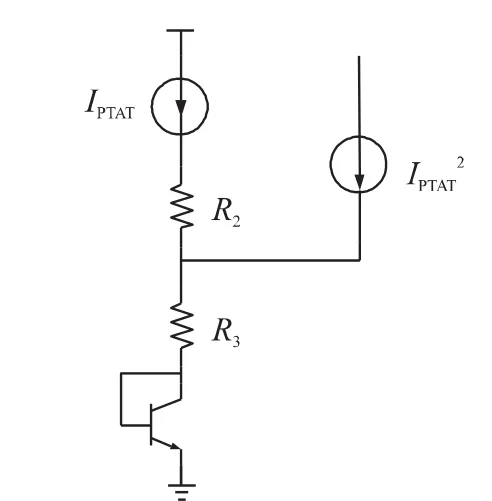

由于对VBE的一阶线性补偿难以满足SOC芯片内部的高精度电路模块的性能要求,故设计图3所示的结构产生IPTAT电流对VBE进行二次温漂补偿,补偿原理[4]如图4所示。

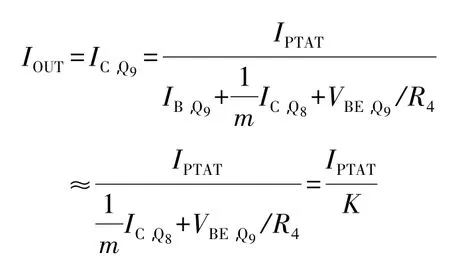

因此,可以得到

满足了带隙基准源生成IPTAT电流的要求,流过晶体管M1、M2和M3的电流之和即为IPTAT电流

图3 无运放带隙基准电路

图4 PTAT2电流产生电路

图中,流过双极晶体管Q6和Q5的为IPTAT电流,即

又有

得到

所以

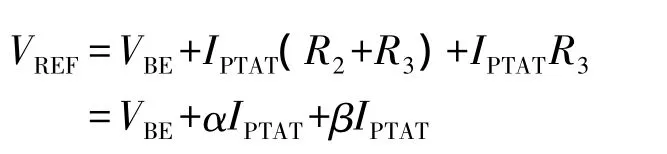

在原来的带隙基准基础上添加图4(a)所示的IPTAT电流产生电路,对VBE进行二次温漂补偿,补偿原理如图5所示,即在原来的IPTAT电流基础上,将IPTAT电流注入到部分电阻上。输出参考电压的表达式即为

式中:,α、β为常量,T为温度。

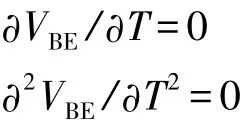

经过二次补偿,使得

经此补偿之后,VBE的非线性只剩下3次及3次以上的高次非线性项,温度系数进一步得到优化。

图5 带隙基准二次补偿原理

3 仿真结果及分析

基于HHNEC的0.35 μm BCD工艺模型,采用Cadence Spectre软件进行仿真设计。

图6所示电路的启动过成曲线,电路启动正常,启动时间小于3 μs,符合设计要求。

图6 带隙基准源启动曲线

图7 一次温漂补偿后的温漂曲线图

图7和图8分别为经过一次温漂补偿及二次温漂补偿后的温漂曲线图。无运算放大器带隙基准电压进行一次补偿后的输出温漂在-40℃至+100℃的温度范围的输出波动约1.516 mV,温漂系数为10.8×10-6/℃。经过二次补偿后,输出温漂在-40℃至+100℃的温度范围的输出波动约361 μV,温漂系数为2.57×10-6/℃。

图8 二次温漂补偿后的温漂曲线图

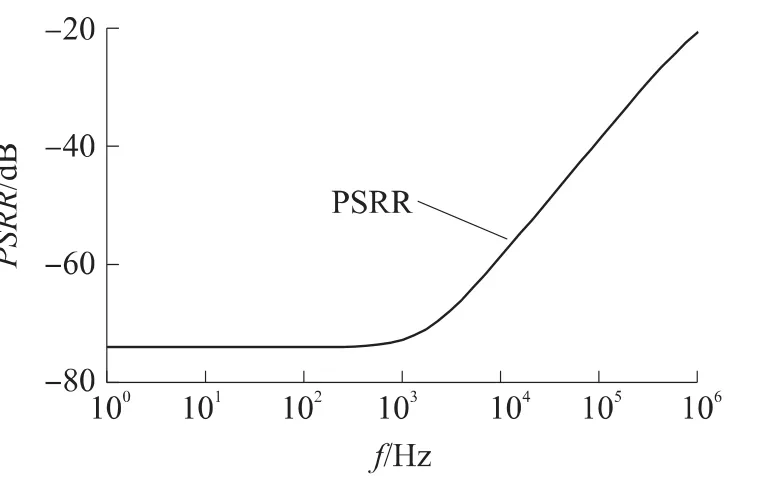

电源抑制比是基准电压源的另一个重要特性,对本电路的PSRR特性进行方针分析,电路的PSRR特性曲线如图9所示。可以看出,电路在低频下电源抑制比为-74 dB,电路整体性能良好。

图10所示为电路的在27℃情况下的DC扫描结果。可以看出,电路具有较宽的电源电压输入范围。

图9 带隙基准源的电源抑制比

图10 带隙基准源直流特性曲线

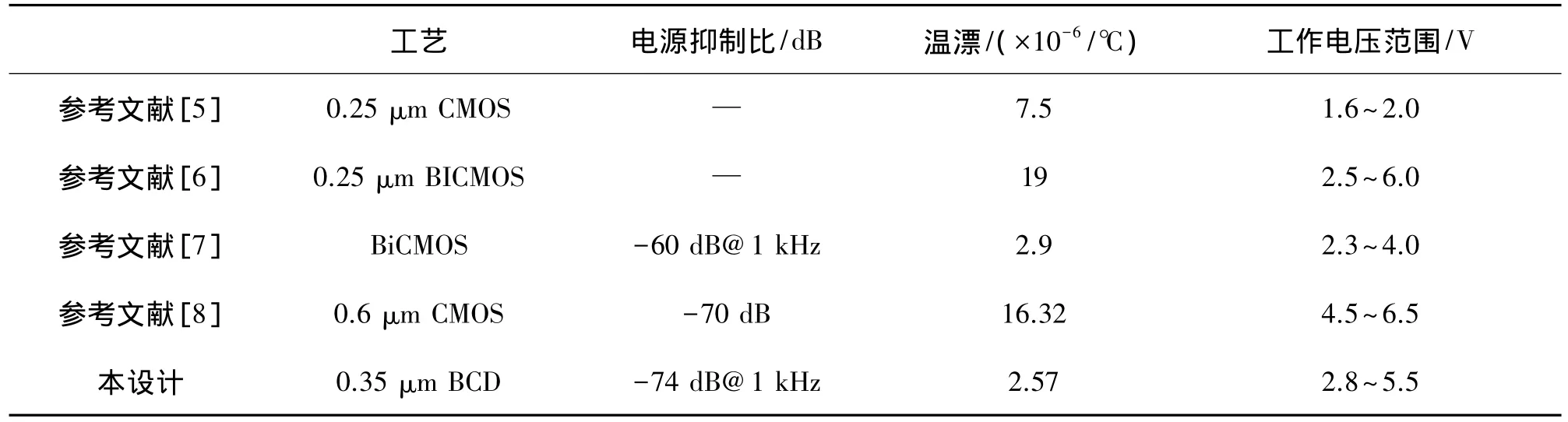

与其他相关研究的性能参数比较,本文设计带隙基准源的PSRR性能以及温漂系数具有较明显的优势,如表1所示。

表1 本文带隙基准预源与相关文献中电路比较

4 结论

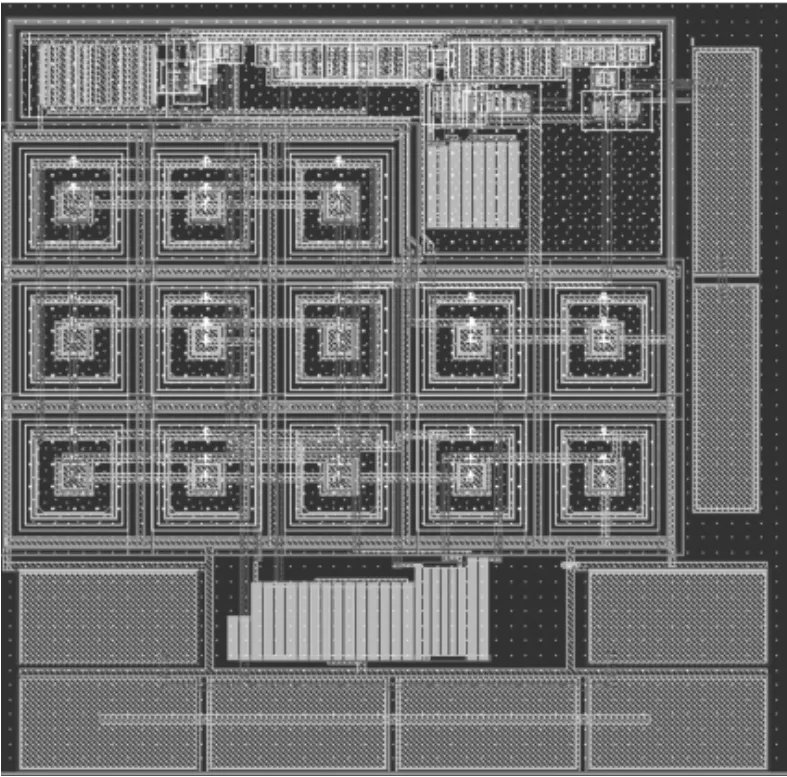

本文提出了一种新型的无运算放大器的带隙基准源,该带隙基准源利用相同电流流过相同比例尺寸的晶体管时晶体管的栅源电流大小相同这一特性,避免使用了运算放大器。CASCODE电流镜等结构减小了传统带隙基准的系统失调和运放失调的影响,同时提高了基准电压的电源抑制比。添加的二次温漂补偿结构减少了温漂系数,使得设计的带隙基准源具有高精度特性。新型带隙基准源的版图如图11所示,已成功用于一款步进电机驱动芯片并流片,并可以广泛应用于数据转换器、电源管理等其他芯片。

图11 带隙基准源版图

参考文献:

[1]丁德彬,杨依忠,张章.基于电荷泵的低压启动高效率BOOST DC/DC变换器设计[J].电子器件,2013,36(2) :211-216.

[2]Brokaw A P.A Simple Three-Terminal IC Bandgap Reference[J].IEEE J Sol Sta Circ,1974,9:388-393.

[3]何乐年,王忆.模拟集成电路设计与仿真[M].北京:科学出版社,2008:196-204.

[4]Paul R,Patra A.A Temperature Compensated Bandgap Voltage Reference Circuit for High Precision Applications[C]/ /India Institute of Technology,Kharagpur 721302,Dec,2004.

[5]Ker M D,Chen J S.New Curvature-Compensation Technique for CMOS Bandgap Reference with Sub-1-V Operation[J].Circuits and SystemsⅡ:Express Briefs,IEEE Transactions on,2006,53(8) :667-671.

[6]杨晓春,于奇,宋文青.一种采用斩波调制的高精度带隙基准源的设计[J].微电子学与计算机,2013(1) :23.

[7]丁大胜,徐世六,王永禄.一种分段温度补偿BiCMOS带隙基准源[J].微电子学,2012,42(3) :340-343.

[8]梁爱梅,凌朝东.电流镜型二次曲率补偿的带隙基准源设计[J].华侨大学学报:自然科学版,2010,31(3) :267-271.

朱铁柱(1988-),男,汉族,江苏淮安人,博士研究生,研究方向为混合集成电路设计,zhutiezhu@ casic.ac.cn;

马成炎(1958-),男,汉族,江苏无锡人,研究员,研究方向为模拟与射频集成电路设计,machengyan@ casic.ac.cn。

The Design of General PCM Receiving and Decoding Circuit

XIE Xiufeng,SU Shujing*

(National Key Laboratory of Electronic Measurement Technology,North University of China,Taiyuan 030051,China)

Abstract:In order to accurately extract the PCM(Pulse Code Modulation) data received from a telemetry system,a common PCM receiving and decoding circuit based on FPGA is designed.The circuit can receive PCM data of different rate by using the bit synchronizer based on phase-locked loop.Its frame synchronizer is based on three-state searching theory so that it can distinguish the data with different structure.The code converter module can convert the six patterns that is NRZ-L/M/S,BiФ-L/M/S.At last the demodulated data is sent to the computer through the USB interface for storage,display and processing.The decoding circuit can identify PCM data stream which has different rates,different patterns and different frame synchronizing code groups.It has both single-ended and differential input interfaces,so it has strong versatility in the field of telemetry.

Key words:PCM; FPGA; general; bit synchronize; frame synchronize

中图分类号:TN432

文献标识码:A

文章编号:1005-9490(2015) 03-0538-05

收稿日期:2014-06-06修改日期:2014-08-04

doi:EEACC:6120B10.3969/j.issn.1005-9490.2015.03.014