EAPR 设计中动态模块间总线宏实现方法

2015-01-23申正义

□赵 鹏 申正义 张 勇

现阶段,高密度FPGA 生产工艺实现难度增大,而且在使用时布线复杂度也呈几何数上升,然而局部动态可重构(Dynamic Partial Reconfiguration,DPR)技术的提出解决了这个问题。局部动态可重构是指重新配置时仅配置FPGA 部分区域,重构过程中,FPGA 其余部分的工作不受影响。该方式减少了单元数目和重构范围,从而大大缩短了FPGA 的重构时间。

一、FPGA 局部动态可重构中总线宏简介

局部动态重构中,系统被划分为静态模块和动态模块,其中动态模块即是可重构部分。静态模块间的通信可以通过简单的直接路由实现,对于动态与静态模块间和动态与动态模块间的通信就由总线宏来实现。局部动态重构设计,总线宏部分作为难点不易实现,文献[1]中提出了总线宏的分类和结构分析,文献[2]中提出的总线宏设计流程是基于三态缓冲器(TBUF)针对老式芯片的设计方法,文献[3]中提出了EAPR 设计流程中的基于slice 的总线宏设计方法,但其仅局限在静态模块和动态模块间的总线宏通信,未涉及动态模块间的总线宏设计,所以局限了EAPR 设计的灵活性,不利于EAPR 应用在更为复杂的电路设计。

二、动态模块间总线宏实现方法

本设计方法是以ML505 开发板为硬件实验平台,以ISE9.1i 和PlanAhead9.2.7 系列软件为依托进行动态模块间的总线宏通信研究。与传统的总线宏设计不同,EAPR 的总线宏不再需要复杂的编程,而是通过模块例化,在软件中进行可视化的操作实现。下面通过一个实例具体解析动态模块间总线宏的实现过程。

(一)获取官方总线宏nmc 文件。首先在Xilinx 官网注册用户,进入总线宏下载页选则相应芯片,由于这里采用的是ML505 开发板,所以选择XC5VLX50T 系列,而后下载得到busmacro_xc5v_async.nmc 文件[4]。

(二)总线宏模块的例化与连线。在EAPR 设计方法中,总线宏必须在ISE9.1i 软件中进行HDL 设计描述和综合,只有建立black box 并定义输入输出才可以在后续程序中调用。通过顶层文件对总线宏模块的例化程序如下:

module busmacro_xc5v_async(input0,input1,input2,input3,output0,output1,output2,output3);

input input 0,input 1,input 2,input 3;

output out0,out1,out2,out3;

endmodule

通过前期实验,针对动态模块间的通信仅使用一级总线宏,在步骤方法一致情况下会在最后的检测分析中反复报错,无法继续进行工程设计,且在其他类文献中没有相应解决方法。尝试性地为两个动态模块各分配一级总线宏,在HDL 程序中,我们定义了bm2 和bm4 两个总线宏的连线,声明了四个端口(bm2_bm4[0.1.2.3]),相应Verilog 代码如下:

busmacro_xc5v_async bm2(

.input0(prm_bm2[0]),

……

.input3(prm_bm2[3]),

.output0(bm2_bm4[0]),

……

.output3(bm2_bm4[3])

);

busmacro_xc5v_async bm4(

.input0(bm2_bm4[0]),

……

.input3(bm2_bm4[3]),

.output0(bm2_prm1[0]),

……

.output3(bm2_prm1[3])

);

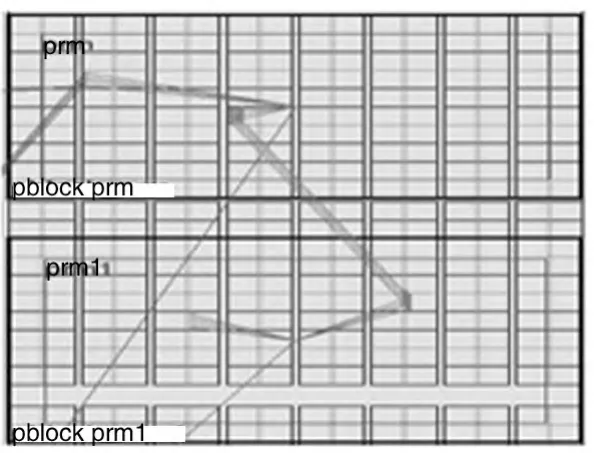

(三)重构区域的建立和总线宏设置。在经过综合后生成网表文件,进入PlanAhead9.2.7 建立工程[5]。如图1,利用该软件可视化的优点在芯片中分配两个动态可重构区域PRM 和PRM1,区域大小取决于后续应用于该动态区域需要的硬件单元数量,且动态区域相互独立不能交集。

图1 分配动态可重构区域

重构区域设置完成后在Netlist 窗口下,选择总线宏bm2,并通过单击菜单栏中Create Site Constraint Mode图标 将其激活,然后将其拖置于动态区域prm 中。bm4 的放置区域为prm1,放置方法同bm2,如图2 中两个总线宏都设置好后可以看到建立在动态区域间的总线宏通信连线。

图2 动态模块间总线宏连线

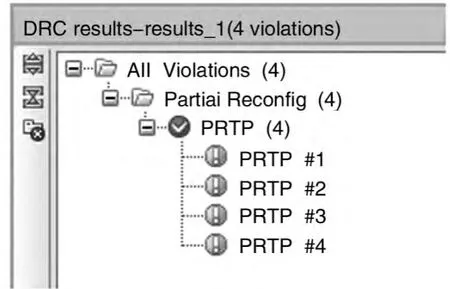

三、检测与分析

在端口和时钟都设置成功后,EAPR 设计的检测部分依然是在PlanAhead9.2.7 软件环境下完成的。PlanAhead9.2.7包含有设计规则检查工具(Design Rule Check,DRC),我们可以通过工具栏中“Tools -RunDRC”选项,如果工程符合设计规则在DRC Results 中将显示检查通过,如图3,仅有四个警告是由于四个端口悬空造成,所以可以得出结论应用此类方法动态模块间的总线宏可以实现。

图3 工程检测与分析图

四、结语

本文提出了一种基于EAPR 技术的动态模块间总线实现方法。通过为两个动态模块分别配置一级总线宏的方式完成了EAPR 设计,并通过分析仿真验证了新方法的正确性,提高了EAPR 在工程上应用的灵活性,拓宽其使用范围,具有一定推广性。

[1]乔守明,祝洪珍,王伟.动态重构中总线宏的结构与实现[J].开发研究与设计技术,2007

[2]赵秋桂,段青亚.FPGA 动态局部可重构中基于TBUF 总线宏设计[J].嵌入式技术,2009

[3]肖松,李跃华,张金林.一种DPR 中总线宏的设计方法[J].电子设计工程,2011

[4]Xilinx Inc.Early Access Partial Reconfiguration User Guide[EB/OL].2006 -3 -6.http://www.xilinx.com/.

[5]Brian Jackson.Partial Reconfiguration Design with PlanAhead 9.2[EB/OL].2007 -8 -2.http://www.xilinx.com/.