全新的高稳定穿墙雷达接收机前端设计∗

2015-01-23

(国防科技大学电子科学与工程学院,湖南长沙410073)

0 引言

近年来,超宽带穿墙雷达成为国内外学者研究的热点,十分适用于反恐、安检和搜救等领域。同时,鉴于国际国内艰巨的反恐形势,加强穿墙雷达系统尤其是其接收机的研究就相当重要了。对超宽带穿墙雷达接收机来说,接收信号为超宽带窄脉冲信号,其频谱很宽[1]。若进行高频实时采样,成本相当高;但若利用等效采样的方法对其进行采样,便会极大地减小对高频超宽带信号采样的难度,而且成本也会大幅度地减小。因此,等效采样这种高速采样手段也越来越成为超宽带雷达接收机发展的必然选择[2]。

上世纪50年代以来,超宽带等效采样技术在摸索中不断发展[3-7],其设计核心为采样门电路。1994年,McEwan系统地阐述了单管采样门、对称采样门、平衡采样门以及桥式采样门的电路结构,分析并总结了它们各自的特点和局限性[8]。后来,Reisenzahn等人充分利用取样相位检测器(Sampling Phase Detectors,SPD)设计了超宽带脉冲接收机,但由于使用的差分运算放大器工作带宽的限制导致重建后的低频信号与原始UWB脉冲信号形状一致性较差[9]。这几种传统的采样门电路对取样脉冲和精密时间延时提出了更高的要求,故取样脉冲产生电路和精密延时电路得以快速发展。取样脉冲产生电路的典型核心器件主要有隧道二极管、阶跃恢复二极管(SRD)和雪崩晶体管等分立元件以及高速逻辑芯片[10]。此外,Han等人还利用传输线原理,结合SRD的阶跃恢复特性实现了脉冲宽度为400 ps的窄脉冲,但这类取样脉冲产生电路结构复杂,且结构不稳定[11]。但精密延时电路大都结合延时时间长的芯片和延时精度高的芯片,利用FPGA的控制以产生延时精度高且延时时间长的延时电路,但两者又难以协调[12]。这一矛盾严重制约着等效采样的采样频率,稳定性更是无法得到保障。

本文优化了传统等效采样技术的采样过程,从根本上解决了精密延时电路对延时精度高和延时时间长难以兼容的难题,提高了信号采集的实时性。同时,基于单片微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)设计了一种全新的等效采样接收机前端实现方案,创造性地利用跟踪保持芯片实现了对接收信号的快速跟踪和保持,克服了传统取样门电路中跟踪保持电路难以在极短的时间内导通和关断的问题,从而能够稳定地保持采集到的高频瞬时信号。此外,这一设计还降低了采集高频信号所需的取样脉冲的要求,降低了成本。

1 改进的穿墙雷达等效采样分析

就目前信号采样的研究现状来说,时域信号的采样方法主要有实时采样和等效采样,而对于周期性的超宽带待采脉冲信号来说,等效采样具有其独特的优势。该方法是在不同的触发周期内取得信号的相位和幅值信息,再按照一定算法对信号进行重构,从而反映出信号完整的波形信息。其中,顺序等效采样能够提供更大的时间分辨率和精度,普遍使用在高速采样系统中。

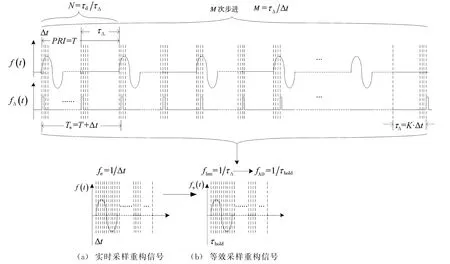

顺序等效采样每次采样都由触发信号来启动,一旦检测到触发信号,采样器会在一个短时间窗内完成采样,当下一次触发到来时,系统会给采样微小的延时增量Δt,进行另一次采样,如此重复多次,后续的采样点均比前一次采样点有一个微小的时延增量Δt,直到遍历整个采样时间窗,数据采集结束后可以按顺序组合重构出信号的特征信息。这种传统的顺序等效采样在每个周期内只采集一个样本,导致信号采集的实时性很差,脉冲重复频率的利用率也很差。而针对穿墙雷达接收机,本文改进了顺序等效采样的采样过程,如图1所示,在每个采样周期内采集多点,成倍地提高了利用率。

图1 改进的穿墙雷达接收机等效采样方法

由图1可知,重构后的信号采样点间隔不完全相等,即不等值步进,但采样时间点有规律:

式中,m=0,…,M-1,n=0,…,N-1,tc为延时信号的传播延时,M为微小时间间隔步进次数,有

N为单个脉冲重复间隔内采样点数目,有

式中,td=2Rmax/c为探测距离所对应的时间,τΔ为距离向扫描单元对应的时间,Δt为步进时间间隔。Ts=T+Δt,其中T为脉冲重复间隔(PRI),采样样本的保持时间τhold决定了后续AD模块所需的最小采样间隔。

设待采信号为f(t),取样脉冲信号为

信号采样的结果为

在传统等效采样过程中,每个周期Ts内仅采集一个样本,即如式(1)中n=0,则有

因待采信号的周期性:f(t)=f(t+T),其等效的实时采样信号为

而优化的顺序等效采样过程在每个时间点t mn上采集一个样本,然后需要以样本采样时间关系进行重新组合,其等效的采样重构信号与采样信号的保持时间有关,为

式(8)经傅里叶变换后得

式中,等效采样频率为

由式(8)和式(10)可知,改进的等效采样过程相当于将待采信号展宽后进行采样,而时域展宽比和频谱压缩系数为τhold/Δt,同时保留了输入信号的所有频率,故而这种改进的等效采样方法是可行有效的。相比于传统等效采样方法,这种方法在一个脉冲重复时间内采集的样本数提高了N倍,样本的采样效率也提高了N倍,而整个扫描距离不变,极大地提高了等效采样的实时性和脉冲重复频率的利用率。

2 接收机前端总体设计

根据图1对改进的等效采样技术分析可知,等效采样接收机在接收到信号之后,需要进行低噪声放大处理,每次采样需要由快速开断的取样门电路来完成,而控制取样门电路选择性地导通和关断是实现新型等效采样接收机的关键,那么,设计精密的延时电路就至关重要。通常,这样精密可靠的延时功能由精密延时芯片来完成,这就需要利用FPGA进行编程控制脉冲触发信号的时序,同时,还能够提供同步时钟信号。

倘若采用传统的等效采样接收机结构,不仅对精密延时电路、取样脉冲产生电路和取样门电路提出了很高的要求,而且因为分立元件难以兼顾快速充电和慢速放电,还会导致样本采集之后无法长时间保持,客观制约了等效采样频率。随着MMIC技术的高速发展,各种高频芯片不断涌现,电路集成的优势也更加明显,于是,基于一种高频的跟踪保持芯片,设计了一种新型等效采样接收机,这种跟踪保持芯片能够很好地具备取样门的功能,而且这种芯片内置的脉冲整形电路也降低了对极窄取样脉冲的指标要求。

因此,取样脉冲可以直接由FPGA模块产生,而不需要特别地设计取样脉冲产生电路。另一方面,这种方法改变了触发脉冲延时和产生触发脉冲的顺序,应该为先由FPGA产生极窄触发脉冲,之后再进行精密的延时。基于跟踪保持芯片的新型等效采样接收机前端设计方案如图2所示。

由图2可知,新型等效采样接收机前端主要由跟踪保持电路(Track/Hold)、精密延时电路、低噪声放大电路(Low Noise Amplifer,LNA)、模数转换(Analog to Digital Converter,ADC)及FPGA组成。外部时钟为FPGA提供精准的时钟信号,FPGA模块主要产生精密时延电路的逻辑控制信号和同步时钟信号,控制精密延时芯片产生顺序时延的时序信号,以触发跟踪保持芯片对接收信号进行高速采样和保持,而采集后的信号保持过后便能够很容易地采集和重构了。而且,优化的接收机结构中跟踪保持芯片集成了脉冲整形网络,故能降低对取样窄脉冲的要求,甚至仅仅需要FPGA产生即可。高频信号有序地采集下来后,后续AD部分需要完成低速率的采样,并送至计算机终端进行信号重组。

图2 基于跟踪保持芯片的新型等效采样接收机前端设计

在超宽带脉冲型穿墙雷达等效采样接收机中,为了达到较好的空间分辨率和穿透性能,接收信号的脉冲宽度为1 ns的单周波脉冲。对这种超宽带脉冲信号进行采样,若要不失真地进行采集,在脉冲宽度内至少需要采集10个样本[1]。那么,采样的时间分辨率最低为100 ps,即在等效采样接收机中,顺序步进延迟的时间最大为100 ps。另外,穿墙雷达的最远探测距离Rmax为30 m,根据td=2Rmax/c,那么接收信号的检测时间范围td为200 ns,延时芯片也需要完成200 ns的精密延时。

3 接收机前端关键模块设计

在基于MMIC跟踪保持芯片的新型等效采样接收机设计中,跟踪保持电路、精密延时电路和FPGA模块是设计的关键,这三个关键模块相互制约,直接决定了冲激型穿墙雷达等效采样接收机的性能。

3.1 跟踪保持电路

跟踪保持电路是新型等效采样接收机设计的核心,主要完成对接收信号进行跟踪和保持,跟踪的速率和样本保持的时间直接关系着其他模块的设计指标,既需要跟踪的速率高,也需要保持的时间长。显然,普通的分立元件无法实现。

根据等效采样接收机的设计指标,跟踪保持电路必须在100 ps的步进时间内完成导通采样和关断,由B≐0.35/τ可知[13],跟踪保持电路的采样带宽需大于3.5 GHz,同时,由于样本保持的时间决定了后续AD模块的采样率,保持的时间越长越好。这样,Hittite公司的HMC660LC4B芯片便是最佳选择,该芯片的采样带宽达到4.5 GHz,样本最大的保持时间为5 ns,同时,时钟频率工作范围宽,可在100~3 000 MHz频段内工作,轻便小巧,集成度高。

但是,跟踪保持芯片HMC660LC4B主要用于数字采样示波器,现将其用于对接收信号的采样保持模式上,若采用原有的工作模式,使用占空比为50%的时钟信号,那么与其同步的接收信号的脉冲重复频率也要很高,这显然是不可能的。本文改进了其工作模式,在保证时钟正脉冲不变的情况下,利用FPGA实现输入时钟频率与接收机的脉冲重复频率的同步,既降低了跟踪保持芯片对输入脉冲的重复频率要求,也保证了跟踪保持芯片能够很好地在合理状态下工作,确保了其稳定性和可靠性。

为了降低输入窄脉冲的要求,接收机前端的跟踪保持芯片HMC660LC4B可工作在100 MHz的时钟频率下,这样,时钟的正脉冲宽度为5 ns,电平为LVPECL,脉冲上下边沿时间为600 ps,这样就明确了精密延时电路和FPGA模块的设计要求。

3.2 精密时延电路

精密延时电路主要产生时序信号,延时的精度直接影响着接收机的采样性能,且时延电路的延时范围决定了接收机所处理接收信号的时间范围,从而决定了冲激脉冲体制穿墙雷达所能够测量的最远探测距离。但是延时精度和最大延时时间相互矛盾,若追求较高精度需要缩短最大延时时间,相反,若追求最大延时时间则要降低延时的精度。

若采用传统的等效采样方法,穿墙雷达接收机需要实现高精度和大范围的延时。根据对冲激脉冲体制穿墙雷达等效采样接收机的分析可知,精密延时电路需要实现的延时范围为200 ns,步进延时时间为100 ps,而为了保证等效采样步进的准确性,步进的精度要求为步进时间的10%,即10 ps。若采用传统的等效采样技术,则要求高精度和大范围的延时,通常采用两级串联延时模式,但端口不匹配和延时精度难以统一。因此,本文优化了传统等效采样技术的采样方法,改进后的等效采样方法利用距离分段扫描方法,从而避免了长时段的延时。

具体来说,穿墙雷达的最大探测距离为30 m,而精延时芯片所能够延时的最大时间为10 ns,其对应的扫描距离为1.5 m,则可将其分为20个距离单元,每个距离单元对应的检测时间τΔ=10 ns,故延时的范围就为10 ns,故只需保证10 ps的延时精度即可。而ON Semiconductor Inc的 MC100EP196A延时芯片便能够轻易实现,同时还避免了端口的不匹配和延时精度的不统一问题。

MC100EP196A芯片的10位控制位能够完成10 ns的精密延时,其延时传播时间tc=2.2 ns,输出信号边沿的上升下降时间为120 ps,脉冲输出为LVPECL电平,能够满足跟踪保持芯片对触发信号电压的要求。

3.3 FPGA模块

FPGA模块主要完成精密延时电路的时序控制功能以及取样脉冲的产生。根据图1的分析可知,取样脉冲可由FPGA直接提供,经过精密延时电路适当的延时到达跟踪保持芯片,以完成对接收信号的采集和保持。整个延时功能是由FPGA控制的,时序的控制体现了优化等效采样方法的思想。

而取样时序控制是该模块设计的核心,由锁相环产生200 MHz的FPGA外部时钟驱动,是FPGA模块产生时序信号和逻辑控制信号的基准信号。由于精密延时芯片要求LVPECL的输入电平,并参考控制字的逻辑位数,FPGA模块可选择MAX7000AE系列的EPM7064AETC100-10芯片,其输出电平为3.3 V,能够完成对逻辑控制位和输入时钟的电平要求。根据FPGA模块的设计目标,设计的逻辑控制信号和触发脉冲信号时序如图3所示。

由图3可知,外部输入的200 MHz时钟信号是FPGA所有时序信号的基准同步信号,启动参考信号Sweep_Strobe是在收到上位控制信号Reset后产生,开始一个完整的扫描周期;1 MHz的时钟信号作为穿墙雷达的脉冲重复频率(PRF),由距离扫描范围td和距离分段扫描时间τΔ可知,整个探测距离分为N=td/τΔ=20段,因而在同一脉冲重复间隔T内,相邻触发脉冲上升沿之间的时间差为10 ns,触发脉冲宽度为5 ns;而由距离分段扫描时间τΔ和步进时间间隔Δt可知,每个扫描周期内步进的次数为N=τΔ/Δt=100次,因为MC100EP196A的步进精度为10 ps,那么延时芯片的控制字每当1 MHz时钟到来后延时计数加10,编程测试结果如图4所示。

由图4可知,Clk_200M信号作为FPGA的基准信号,每当Clk_200M上升沿到来时,产生一个窄脉冲触发信号,200个Clk_200M信号时间相当于一个Clk_1M的时间;当Clk_1M信号的上升沿到来时,控制输出信号MC_Value就增加10’d10,这样,每个Clk_1M周期内就包含有20个窄脉冲信号,总时长为200 ns,如图4(a)所示。因为每次延时步进时间为100 ps,这样,步进信号每延时10 ns需要10个Clk_1M周期,则MC_Value一个完整的步进控制时间为10∗1μs,如图4(b)所示。如此,即可实现对延时精度10 ps,总延时时间为200 ns的延时控制。仿真结果与理论分析设计相吻合,很好地验证了逻辑控制信号的相对关系,能够为精密延时电路提供精准的延时信号。

需要注意的是,由于MC100EP196A芯片存在传输时间,这会导致每次的延时都要比理想的延时“晚”2.2 ns,但每次控制延时都会晚相同的时间,故整个延时时间窗就整体“晚”2.2 ns,相当于扫描距离窗“外推”,但这些对采样的结果影响不大。

图3 FPGA模块逻辑控制信号和触发脉冲时序分析

图4 FPGA模块逻辑控制信号和触发脉冲信号时序测试

4 结束语

本文改进了传统等效采样的采样模式,讨论和分析了其可行性,提出了新型超宽带等效采样接收机前端的设计思路和方法,理论分析并仿真论证了优化的等效采样方法。理论分析与仿真测试结果一致性良好,充分论证了实现10 GHz的等效采样频率的可行性。与现有技术相比,该方案充分发挥了MMIC跟踪保持芯片的高重复频率、高稳定性和高度集成的优势,极大地提高了传统等效采样的实时性,降低了等效采样技术对取样脉冲信号的要求,减小了精密延时信号的延时时间范围。电路元器件数量少,结构紧凑,集成度高,极大地简化了接收机的结构,又能获得极佳的性能。同时,还避免了分立元件搭建等效采样电路所带来的不稳定性和不可靠性,可以很好地应用在穿墙雷达等效采样接收机中。下一步的研究重点将是进一步提高信号采集的可靠性,可通过多次采样的累加值作为样本,提高信噪比,为更精确更快速地采集高频信号打下良好的基础。

[1]费元春.超宽带雷达理论与技术[M].北京:国防工业出版社,2010:41-46.

[2]沈绍祥,叶盛波,方广有.基于无载频脉冲雷达信号的高速数字采样方法与实现[J].雷达学报,2012,1(2):136-142.

[3]KAHRS M.50 Years of RF and Microwave Sampling[J].IEEE Trans on Microwave Theory and Techniques,2003,51(6):1787-1805.

[4]周维,王赤,田茂,等.基于等效时间采样的探地雷达回波信号采样方法研究[J].雷达科学与技术,2004,2(1):43-47.ZHOU Wei,WANG Chi,TIAN Mao,et al.Research on a Sample-Collecting Method of Echo Data of Ground Penetrating Radar Based on Equivalent Time Sampling[J].Radar Science and Technology,2004,2(1):43-47.(in Chinese)

[5]CHEN C,WU S,MENG S,et al.Application of Equivalent-Time Sampling Combined with Real-Time Sampling in UWB Through-Wall Imaging Radar[C]∥International Conference on Instrumentation,Measurement,Computer,Communication and Control,Beijing:[s.n.],2011:721-724.

[6]LIU Q,WANG Y,FATHY A E.A Compact Integrated 100 GS/s Sampling Module for UWB See Through Wall Radar with Fast Refresh Rate for Dynamic Real Time Imaging[C]∥Radio and Wireless Symposium(RWS 2012),Santa Clara:[s.n.],2012:59-62.

[7]LIU Q,WANG Y,FATHY A E.Towards Low Cost,High Speed Data Sampling Module for Multifunctional Real-Time UWB Radar[J].IEEE Trans on Aerospace and Electronic Systems,2013,49(2):1301-1316.

[8]McEwan.Ultra-Wideband Receiver:US,5345471[P].1994-09-06.

[9]REISENZAHN A,BUCHEGGER T,SCHERRER D,et al.A Ground Penetrating UWB Radar System[C]∥The Third International Conference Ultra-Wideband and Ultra-Short Impulse Signals,Sevastopol:[s.n.],2006:116-118.

[10]ALESSIO D A,MARCO D,RICCARDO G,et al.Experimental Comparison of Low-Cost Sub-Nanosecond Pulse Generators[J].IEEE Trans on Instrumentation and Measurement,2011,60(1):310-318.

[11]HAN J,HUYNH C,NGUYEN C.Tunable Monocycle Pulse Generator Using Switch Controlled Delay Line and Tunable RC Network for UWB Systems[C]∥IEEE International Symposium on Antennas and Propagation,Toronto:[s.n.],2010:1-4.

[12]YANG J,LIU S,ZHU C,et al.Equivalent Sampling Oscilloscope with External Delay Embedded System[C]∥IEEE International Conference on High Performance Computing and Communications,Banff:[s.n.],2011:195-201.

[13]LEE J S,NGUYEN C.A Low-Cost Uniplanar Sampling Down-Converter with Internal Local Oscillator,Pulse Generator,and IF Amplifier[J].IEEE Trans on Microwave Theory and Techniques,2001,49(2):390-392.