VHDL中配置语句的基本用法

2015-01-17罗宇岳淼傅饶

罗 宇 岳 淼 傅 饶

(西华师范大学计算机学院,四川 南充 637000)

VHDL中配置语句的基本用法

罗 宇 岳 淼 傅 饶

(西华师范大学计算机学院,四川 南充 637000)

在VHDL语言中,配置可以把特定的结构体关联到(或指定给)一个确定的实体。通常在VHDL工程中,配置语句可以为实体指定或配属一个结构体,让一个实体配置不同的结构体以使其具有不同的功能或比较不同结构体的仿真差别等。本文介绍了配置语句的基本格式,并通过例子讲解配置语句的基本用法。

VHDL;配置;实体;结构体

1 概述

目前,常用的HDL(硬件描述语言)主要有VHDL、Verilog HDL、System Verilog和System C。其中VHDL在EDA设计中应用相当普遍,也得到几乎所有主流EDA工具的支持。VHDL一个完整的、可综合的程序结构,一般包括库(library)、程序包(Package)、实体(entity)、结构体(structure)和配置(configuration)。

配置是把元件具体安装到实体的最基本设计单元。在综合或仿真中,可以利用配置语句为确定整个设计提供许多有用信息。例如,对以元件例化的层次方式构成的VHDL设计实体,就可以把配置语句的设置看成一个元件表,以配置语句指定在顶层设计中的某一元件与一特定结构体相衔接,或赋予特定属性。配置语句还能用于对元件端口连接进行重新安排等。

一般地,配置语句的用法有默认配置法、元件配置法和实体-结构体对配置法三种。

2 默认配置法

默认配置是一种最简单形式的显式配置,不含任何块语句和元件的模块用这种配置,默认配置指定配置实体的配置名和为实体指定的结构体。其一般格式如下:

CONFIGURATION配置名OF实体名IS

配置说明

END配置名;

其中,一种最简单的缺省配置格式如下:

CONFIGURATION配置名OF实体名IS

FOR选配结构体名

END FOR;

END配置名;

如前所述,每个实体可以拥有多个结构体,而每个结构体的地位是平行的,在这种情况下,可以用默认配置方式为实体指定一个结构体。

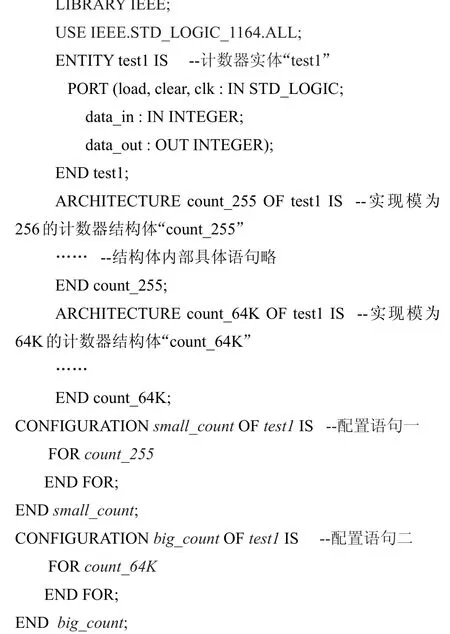

例1.为一个计数器(实体名为“test1”)建立两个配置,分别把结构体“count_255”和“count_64K”指定给计数器“test1”。

上述两个配置语句为实体指定了两个结构体,其中配置语句一的配置名为“small_count”,指定的结构体为count_ 255,即此配置语句实现实体的模为256的计数功能;配置语句二的配置名为“big_count”,指定的结构体为count_64K,即此配置语句实现实体的模为64K的计数功能。

3 元件配置法

在VHDL设计中,通常会采用自顶向下的层次设计方法。一般而言,高层电路会调用低层电路或元件。我们可以利用配置语句,通过对被调元件指定一定功能的结构体,从而使高层电路完成相应的功能目标。由于被调用元件可以指定不同的结构体,相应地,高层电路也能完成不同的功能。运用元件配置法,需定义并配置好低层元件。

元件配置的格式如下:

CONFIGURATION配置名OF高层电路实体名IS

FOR高层实体的结构体名

FOR例化名:低层元件名USE CONFIGURATION库名.低层元件配置名;

END FOR;

……

FOR例化名:低层元件名USE CONFIGURATION库名.低层元件配置名;

END FOR;

END配置名;

一般地,库名为WORK库。

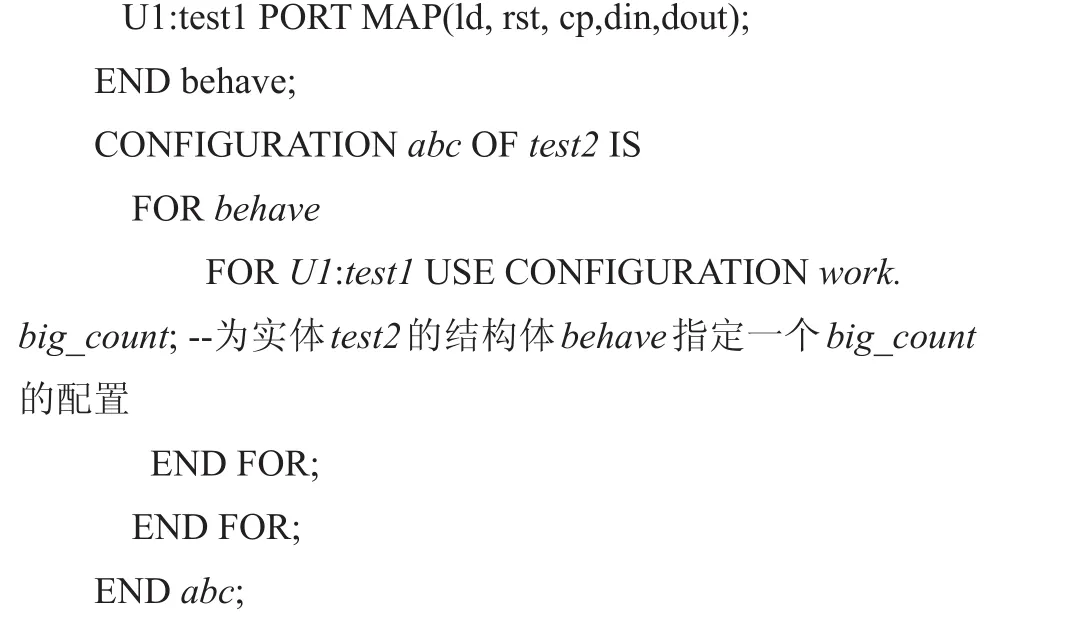

例2.创建一个电路,要求实现模为64K的计数功能。

(1)先创建低层电路,并进行配置,如例1所示。

(2)创建一个高层(顶层)电路,并进行配置,代码如下:

如果我们想实现模为256的计数器,只需要将work. big_count改为work.small_count即可。

4 实体-结构体对配置法

此方法与元件配置法有些类似,只是实体-结构体对配置法是直接为高层电路调用的低层元件指定具体结构体。其使用格式如下所示:

CONFIGURATION配置名OF高层电路实体名IS

2007—2017年世界纤维板进口额排名前5位的国家包括美国、英国、德国、法国、意大利、荷兰、波兰、俄罗斯和日本,2007年依次为美国、德国、英国、法国和荷兰,2017年为美国、德国、意大利、英国和波兰。美国进口额始终位列第1,其世界占比存在波动,但总体变化不显著,2007年为21%,2017年为14%;进口额第2位轮流由英国和法国占据,且两者差距不大;期间分别排名第3至第5位的国家与英法两国的差距也很小。

FOR高层实体的结构体名

FOR例化名:低层元件实体名USE ENTITY库名.低层元件实体名(结构体名);

END FOR;

……

FOR例化名:低层元件实体名USE ENTITY库名.低层元件实体名(结构体名);

END FOR;

END FOR;

END配置名;

同样地,库名一般为WORK库。

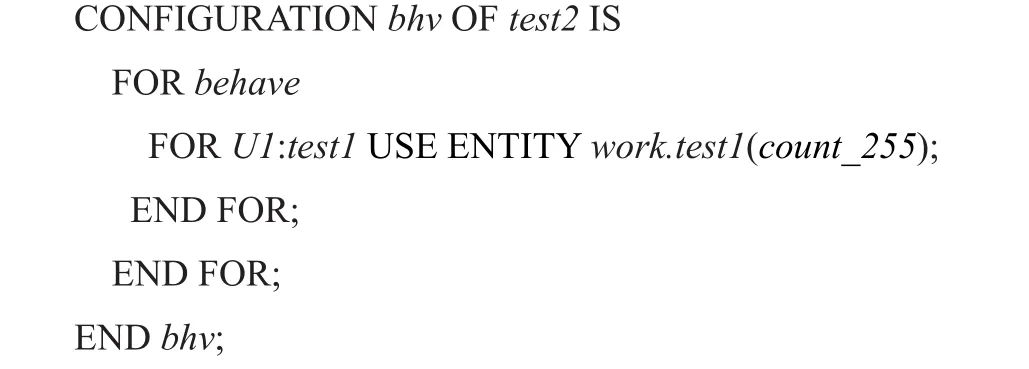

例3.创建一个电路,要求实现模为256的计数功能。

(1)先创建低层电路,并进行配置,如例1所示。

(2)创建一个高层(顶层)电路(代码与例2配置语句之前代码相同),且配置代码如下:

在上述配置语句中,将高层实体test2的结构体behave指定为低层实体test1的结构体count_255的配置,从而实现了模为256的计数器。很明显,只要将上述语句中的“work. test1(count_255)”改为“work.test1(count_64K)”即可实现模为64K的计数器。

5 结语

配置主要为高层(顶层)设计实体指定结构体,或为参与例化的元件实体指定所希望的结构体,以层次方式来对元件例化作结构配置。实现的方法简单、实用和高效,在运用以上三种方法时,需要注意其用法与使用场合,并搞清高层实体与低层实体及结构体之间的关系。

[1]潘松,黄继业.EDA技术实用教程(第三版)[M].北京:科学出版社,2006.

[2]邹道胜,朱如琪.CPLD/FPGA与ASIC设计实践教程(第二版) [M].北京:科学出版社,2010.

[3]徐志军,王金明,尹廷辉.EDA技术与VHDL设计[M].北京:电子工业出版社,2009.

[4]江国强.EDA技术与应用[M].北京:电子工业出版社,2010.

Basic Usage of Configuration Statements in VHDL

Luo Yu Yue Miao Fu Rao

(West China Normal University,Nanchong 637000,Sichuan)

In the VHDL language,a configuration can be associated with a specific structure to a certain entity.Usually in the VHDL project,the configuration statements can be specified or attached to a structure,and it can let an entity configure different structures for different functions or simulations.This paper introduces the basic form of the configuration statements and the basic usage of the configuration statements by example.

VHDL;configuration;entity;structure

TN402

A

1008-6609(2015)10-0077-02

罗宇,男,重庆市人,硕士,讲师,研究方向:电子信息处理。