基于CY7C68013A与FPGA的卫星数据采集系统设计

2015-01-04纪元法孙希延王海辉

黄 桂,纪元法,孙希延,王海辉

(桂林电子科技大学信息与通信学院,广西桂林 541004)

基于CY7C68013A与FPGA的卫星数据采集系统设计

黄 桂,纪元法,孙希延,王海辉

(桂林电子科技大学信息与通信学院,广西桂林 541004)

为了实现高速数据采集,保证数据的可靠性和完整性,采用CY7C68013A和FPGA组成的硬件平台,由上位机软件利用两线程乒乓操作的方式设计了一种卫星数据采集系统,并对卫星信号进行了实时数据采集。实验结果表明,该卫星数据采集系统的采集速率能达到38 MB/s,数据传输稳定可靠,解决了采集过程中数据丢失的问题。

CY7C68013A;FPGA;乒乓操作;数据采集

PCI接口、串行接口、并行接口等是外设与PC机通信的传统方式,它们一般体积较大、型号各异,不能满足大量数据高速实时传输的要求[1]。USB接口支持热拔插和多个外设的连接,设置灵活,传输速率高达480 Mbit/s。

在卫星导航设备研发中,需要实时采集卫星数据,并对这些数据进行仿真分析,根据分析结果验证接收机或下变频部分是否正确。大量的卫星数据经过下变频后仍然超过了串口传输的最大速率,导致串口传输出现数据丢失现象[2]。为了实现高速传输,保证数据的可靠性和完整性,利用CY7C68013A和FPGA设计了一种高速实时卫星数据采集系统,解决了一般串口采集中速率低且容易丢失数据的问题。

1 系统硬件设计

本设计硬件结构包括射频前端、FPGA主控端、USB接口电路,如图1所示[3]。天线接收GPS/BD信号,经过下变频、放大和模数转换后得到数字中频信号;该中频信号通过引脚引入FPGA的FIFO内, FPGA通过对USB数据传输控制,将FIFO中的数据传入USB端点,再由USB接口电路按照通信协议将端点的数据传到PC中存储。

图1 硬件结构Fig.1 Hardware architecture

1.1射频前端

射频前端采用RX3007芯片,可同时接收BD、GPS L1、Galileo E1中任意2个导航频点信号。RX3007芯片集成了低噪声放大器、中频带通滤波器、自动增益控制放大器、模数转换器、压控振荡器等,通道线性好,抗阻塞性能强,可应用于具有导航功能的移动终端集成电路[4]。

卫星信号经射频前端产生4.092 MHz的数字中频信号,并以SGN和MGN 2 bit信号输出。

1.2 FPGA主控端

FPGA主控端负责将卫星数据存储到内部FIFO中,并控制USB的读写时序,完成数据传输。本设计采用Altera公司的CycloneII系列EP2C70F672C8N芯片,该芯片包含68 416个逻辑单元,250个M4KS,并且提供422个I/O接口。

为了保证数据不丢失,在FPGA内部构建了一个65 536×8 bit的FIFO存储器,不需要额外添加缓存器,避免了复杂的电路设计。

1.3 USB接口电路

本设计USB接口电路采用CY7C68013A芯片,它是EZ-USB FX2类型中一款低功耗设备,其内部包含串行接口引擎、8051微控制器、USB2.0收发器、I2C总线、地址总线、数据总线、16 k B的软配置RAM、4个集成FIFO存储器和1个可编程的串行接口[5]。该系列芯片的优势在于包含一种称为“量子FIFO”的特殊架构,如图2所示。量子FIFO使芯片接口与外部逻辑能够共用FIFO,不需要微控制器干预传输过程,但它能通过访问内存或者FIFO的方式访问端点数据[6]。

图2 量子FIFO架构Fig.2 Quantum FIFO architecture

CY7C68013A与外设有3种接口方式:Porst、GPIF和Slave FIFO。Ports是最基本的数据传输方式,传输速率低,并且需要CPU的参与;GPIF能够通过设计读写时序主动读写8/16位接口的控制器、存储器以及总线;Slave FIFO是一种由外部主控器控制USB芯片读写时序的从机方式,CPU不干预传输过程。本设计选择Slave FIFO方式,数据传输过程如图3所示。

图3 数据传输过程Fig.3 Data transmission

CY7C68013 A内置7个端点缓冲区,3个固定为64 Byte,其余4个可以进行配置。EP0配置为控制传输端点,它的OUT和IN类型具有相同的内存地址;端点1可以采用除控制传输之外的任何一种传输方式。EP0、EP1IN、EP1OUT只能由固件访问; EP2、EP4、EP6、EP8端点能够在不需要固件干预的情况下实现与片外设备的高速传输[7],其中,EP4、EP8只能配置为512 Byte,而EP2、EP6可以配置为512 Byte或1024 Byte,并且可以设置为2、3、4倍缓冲。

1.4通信电路

本设计将CY7C68013A设置为从机,FPGA设置为主机,由Verilog HDL语言编程从机的读写逻辑信号。FPGA与USB通信电路如图4所示。

Slave FIFO接口IFCLK有2种类型:1)由芯片自带时钟电路提供,频率为30 MHz或48 MHz信号;2)由外部逻辑提供,频率为5~48 M Hz信号[8]。时钟类型由INCONFIG的时钟选择位IFCLKSRC进行选择。

图4 FPGA与USB通信电路Fig.4 FPGA and USB communication circuit

FD为FIFO的双向数据总线,其宽度由EPXP-KTLENH寄存器的字宽设置选择为8 bit或16 bit,本设计选择8 bit模式。

FIFOADR[1:0]=11选择端点6作为数据缓冲区,采用批量传输方式,每次传输512 Byte,并设置为4倍缓冲。

FLAGA、FLAGB、FLAGC、FLAGD引脚可由FLAGSAB、FLAGSCD设置标志端点的不同状态。本设计FLAGB检测端点6为写满状态,并且由FIFOPINPOLAR设置为低电平有效。

SLWR为IN端点数据的写选通信号,由FPGA控制,本设计将SLWR设置为高电平有效。

2 软件设计

2.1固件配置程序

固件配置程序实现对USB寄存器的初始配置和重枚举功能,并根据主机请求对芯片进行配置,然后按照具体的应用功能响应外部请求。

按照cypress的固件程序框架进行程序设计,可降低设计的复杂度,并缩短项目周期。在Keil软件系统中对固件程序进行编译,当需要调用固件库中的函数时,必须在设计中添加头文件EZUSB.H和EZREGS.H,同时将库文件Ezusb.lib包含在工程中,并在相应函数中编写程序代码[9]。

软件设计的初始化主要调用TD_Init函数,包括下列设置:

1)初始化CPU时钟为48 MHz。

2)选择接口时钟由外部逻辑提供,采用同步模式。

3)设置端点6为输入方向,采用批量传输方式,4倍缓冲结构,每次传输512 Byte。

4)配置外部端口,SLWR高电平有效,FLAGB低电平有效。

用户功能主要通过设备工作期间重复调用TD_ Poll函数,该函数主要执行查询端点状态任务。

void TD_Poll(void)

{

if(!(EP2468STAT&0x01))

{

SYNCDELAY;

}

}

设备工作期间需要不断监测USB是否挂起,并判断是否包含重新开始事件,由返回值决定是否运行唤醒函数TD_Resume[10]。固件配置如图5所示。

图5 固件配置Fig.5 Firmware configuration

2.2 FPGA控制程序

本设计USB读写信号控制由FPGA实现,FPGA生成一个异步FIFO,为了实时采集卫星数据, FIFO的写请求标志位wrreq必须置为1,读请求标志位rdreq由USB端点和FIFO空满状态决定。

在卫星数据写入FPGA的FIFO数据期间,FPGA监测FIFO的写满状态,若写满标志位wrfull由0变1,则FIFO处于写满状态,停止向FIFO传输数据。

在USB读取FPGA的FIFO数据期间,USB芯片自动检测端点是否写满,若写满,则写满标志位FLAGB自动置0,USB停止读取FIFO数据。同时, FPGA检测FIFO的读空状态,若检测到读空标志位rdempty由低电平跳变至高电平,则FIFO读空, USB停止读取FIFO数据。当且仅当USB的端点没有写满,FPGA的FIFO未被读空,FPGA才将USB的SLWR标志置高,否则,USB的SLWR标志置低,禁止向USB端点写入数据[11]。FPGA时序如图6所示。

图6 FPAG时序Fig.6 FPGA timing

2.3驱动程序

USB芯片的开发需要驱动程序进行主机和设备的连接。USB驱动完成2项任务:1)通过USB芯片内部增强型8051将固件程序导入内存;2)实现PC与外部设备之间的通信[12]。

本设计使用Cypress公司开发的通用驱动,因为USB设备驱动的安装是通过查找与芯片的VID、PID相符的芯片信息文件实现的,所以需要根据芯片的具体参数修改INF文件,以便连接芯片与驱动程序。

2.4应用程序

本设计通过上位机软件将数据保存到PC,在数据传输完毕再进行数据仿真分析。为了提高数据的接收和存储速度,采用了多线程操作,一个线程负责数据接收,另一个线程负责数据存储,并设计了乒乓存储操作方式,在数据接收和存储之间进行线程切换,提高系统的处理速度。

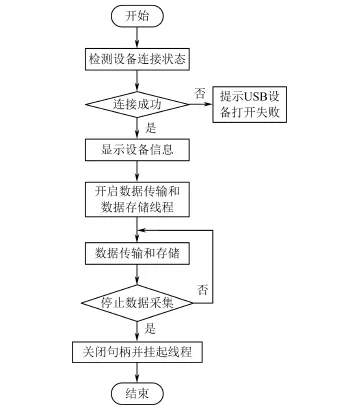

应用程序首先调用Creat File函数,若该函数返回值为真,则得到了该设备驱动程序的句柄,否则提示打开设备失败,重新尝试连接,确认连接设备后,开启数据传输和数据存储线程[13]。在数据传输线程中通过调用DeviceIoControl函数,设置输入输出数据缓冲区指针以及长度,执行数据传输操作。在数据存储线程中,调用WriteFile函数,在指定的PC文件中写入数据。整个过程需要不断监测数据采集是否终止,若终止,调用Close Handle函数释放内存,并调用Suspend Thread函数挂起线程。应用程序流程如图7所示。

3 应用验证

GPS/BD卫星信号经过下变频后为2 bit数据,通过补位得到8 bit的in_fpga_data数据,并存储在FPGA的FIFO中。采集的卫星数据格式如图8所示。

图7 应用程序流程Fig.7 Application process

图8 卫星数据格式Fig.8 Satellite data format

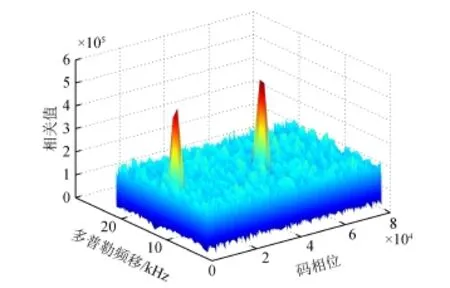

采用Matlab软件对GPS/BD卫星信号数据进行仿真分析,GPS 2号卫星和BD 10号卫星的捕获如图9、10所示。由GPS/BD星历预报软件可知,在采集信号时,GPS 2号和BD 10号卫星可见,图9、10中都出现了捕获峰值,捕获到GPS 2号卫星和BD 10号卫星,验证了采集数据的准确性。

以采集的GPS数据进行跟踪验证,对任意1 ms开始跟踪,跟踪效果如图11所示。从图11可看出,结果实现了连续跟踪,没有出现断点,验证了采集数据的完整性。

图9 GPS 2号卫星捕获图Fig.9 The captured figure of 2th GPS satellite

图10 BD 10号卫星捕获图Fig.10 The captured figure of 10th BD satellite

图11 GPS 2号卫星跟踪效果图Fig.11 The tracking figure of 2th GPS satellite

4 结束语

本设计采用Keil工具编写代码完成USB通信协议,利用Verilog语言进行数据传输控制,VC进行界面操作,Matlab作为仿真平台,实现了卫星数据的高速传输与存储,通过对采集数据进行仿真,实现卫星的捕获跟踪。实验结果表明,设计的卫星数据采集系统稳定性好,实时性高,完整性强,对卫星信号的采集和研究具有较高的应用价值。

[1] 薛园园,赵建领.USB应用开发宝典[M].北京:人民邮电出版社,2004:3-5.

[2] 翟伟,纪元法,孙希延,等.基于FPGA的高速串口采集系统设计[J].桂林电子科技大学学报,2013,33(4):275-278.

[3] 张建喜,旺峰,李金海,等.基于USB的GPS数据采集系统[J].电讯技术,2010,50(6):96-100.

[4] 胡辉,沈翔,纪兆云,等.基于USB2.0的GPS中频数据采集器研制[J].河南师范大学学报:自然科学版,2012, 40(3):55-59.

[5] 位小记,谢红,郭慧.基于FPGA和USB的高速数据传输平台的设计[J].应用科技,2010,37(11):53-56.

[6] 谭安菊,龚彬.USB2.0控制器CY7C68013与FPGA接口的Verilog HDL实现[J].电子工程师,2007,33(7): 52-55.

[7] 马俊涛,李振宇.Slave FIFO模式下CY7C68013和FPGA的数据通信[J].中国传媒大学学报:自然科学版, 2009,16(2):38-44.

[8] 仝瑞普.基于Slave FIFO模式USB数据传输系统设计与实现[D].南京:南京理工大学,2008:25.

[9] 方琳,谭全福.GPS L1信号中频数据采集系统设计[J].测控技术,2011,30(11):40-49.

[10] 范旭东,沈三民,刘建梁,等.基于LVDS和68013A的数据控制传输系统设计[J].计算机测量与控制,2014, 22(6):1950-1952.

[11] 乔立岩,吴江伟,徐红伟.数据采集卡USB2.0接口设计[J].电子测量技术,2010,33(1):57-60.

[12] 刘俊涛,原亮.WDM模式下USB设备驱动程序的设计[J].计算机工程与设计,2003,24(6):42-45.

[13] 吴磊,郭超平,申世涛.基于CY7C68013与FPGA的便携式数据采集系统[J].计算机应用,2012,32(增刊): 164-166.

编辑:曹寿平

Design of satellite data acquisition system based on CY7C68013A and FPGA

Huang Gui,Ji Yuanfa,Sun Xiyan,Wang Haihui

(School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin 541004,China)

In order to achieve high-speed data acquisition and ensure the reliability and integrity of the data,a hardware platform composed by CY7C68013 A and FPGA is applied,the mode of two threads ping-pong operation is used to design a satellite data acquisition system by PC software,and the system is used to capture real-time satellite signals.The experimental results show that the collection rate of the design can reach 38 MB/s,the transmission of data is reliable,and the problem of data loss in the acquisition process is solved.

CY7C68013A;FPGA;ping-pong operation;data acquisition

TP274+.2;TN927+.2

:A

:1673-808X(2015)04-0275-05

2015-03-16

国家自然科学基金(61162007,61271284,61362005);广西自然科学基金(2013GXNSFA019004);广西无线宽带通信与信号处理重点实验室主任基金(GXKL0614102)

纪元法(1975―),男,山东莘县人,教授,博士,研究方向为信号处理、卫星导航。E-mail:jiyuanfa@163.com

黄桂,纪元法,孙希延,等.基于CY7C68013A与FPGA的卫星数据采集系统设计[J].桂林电子科技大学学报,2015,35(4):275-279.