基于SATA接口的安全存储控制

2014-12-23马建鹏姚智慧赵明亮

马建鹏,姚智慧,赵明亮

(中国航天科工集团二院706所,北京100854)

0 引 言

作为数据存储载体的存储设备,如何保证数据能够访问受控,使得存储设备即使在丢失、不受控等状态下,依然保证其存储数据不为非法用户获取,成为数据安全研究的重要内容之一。SATA (serial ATA)接口是当前主流的串行硬盘接口,具有传输速率高、可靠性高、连线简单等优势。然而由于SATA 协议实现复杂度高和安全技术硬件实现比较困难等原因,国内只有少数科研机构展开了基于SATA 接口的安全存储控制研究,且相关研究多是基于控制原语和数据的完全转发开展,其实现较为简单,不能自主完成对主机或硬盘的交互,难以快速对传输状态的变化及异常做出响应,可靠性较低。本文针对安全存储自主创新的需求,在深入研究SATA 协议和信息安全技术的基础上,设计实现了一种基于SATA 接口的安全存储控制系统。经过FPGA 上的测试,该系统能自主完成对主机和硬盘的交互,快速处理异常,准确提取信息,并实现数据加解密和身份认证等安全功能。

1 SATA协议体系结构

SATA 协议体系[1-3]采用典型层次结构,分为四层:物理层、链路层、传输层和应用层。物理层负责与电气相关的特性,主要完成差分信号和OOB信号的收发、上电复位及初始化、电源管理、速率协商、串并/并串转换和数据对齐等功能;链路层负责链路上帧的发送与接收,主要完成通过握手建立和释放链路、帧定界、CRC 校验与生成、冲突仲裁、流量控制、8b/10b编码与解码、加解扰等功能;传输层负责FIS相关的事务,主要完成FIS的产生与解析、差错处理和流量控制等功能;应用层负责各种命令的执行以及相关寄存器的访问。

2 系统设计

2.1 系统硬件平台

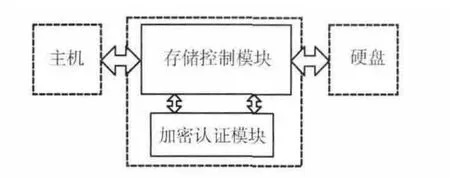

本 系 统 实 现 于Xilinx Virtex-6 系 列[4,5]FPGA。该 系 列FPGA具有先进的架构和极高的性能,是业界首批采用40纳米级工艺的FPGA。其可提供多达758,784 个逻辑单元,1200个I/O引脚,具备强大的时钟管理能力,能够满足本系统的资源需求。其中,Virtex-6中的高速串行收发器RocketIO GTX 包括8b/10b编解码器、极性控制器、FIFO、CRC模块、串化/解串器、接收/发送缓冲器、预加重模块、时钟生成器、时钟恢复器等模块,并具有高效的可配置性和与FPGA 可编程逻辑资源紧密结合的特点,可满足各种不断发展的高速串行协议的需要。通过调用RocketIO GTX 模块,正确的配置模块参数,可以实现系统存储控制模块中物理层功能模块的部分功能,从而简化系统设计。

2.2 系统总体结构

本系统桥接于主机硬盘之间,由存储控制模块和加密认证模块两部分组成[6],如图1 所示。传输链路建立后,流经系统的信息分为控制原语、加密帧和非加密帧,系统对不同的信息采用不同的处理方式。其中存储控制模块即时响应控制原语,同时触发内部状态机的跳转;对其它信息,经过串并转换、解码、数据提取甄别等操作,将识别出的非加密帧再经重新装帧、编码、并串转换等操作直接转发,对识别出的加密帧递交加密认证模块做加密处理。

图1 系统框架

2.3 系统详细设计

系统详细实现结构如图2所示。

2.3.1 存储控制模块

存储控制模块由物理层子模块、链路层子模块和路径选择子模块三部分构成。其中物理层子模块和链路层子模块分为主机端物理层子模块和链路层子模块,以及设备端物理层子模块和链路层子模块,分别用于完成对硬盘和主机的交互,实现协议物理层和链路层中规定功能;路径选择子模块完成对链路层子模块提取数据的甄别,决定数据是否加密,同时负责数据缓存和流量控制信号的生成。

(1)物理层子模块

主机端物理层子模块和设备端物理层子模块在功能与实现上基本相同。本系统主要通过完成Xilinx GTX IP核的配置和OOB控制器的设计2个部分的工作来实现物理层的相关功能[7]。

通过使用ISE软件提供的Core Generator工具配置Xi-

图2 系统结构

linx Virtex-6FPGA 内嵌的硬核GTX 的参数,使其正确完成高速串行比特的发射和接收、OOB 信号检测、时钟数据恢复、时钟补偿、预加重、去加重、串并/并串转换和极性检测等功能;同时基于Xilinx提供的数字时钟管理器实现了时钟输出和时钟倍频;并通过FPGA 的动态配置端口实现GTX 模块属性的配置。配置如图3所示。

图3 GTX 模块配置

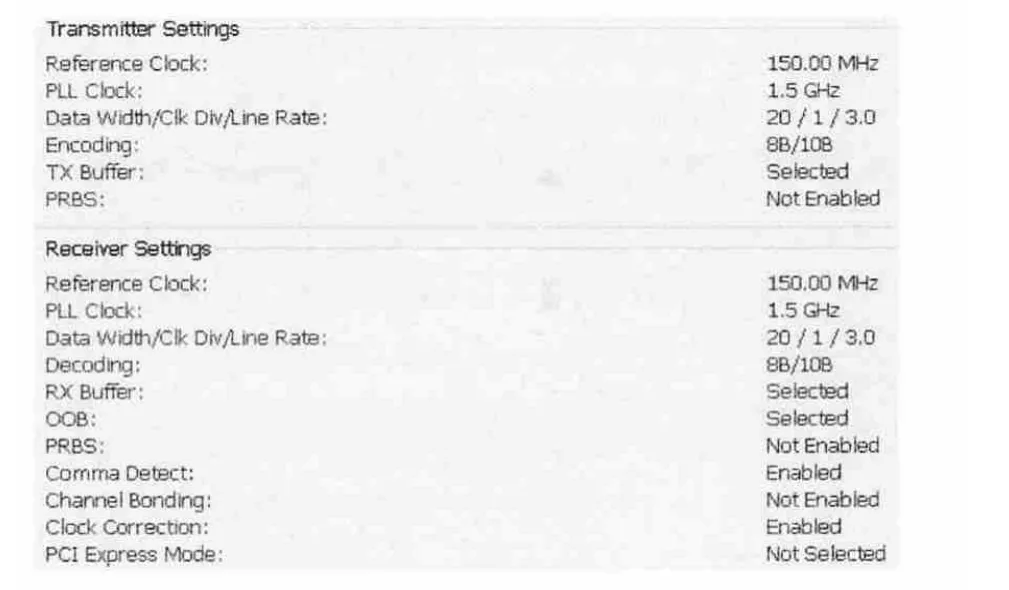

OOB (out of band)信 号 是 一 种 与 正 常 数 据 信 号 峰 峰值不同的差分信号,主要用于物理层链路的初始化,由数据和空闲两部分组成,并根据空闲时间的不同分为COMINIT、COMRESET 和COMWAKE 这3 种 类 型。OOB 控制器通过控制OOB信号的发送接收,完成如图4所示链路初始化过程,来实现物理层的上电初始化功能。

(2)链路层子模块

主机端链路层子模块和设备端链路层子模块仅在帧发送冲突时的处理上有差异,其它实现相同。因为链路层子模块的实现较为复杂,本系统将其功能实现部分与控制部分分开实现,简化设计。

图4 物理层上电初始化

链路层子模块的功能主要分为控制原语的收发、CRC校验和扰码生成三部分。其中控制原语是用来控制和维持串行链路数据传输状态的一系列信息原语,是由4个字节组成的链路层信息字,包括用于帧定界的SOF和EOF、流量控制的HOLD 和HOLDA、接收反馈的R_OK 和R_ERR 等18种原语。CRC 即循环冗余校验,是一种检错能力强、计算开销小、易于编码实现的校验算法。在链路层子模块中,通过采用生成多项式G (X)=X32+X26+X23+X22+X16+X12+X11+X10+X8+X7+X5+X4+X2+X+1,对信息帧中的起始原语SOF 和结束原语EOF 之间所有的有效数据进行串行CRC 校验,来检测信息的传输错误。扰码是在8b/10b编码基础上,通过使用线性反馈移位寄存器来实现扰码生成多项式G (X)=X16+X15+X13+X4+1,进一步调整连续的1或0信号,最大程度地避免连续信号在传输过程中所受到的干扰。链路层子模块通过原语的解析、CRC检测和解扰,以及原语的生成、CRC 生成和加扰等过程,实现链路信息的接收和发送。

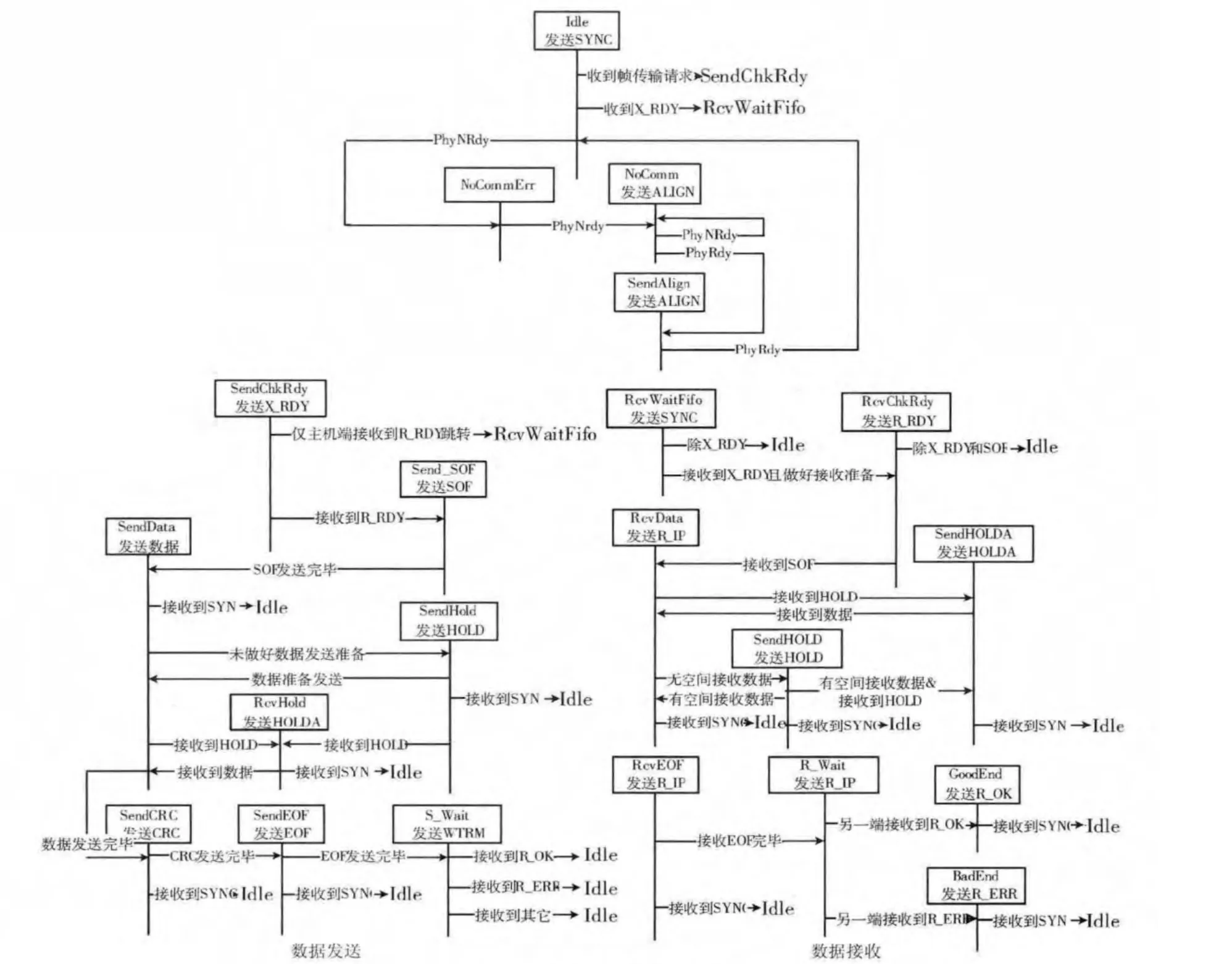

图5 链路层状态迁移

链路层子模块使用状态机来控制其功能实现,使链路层子模块能够正确有序完成一帧数据从SOF 原语、数据、CRC 到EOF 原语的发送与接收,正确完成对数据部分CRC校验和数据加解扰,以及流量控制实现等。其根据接收信息以及路径选择子模块的反馈信息来控制发送与接收时序,并生成差错管理相关的控制信号,来实现对链路状态的控制。链路状态机的状态迁移如图5所示。

(3)路径选择子模块

路径选择子模块处理的数据结构在协议中称为帧信息结构 (frame information structure,FIS),是协议链路层中帧结构去除帧头、帧尾以及流量控制原语后的信息。该数据结构负责阴影寄存器 (shadow register)内容、ATA 命令、数据传输的建立信息、数据、自测试启动指令和固定FIS种类值等信息的传输。路径选择子模块通过解析FIS头部的类型 (type)字段,甄别FIS种类,同时界定FIS中数据起始位置;而后根据主机到硬盘的Register FIS中的命令(command)字段判断是否加密。若需加密,则寄存其后Data FIS头部 (head),并将FIS中数据部分送入加密认证模块,加密完成后将数据与头部拼接,送至链路层子模块处理;若无需加密,则直接传送链路层子模块。同时,在FIFO 中缓存FIS数据,并生成流量控制信号,完成通路上的流量控制。

2.3.2 加密认证模块

加密认证模块由加密子模块、身份认证子模块和用户UKey三部分构成。其中加密认证子模块负责加密数据格式的转换和AES 256 算法的实现;身份认证子模块和用户UKey共同完成用户的身份认证功能。

(1)加密子模块

AES算法,是一种使用迭代型分组密码的对称加密算法,其分组长度和密钥长度均可在128位、192位和256位中作选择,如图6所示是本系统所使用的128位分组长度、256位密钥AES 算法加解密过程示意图。256 位密钥的AES算法使用14轮迭代运算,其中前13轮迭代完全相同,依次经过字节替换 (substitute bytes)、行移位变换 (shift rows)、列混合变换(mix columns)和轮密钥加(add round keys)4 个步骤,而最后一轮迭代则跳过列混合变换。其加密过程是基于4X4的字节矩阵运作的。其中每一轮迭代使用的子密钥均是原始密钥通过Key Expansion密钥扩展算法与字节矩阵共同生成;字节替换是使用非线性的替换函数,通过查找表的方式将各个字节替换;行移位变换将矩阵中的各行进行循环移位;列混合变换则通过线性转换混合矩阵中各个直行。在本系统的加密算法实现中,对密钥扩展运算做出优化:对运算出的各轮次密钥做缓存,此后使用不再运算,直接查找;同时,将算法的迭代过程分为14段,进行14级流水操作[8]。

加密子模块处理的原始数据,是经过8b/10b解码和数据解扰的加密FIS数据部分,也是无加密时最终存储在硬盘上的数据。加密子模块在实现加密算法前,使用输入缓存和输出缓存,完成存储控制模块中的32位位宽数据,与加密算法中的128位位宽数据,2种不同位宽数据格式的转换;同时,使用2个缓存完成由于加解密延迟所产生的流量控制。

图6 AES算法加解密流程

(2)身份认证子模块和用户UKey

身份认证子模块和用户UKey共同完成基于非对称密钥体制的双向身份认证。

非对称密钥加密是指对信息的加密和解密使用不同密钥的加密过程,其由一个公开的公钥和一个私有的私钥构成一对密钥,且互为唯一解开对方加密数据的密钥。在加密认证模块中,用户UKey拥有自己的私钥Kd1和身份认证子模块的公钥Ke2,模块拥有自己的私钥kd2 和用户UKey的公钥Ke1,且Kd1、Ke1、Kd2、Ke2 均不公开。用户UKey对模块进行认证时,首先用户UKey生成一串随机数X,并用自己的私钥Kd1 对数据加密DKd1 (X),然后将密文发送给模块,模块用用户UKey的公钥Ke1解密密文EKe1 (DKd1 (X)),再用自己的私钥Kd2 进行加密DKd2 (Eke1 (DKd1 (X))),并返回给用户UKey,最后用户UKey用模块的公钥Ke2 解密Eke2 (DKd2 (Eke1(DKd1 (X)))),然后与最初生成的随机数X 进行对比,如果Eke2 (DKd2 (Eke1 (DKd1 (X))))=X,则说明模块身份正确,否则不正确。同样模块也对用户UKey进行相同的认证过程[9]。其中非对称加密算法的实现,使用第三方提供的芯片完成。

加密子模块的密钥存储于用户UKey的ROM 中。当身份认证子模块和用户UKey成功完成上述认证过程后,用户UKey将自己私钥Kd1加密过的密钥传输给身份认证子模块,身份认证子模块将用户UKey公钥Ke1解密后的密钥传输给加密子模块,完成密钥的传输。至此,数据通路连通,加密子模块激活。

3 仿真与验证

本系统经过模块级和系统级仿真,以及Xilinx ML623开发板的板级验证。其中模块与系统级仿真使用Mentor公司开发的主机行为模型,及实验室自主研发的硬盘行为模型构成的仿真环境,并在Synopsys公司的VCS软件中进行了功能仿真;测试环境由搭载Virtex-6 FPGA 芯片的ML623开发板,使用SATA 线缆与ML623开发板相连的SATA 接口硬盘与计算机A,以及使用JTAG 线缆与ML623开发板相连的计算机B构成,计算机B上ISE 软件通过JTAG 下载线将生成的BIT 文件下载至FPGA 中,辅助Xilinx推出的用于FPGA 产品的Chipscope在线逻辑分析仪工具以及SATA 协议分析仪,完成系统的板级验证。

如图7所示为常用DMA 加密命令,WRITE DMA (用于主机写入指定扇区数据,加密命令)命令的系统仿真。

图7 加密命令系统仿真

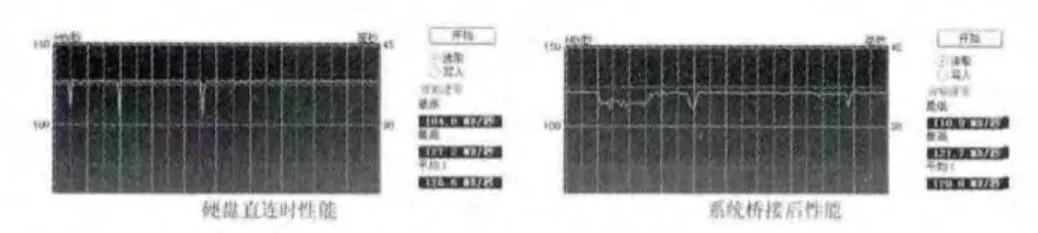

HDTune软件对系统进行的性能测试结果如图8所示。

图8 系统性能对比

4 结束语

本文在深入分析研究SATA 协议和存储安全控制技术的基础上,提出并实现了SATA 接口存储设备的安全控制技术设计,并通过系统仿真,以及基于ML623 开发板和virtex-6FPGA 芯片的半实物验证,详尽的测试和验证了存储控制、用户身份认证和数据加解密等功能,使得存储安全控制技术设计在确保主机和硬盘正常进行存储数据加密、非存储数据正常交互的同时,降低其对主机与存储设备间数据传输带宽的影响,提高SATA接口存储安全控制技术的可用性。

[1]ANSI INCITS 397-2005,AT attachment with packet interface-7volume 1 [S].

[2]ANSI INCITS 397-2005,AT attachment with packet interface-7volume 2 [S].

[3]ANSI INCITS 397-2005,AT attachment with packet interface-7volume 3 [S].

[4]Xilinx,inc.Virtex-6family overview [EB/OL]. [2012-01-19].http://www.xilinx.com/support/documentation/data_sheets/ds150.pdf.

[5]Xilinx,inc.Virtex-6packaging and pinout specification [EB/OL].[2011-11-23].http://www.xilinx.com/support/documentation/user_guides/ug365.pdf.

[6]LONG Yu.Design of SATA 2.0interface hard disk encryption and decryption chip data path and implementation on FPGA[D].Chengdu:University of Electronic Science and Technology of China,2009 (in Chinese).[龙羽.SATA 2.0硬盘加解密接口芯片数据通路的设计与FPGA 实现 [D].成都:电子科技大学,2009.]

[7]LIU Yang.Physical layer design and system debugging of SATA II interface encryption and decryption chip [D].Chengdu:University of Electronic Science and Technology of China,2009(in Chinese).[刘洋.SATA II加解密接口芯片的物理层设计与系统调试 [D].成都:电子科技大学,2009.]

[8]FENG Zhixing.Research and hardware design of AES in mobile memory encryption system [D].Shanghai:Shanghai Jiao Tong University,2009 (in Chinese). [冯志兴.AES算法在移动存储加密系统中的硬件设计 [D].上海:上海交通大学,2009.]

[9]Douglas R Stinson.Cryptography theory and practice [M].3rd ed.Beijing:Publishing House of Electronics Industry,2009 (in Chinese). [Douglas R Stinson.密码学原理与实践[M].3版:北京:电子工业出版社,2009.]

[10]LI Cui,REN Jie,YU Bin.Design and implementation of USB IP core with identity authentication function [J].Journal of Hefei University of Technology (Natural Science),2013,36 (5):580-585 (in Chinese).[李翠,任杰,郁滨.一种具有身份认证功能的USB IP核设计与实现 [J].合肥工业大学学报 (自然科学版),2013,36 (5):580-585.]