IEEE 1394事务层接口的设计与实现

2014-06-27张爱林

王 佩,徐 进,张爱林

(1.西安工程大学 电子信息学院,陕西 西安 710048;2.国网甘肃省电力公司检修公司,甘肃 兰州 737100)

0 引 言

IEEE1394协议是一种高速串行总线标准,该协议规定了事物层、链路层和物理层3个协议层[1].1394总线不仅节省空间,而且可替代多种巨大而昂贵的接口[2],因而应用范围越来越广,其技术也逐渐趋于完善.基于此,本文设计了一种IEEE1394事务层接口,目的是实现在PLB总线和139链路层之间进行数据传输.IEEE1394协议最初由Apple公司发布,后来经IEEE采纳并进行规范,成为IEEE1394-1995标准,目前在工业应用领域中IEEE1394总线技术应用在航天领域、航空领域、工业测控领域以及军事领域中,传输速度己经达到了每秒几百兆以上[3].在民用领域中,IEEE1394技术主要集中应用在3个领域:家电行业、个人计算机行业和专业音视频行业[4].该技术最先在国外发展起来,市场上国外设计的1394总线产品较多,国内近几年才开始发展,技术还不够成熟.

目前在PLB总线和1394链路层之间进行数据传输的设计中,对于数据异常发送和接收的处理方面做的还不够完善.本文基于IEEE1394b协议[5]研究设计了一种事务层接口, 包括跨时钟域数据访问、数据位宽转换、寄存器状态控制等,对于数据异常的处理提出了一种解决方法,为1394总线事务层与链路层接口之间的数据传输提供了一种可行的设计方案,具有一定的实用价值.

1 事务层接口设计

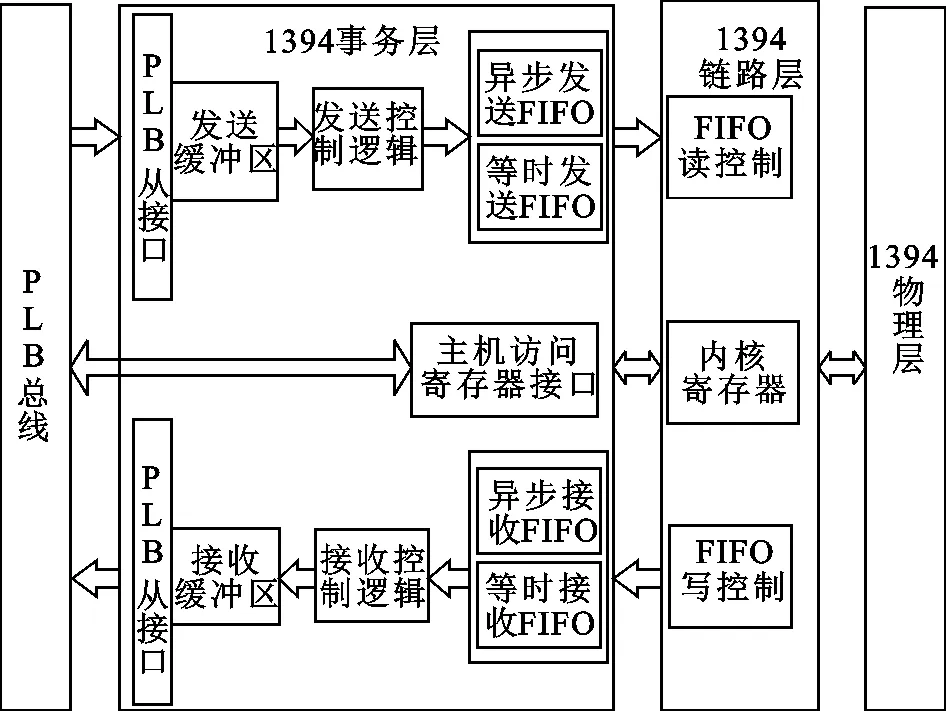

1.1 系统设计结构

1394事务层模块连接了PLB总线和1394链路层模块,主要完成1394总线事务层的数据发送和数据接收任务.由于事物层和链路层控制器采用的时钟不同,在传输过程中需要进行时序的缓冲,所以事务层逻辑向链路层提供4组通用FIFO存储器[6],分别用于异步数据包和等时数据包的收发缓存,实现了1394总线各种数据的收发操作.系统设计框图如图1所示.

图1 事物层接口设计

事物层接口模块包含PLB从接口、寄存器访问接口和4个FIFO存储器.这4个FIFO存储器分别是异步发送FIFO、等时发送FIFO、异步接收FIFO、等时接收FIFO.异步发送FIFO和等时发送FIFO是一类,统称为写FIFO;异步接收FIFO和等时接收FIFO是一类,统称为读FIFO.这4种FIFO支持的PLB事务包括128位或64位单拍读写操作和四字突发读写操作.

1.2 PLB从接口设计

PLB总线提供了一个高宽带、低延迟、高性能的处理器内部总线,该总线接口单元从PLB主设备独立的访问连接到PLB总线接口上的从设备.

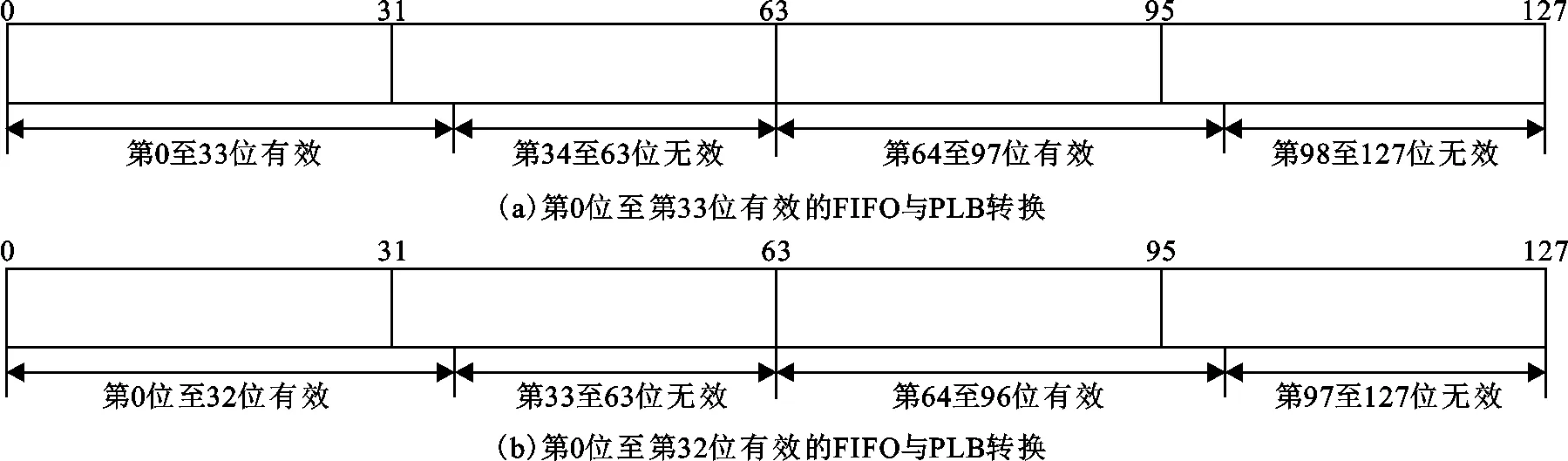

PLB总线从接口主要支持单拍读写和突发读写操作,可访问以下4个地址空间:异步发送数据缓冲区、等时发送数据缓冲区、异步接收数据缓冲区和等时接收数据缓冲区.每片地址空间首地址支持硬件参数化配置.只支持单拍访问寄存器地址空间,并且该空间首地址支持硬件参数化配置,数据访问宽度是32位.由于包格式的不同,FIFO接口可支持33或34位宽,而PLB总线从接口的数据位宽是128位,所以每次PLB操作将写入或读出2个FIFO深度的数据.异步发送FIFO和等时发送FIFO深度均为4k,异步接收FIFO和等时接收FIFO深度均为8k.FIFO与PLB之间的数据有效位转换关系如图2所示.

图2 FIFO与PLB的数据有效位转换

1.3 发送FIFO接口设计

通过异步发送FIFO接口,事务层发送逻辑可以控制链路层逻辑发送1394异步包.虽然只定义了一个FIFO接口,但是可以连接多个物理FIFO.在正常操作下,链路层逻辑会持续监测异步发送FIFO接口,便于发送数据,并在1394总线处于异步阶段时,请求物理层去仲裁1394总线.整个异步发送过程如下所述:

当主机控制逻辑准备好一个异步包时,事务层发送FIFO控制逻辑设置ATFPktRdy(发送包准备)信号有效,请求链路层逻辑开始从异步发送FIFO中读取、处理数据.当事物层逻辑检测到ATFInc(读取异步发送FIFO数据的指针增加控制信号)有效时,撤销ATFPktRdy信号.链路层逻辑使用ATFPktRdy信号作为处理数据的开始,使用ATFEmpty信号来判断FIFO中是否存在有效数据.

当链路层逻辑采样到ATFPktRdy有效时,会检查异步发送FIFO中的第一个数据是否有效,若有效,链路层向物理层发出请求,所有的数据包会使用优先级仲裁.链路层逻辑在发完请求之后,会等待来自物理层的应答.当链路层检测到物理层取消了当前请求,链路层逻辑会重新发起请求.直到接收到来自物理层的应答,链路层逻辑才会驱动物理层与链路层之间的数据传输接口处于保持状态,开始准备数据发送.

每当链路层逻辑处理完一个异步发送FIFO字时,ATFInc信号有效一个周期,即读FIFO数据指针加1,在下一个时钟周期,有效的新FIFO数据将被发送.链路层逻辑会持续检查ATFEmpty信号和FIFO中的包标识位.当ATFEmpty信号有效时会发生Underrun的情况,链路层逻辑将放弃物理层与链路层之间的接口控制权.当链路层逻辑检测到FIFO中的包标识位时,则认为当前这个字是发送状态字,上一个字是数据包的最后一个字,链路层逻辑随后会放弃物理层与链路层之间的接口控制权.当完成异步包的发送后,链路层逻辑会等待来自物理层的响应包.当收到响应包,链路层将异步数据发送完成的返回信号和异步包对应的状态字上报给事务层逻辑,便于事务层逻辑辨认该返回信息是属于之前的哪一个发送包.

通过等时发送FIFO接口,事务层发送逻辑可以控制1394链路层发送等时包.尽管这个接口被定义成一个FIFO接口类型,但是这个接口可以连接多个物理FIFO.1394总线上的等时操作都是由等时周期开始包来统一控制的.当事务层发送、链路层接收到一个等时周期开始包,链路层逻辑就开始将一个周期内规划好的等时包发送到1394总线上.整个等时发送过程如下所述:

当主机控制逻辑准备好一个等时包时,事务层发送FIFO控制逻辑设置ITFPktRdy(发送包准备)信号有效,请求链路层逻辑开始从等时发送FIFO中读取、处理数据.当事务层逻辑检测到ITFInc(读取等时发送FIFO数据的指针增加控制信号)有效时,撤销该信号.ITFEmpty信号用于判断在等时发送FIFO中是否存在数据.

当链路层逻辑检测到ITFPktRdy信号有效时,会从等时发送FIFO中取出第一个字检查数据的有效性,若有效,链路层会向物理层发起请求,然后等待来自物理层的应答.在发送等时包前,事务层需向等时发送FIFO中填入一个周期隔离字,用于标识每个等时周期待发数据包的界限.当链路层检测到物理层取消了当前的请求,链路层逻辑会重新发起请求.一旦检测到来自物理层的授权应答,链路层逻辑将驱动物理层与链路层之间的接口为保持状态,开始准备发送数据.

每当链路层逻辑处理完一个等时发送FIFO字时,链路层逻辑会驱动ITFInc有效一个周期,表明在下一个时钟周期读取的新FIFO数据有效.链路层逻辑持续检查ITFEmpty信号和FIFO包标志位.当ITFEmpty信号有效时会发生Underrun情况,链路层逻辑将放弃物理层与链路层之间的接口控制权.当链路层逻辑检测到FIFO中的包标识位时,则认为当前这个字是发送状态字,上一个字是数据包的最后一个字,链路层逻辑随后会放弃物理层与链路层之间的接口控制权.

当完成等时包的发送后,链路层逻辑会检查等时发送FIFO中下一个字是周期隔离字,还是当前等时周期待发送的下一个等时包.若是等时周期隔离字,表示在当前等时周期中不再需要发送等时包,即链路层已经处理完成当前的等时周期,反之表明当前等时周期内还需要继续发送等时包.

Underrun情况是指:在链路层逻辑从发送FIFO中取数的过程中,链路层逻辑的读取速率大于事务层逻辑的填写速率,即链路层逻辑还没有读取一个完整的包,发送FIFO中就已经没有数据了,致使1394总线上出现一个不完整的错误帧,最终导致总线效率降低.为防止此情况发生,本设计先将足够多的数据填入发送FIFO中,当链路层以一定的速率开始读取数据时,主机发送控制逻辑能够及时、连续提供发送数据,并避免发送FIFO空,产生错误帧.

发送FIFO每次只填写一帧待发数据,发送完成之后FIFO读写指针归零.当事物层逻辑、软件检测到发送FIFO发生Underrun、包头字数错误、包头事务代码错误时,链路层逻辑会产生中断信号,通知主机对发送FIFO进行flush操作,即产生一个系统时钟周期的高电平脉冲信号,结束异常发送过程,同时复位发送FIFO及其周围的逻辑,然后清除中断.在flush操作结束前,发送逻辑不会向1394总线上发送任何数据包.

存储在异步发送FIFO中的包与1394总线上传输的包格式不太一样.异步发送FIFO输出33位数据总线,32位宽的异步发送数据线,第33位为1用于标识异步发送FIFO包格式的开始和结束,即包的第一个字和最后一个字,包的其余字段此位为0.

存储在等时发送FIFO中的包与1394总线上传输的包格式不太一样.等时发送FIFO输出34位数据总线.32位宽的等时发送数据线,第33位为1用于标识等时发送FIFO包格式的开始和结束,即包的第一个字和最后一个字,包的其余字段此位为0.第34位是等时周期隔离字标识位,为1时,表示在当前等时周期中不再需要发送等时包,即链路层已经处理完成当前的等时周期;为0时,表明当前等时周期内还需要继续发送等时包.

1.4 接收FIFO接口设计

通过异步包接收FIFO接口,1394链路层IP可以将1394总线上接收到的异步包,写入到事务层的异步包接收FIFO中.通过等时包接收FIFO接口,1394链路层IP可以将1394总线上接收到的等时包,写入到事务层的等时包接收FIFO中.整个接收过程如下所述:

当链路层逻辑检测到物理层与链路层之间的接口有数据前缀时,接收逻辑就开始工作.首先会把接口的速度锁存住,然后把接收到的数据转换成32位数据.当接收逻辑收集到1394总线上的第一个32位数据时,会对内容进行解析.对于异步包,若其目标节点ID与链路层的节点ID寄存器内容相匹配,目标总线ID与链路层的总线ID寄存器内容相匹配,则将这帧数据传递给事物层接收逻辑.对于等时包,若其通过了等时接收通道检查,则数据包会被传递给事物层接收逻辑.当链路层把第一个32位数据写入接收FIFO时,需要把接收FIFO内的第32位置1,表明这是一个帧的开始数据.如果接收包是异步非广播包,链路层会向物理层发起立即请求,用于发送响应包.

在接收数据包的包头过程中,接收FIFO始终有空间的前提下,所有包头字将被写入接收FIFO中,若接收到包头不完整或包头CRC校验码错误的数据包以及发生了接收FIFO几乎满事件,则后续数据负载不会被写入接收FIFO中,同时放弃此次接收并对已写入接收FIFO的数据进行Backup操作.

在接收数据包数据负载过程中,每接收一个字就进行一次Update操作.若出现了接收FIFO几乎满状态,接收状态机就会停止向接收FIFO写入数据,之前被写入的数据负载不会被丢弃,所剩最后一个字节会被填入状态字.当接收FIFO满,链路层会丢弃正在接收的来自物理层的数据包,如果该数据包要求返回响应包,则事物层逻辑产生忙响应包输出给发送模块再发送至物理层.接收逻辑会对数据负载进行CRC校验,若出现校验码错误,数据仍写入接收FIFO中,但会产生相应的中断信号,通过中断状态寄存器向主机报告错误.

若接收到的数据负载实际长度大于包头中的数据长度,将在接收完包头数据长度的数据负载后认为下一个数据是CRC校验码,可能会产生校验码错误;若数据负载实际长度小于包头中的数据长度,将正常结束接收操作,主机可以通过比较包头数据长度与实际负载长度得知此情况.

Update操作指更新接收FIFO,即链路层逻辑需要表明前一个和当前接收到的字是有效的FIFO控制字,其中接收包头数据是整体更新一次,而数据负载和状态字都是每字更新一次.Backup操作指将接收FIFO的写指针指向最初开始接收这帧数据的位置,即抛弃接收到的数据.当链路层逻辑检测到接收数据包头存在CRC错误时,接收控制逻辑放弃之前已经写入接收FIFO的数据,并把接收指针归位.对于读FIFO,当出现Backup,所有未Update的数据将被放弃.

异步接收FIFO接收32位宽的异步数据线,在第33位填入包标志位,为1表示包的第一个字和最后一个字,包的其余字段此位填0.第34位置1表示该字是总线复位标识字或是自标识包.等时接收FIFO接收32位宽的等时数据线,向第33位填入等时周期开始包的标识字,通知事物层逻辑收到的等时包属于哪个等时周期,或者标识等时包的第一个和最后一个字.

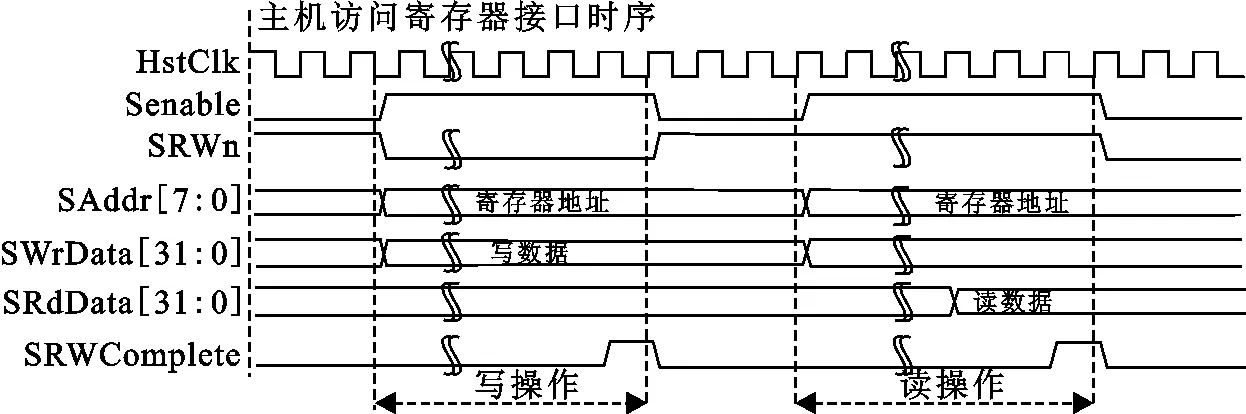

1.5 主机访问寄存器接口

主机通过这个接口访问链路层逻辑的寄存器.1394链路层模块寄存器分为DCR(设备配置)寄存器和PLB(处理器局部总线)寄存器.DCR寄存器主要是链路层内核寄存器,PLB寄存器主要是FIFO控制和状态寄存器.主机访问寄存器接口的时序是一个异步时序,即主机访问寄存器的时钟与寄存器内部使用的时钟完全异步.所以无论读、写操作,都会有一个操作完成的标识.对于读操作,只有检测到SRWComplete信号为高脉冲,才能安全的读取同步过来的数据,只有在上一次操作彻底完成的情况下,才能发起下一次读写操作.主机访问寄存器接口时序如3所示.

2 仿真验证

2.1 异步发送FIFO接口时序

事务层逻辑需要发送异步数据时,需要先将足够的数据填入异步发送FIFO中,才能够使能ATFPktRdy信号,当检测到ATFInc信号为高电平,撤销ATFPktRdy信号使能.每次ATFInc信号为高电平,即读数据指针增1时,在下一个时钟正跳变时,异步FIFO中待发送数据将被输出.

图3 主机访问寄存器接口时序图

2.2 等时发送FIFO接口时序

事务层需要发送等时数据时,需要先将足够的数据填入等时发送FIFO中,才能够使能ITFPktRdy,当检测到ITFInc为高电平,撤销ITFPktRdy信号使能.每次ITFInc信号为高电平,即读数据指针增1时,在下一个时钟正跳变时,等时FIFO中待发送数据将被输出.

2.3 异步接收FIFO接口时序

异步包的接收分为2个部分:包头的接收和包负载的接收.在包头的接收过程中,每个接收包头字没有立即被写入接收FIFO,只有在正确接收包头完成之后,才能通过Update信号真正使数据被写入FIFO.而在接收包负载的过程中,每个接收负载字会被立即写入接收FIFO中.一旦在接收的过程中,出现了Backup操作,则接收FIFO的写指针必须要能够回到接收当前帧的起始位置.

2.4 等时接收FIFO接口时序

等时包的接收分为2个部分:包头的接收和包负载的接收.在包头的接收过程中,每个接收包头字没有立即被写入接收FIFO,只有在正确接收包头完成之后,才能通过Update信号真正使数据被写入FIFO.而在接收包负载的过程中,每个接收负载字会被立即写入接收FIFO中.一旦在接收的过程中,出现了Backup操作,则接收FIFO的写指针必须要能够回到接收当前帧的起始位置.

3 结束语

文中设计的1394事物层接口不仅对数据位宽进行了有效转换,且采用FIFO存储器解决了链路层和事物层时钟异步的问题,并对事物层控制逻辑操作过程进行了详细设计提出了一种针对数据异常情况下的处理方法,通过对寄存器的设置不仅实现数据流的有效控制,并能获取当前的状态信息,实现事务层与链路层的数据通信,提高数据的传输效率.最后采用QuestaSim软件进行仿真验证,从仿真时序图中可以得出事物层接口基本实现了事物层模块正常发送和接收数据包的功能.

参考文献:

[1] 汪国有,何晓翔,王志勉.基于FPGA的IEEE1394链路层控制器的设计与实现[J].红外与激光工程,2004,33(5):553-556.

[2] 李肇庆,朱险峰.IEEE1394接口技术[M].北京:国防工业出版社,2004:7-12.

[3] 高旭光.基于IEEE1394总线的高速信息传输设备的设计[D].保定:河北大学,2010:4-9.

[4] 杨庆勇,刘方,张覃平,等.基于IEEE 1394接口的图像传输控制器设计[J].仪器仪表用户,2008,3(11):41-43.

[5] IEEE Std.1394bTM—2002,IEEE Standard for a High Performance Serial Bus-Amendment 2[S].New York:IEEE Computer Society,2002.

[6] 杨丽君,张盛兵,杨可,等.1394链路层控制器等时传输模式的设计[J].计算机测量与控制,2012,20(3):800-803.