一种高Q值高阶ΣΔ加速度计接口电路*

2014-12-10都文和盛大鹏

都文和 ,盛大鹏 ,王 婷

(1.齐齐哈尔大学 通信与电子工程学院,黑龙江 齐齐哈尔 161000;2.哈尔滨工业大学 航天学院,黑龙江 哈尔滨 150090)

0 引言

因为 Sigma-delta(Σ-Δ)MEMS微机械加速度计具有尺寸小、功耗低、可靠性高等特点,在国防军事领域和民用市场都得到了广泛的应用[1]。高性能的加速度计一般采用高品质因数(Q)的传感器结构,在真空环境下具有较低的机械热噪声,灵敏度也较高,然而高Q值的加速度计具有不稳定、响应时间长等特点。对低阶结构的高Q值加速计系统进行PID电学补偿能够提高系统的稳定性,但是在过采样率不高的情况下,低阶结构的高Q值加速度计接口电路性能往往受低频量化噪声限制,难以满足应用需求[2-3]。提高过采样率能够一定程度上降低基带内的量化噪声对系统性能的影响,然而这对运放的带宽提出了更高的要求,使得系统的功耗大大增加[4]。针对这一问题,本文设计了一种高阶结构的高Q值闭环Σ-Δ加速度计接口电路,大大降低了数字接口电路基带内的量化噪声。为了保证该高阶系统的稳定性,设计了一种前置补偿器电路来提高电学阻尼,完成了PCB板级的开关电容(SC)电路。测试结果表明,设计的闭环高阶加速度计不仅系统稳定,而且大大降低了基带内的量化噪声。

1 ΣΔ加速度计系统结构

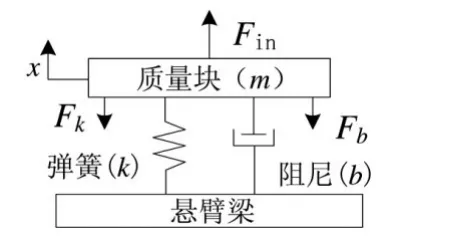

微机械加速度计由敏感质量块m借助于弹性元件附于固定支架上,其力学模型如图1所示。

图1 加速度计原理图

当外加力施加到质量块上时,质量块受到了弹性力与阻尼力,其幅值分别与质量块的位移、速度成正比,且与系统外力反向。由此可得加速度a(t)作为输入变量、质量相对壳体位移 x(t)作为输出变量的传递函数为:

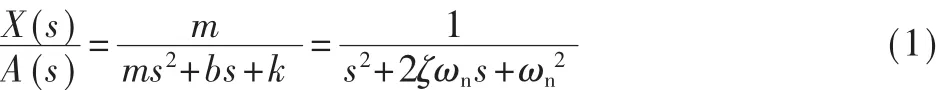

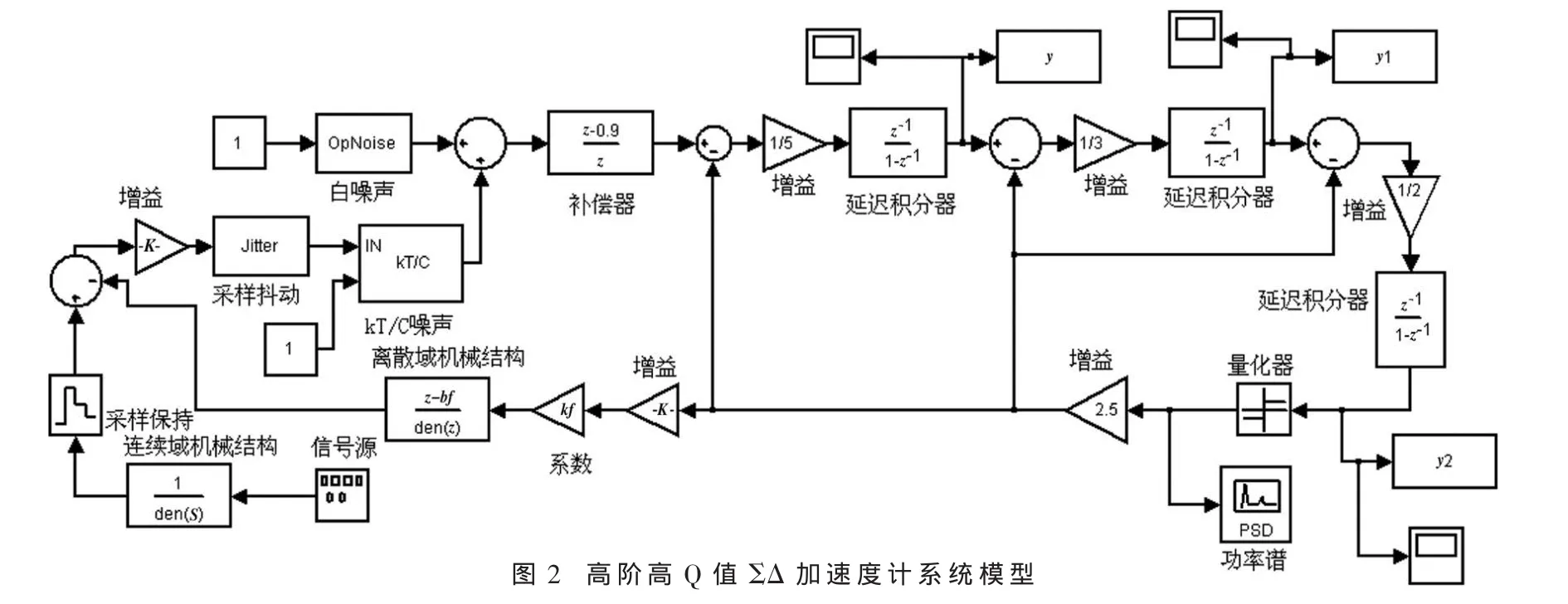

高Q值加速度计敏感结构处于欠阻尼状态,不加任何补偿的闭环二阶系统条件稳定[5]。在对高Q值二阶系统进行电学补偿以后,虽然系统稳定性提高,但也降低了系统的环路增益,使得系统对低频噪声的整形能力下降,影响输出信号的性能。因此可以在后级增加电学调制器,提高系统的环路增益,加强加速度计系统对噪声的整形能力。为使降低设计难度的同时获取较高的性能,选取三阶全反馈结构的电学调制器结构。基于该高Q值结构的ΣΔ加速度计系统结构模型图如图2所示,图中包含机械结构的连续时间模型、机械结构的离散时间模型、前级电荷电压转换线性因子Ka、前置补偿器、调制器、电压力转换因子Kg等模块,另外还包括运放噪声、开关噪声等噪声模块。高阶高Q值的加速度计系统类似于高阶的电学调制器,存在系统稳定性的问题,因此需要合理设计后级电路参数,以确保系统稳定。图3是图2中的五阶高Q值ΣΔ加速度计量化噪声传递函数QNTF的根轨迹曲线,可以看出该高阶系统是条件稳定的。当增加输入信号的幅度使得量化器的增益小于0.545时,QNTF的根轨迹进入单位圆外,系统变得不稳定,因此该高阶系统有一个输入信号范围。

图3 NTF根轨迹图

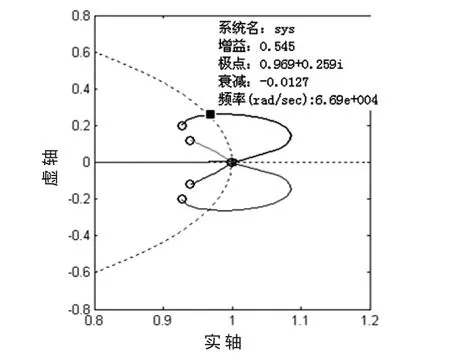

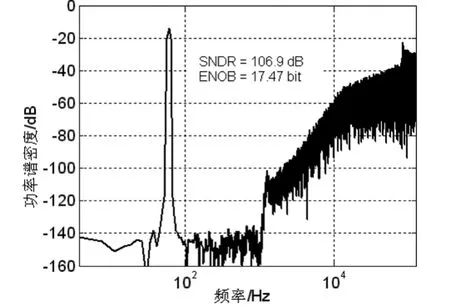

为了进一步验证系统的稳定性,在MATLAB的Simulink环境下对该系统进行建模并进行瞬态仿真。给该加速度计系统施加一个模拟的正弦加速度信号,系统采样频率为 250 kHz,输入信号幅度为-7.56 dBFS(1 g),频率为61.035 Hz,带宽为 1 kHz。各级积分器的输出统计图如图4所示,可以看出,系统在输入大信号时各级积分器输出摆幅较小,系统稳定。图5是其一位量化器输出的频谱图,仿真结果表明,该加速度计系统低频噪声较小,在 1 kHz带宽内信噪失真比约为107 dB,能够达到17 bit的有效精度。

图4 积分器输出柱状图

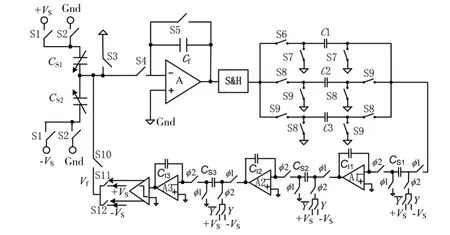

2 闭环电路设计

本文整个闭环电路原理图如图6所示,将机械结构部分等效成两个可变电容CS1和CS2。接口电路部分包括低噪声前级电荷放大器、后级采样和保持电路、前置相位补偿器电路、三阶调制器电路以及一位DAC电路。前级低噪声电荷放大器和采样保持电路借鉴参考文献[6]的设计原理,采用电容检测和电压反馈分时复用的方法来防止反馈信号和检测信号的互相干扰[7]。这里设计了一种无源相位补偿器电路进行结构的电学补偿[8]。

图5 行为级建模仿真结果

图6 五阶闭环ΣΔ加速度计接口电路原理图

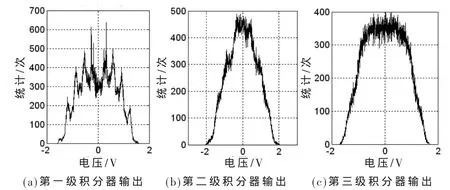

图6中如果选取电容 C2=C3=αC1,则相位补偿器的传递函数为:

其中,α表示补偿器的补偿深度,较大的α值能够给系统提供较大的相位裕度,提高稳定性,但同时也牺牲了一定的增益。对于高阶系统,前级增益的下降可以通过后级增益进行调整,因此系统的噪声整形能力得到保障。三级调制器电路的采样电容和反馈电容共用,电路结构简单,且不会增加热噪声和运放的负载。调制器输出控制一位DAC反馈的开关,决定反馈电压的极性。

3 电路测试验证和分析

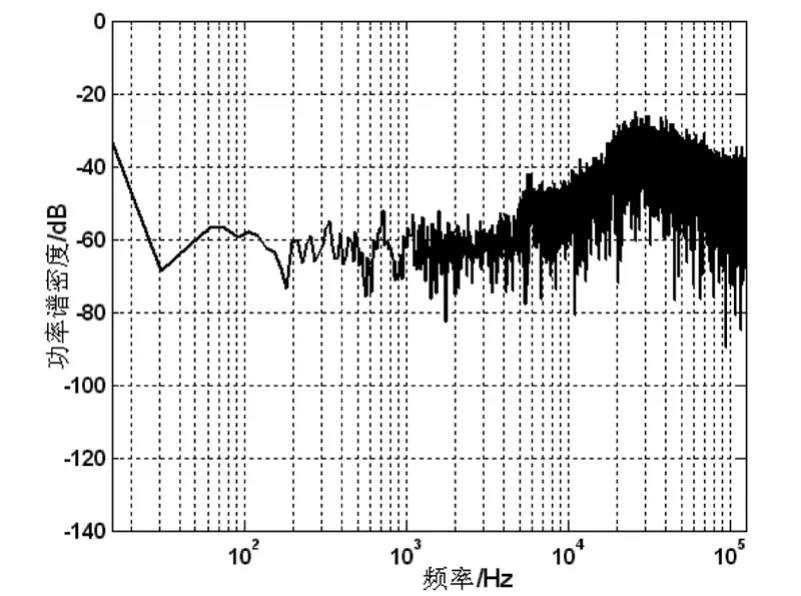

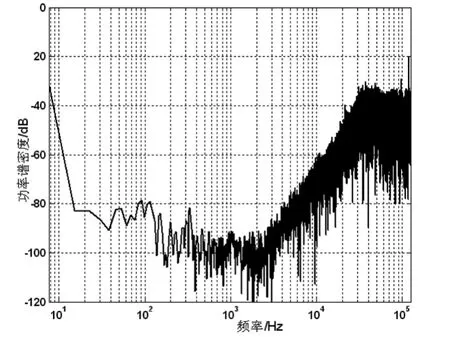

上述的设计思路和电路原理图已经通过软件进行了仿真和验证,然后设计PCB来进行实验验证。PCB检测电路是基于高精度低噪声运放OPA2209和模拟开关ADG1233进行实验设计。时钟部分由FPGA产生来控制模拟开关工作。采样得到的数字码流经过MATLAB程序进行处理,从频谱图中可以看出系统的噪声特性。为了对比高阶结构和低阶结构对低频噪声整形能力的不同,分别测试了基于结构本身的二阶闭环加速度计和基于三阶调制器结构的五阶闭环加速度计系统。两次测试的采样频率和采样点数一致,测试结果分别如图7和图8所示。

图7 二阶闭环加速度计PCB测试结果

图8 五阶闭环加速度计PCB测试结果

从图7的频谱图中可以看出,结构本身具有一定的噪声整形能力,但是由于结构本身的低频增益较低,系统阶数不高,对于量化噪声的整形能力有限。图8的测试结果显示,当采用高阶结构以后,低频带内的量化噪声得到大大的降低,系统的噪声整形能力得到很大的提高。系统灵敏度为1.25 V/g,低频等效加速度输入噪声约为63μg/Hz1/2。模拟开关的导通电阻和馈通效应、PCB测试板的寄生参数等都会恶化系统的整体性能。通过图7和图8测试结果的对比可以发现,设计的基于高Q值高阶结构的加速度计经过电学补偿以后系统稳定,工作正常,相对于二阶结构,其对传感器带内量化噪声的抑制能力大大提高。

4 结论

针对低阶高Q值加速度计系统较高的量化噪声问题提出了一种高阶高Q值ΣΔ电路。通过建模分析,验证了提出的带前置补偿器的高阶高Q值加速度计系统的稳定性,同时对该加速度计系统进行了电路设计和实验验证。测试结果表明,基于前置补偿器的高阶高Q值加速度计电路系统稳定,该高阶结构大大降低了传感器带内的量化噪声,提升了系统的性能。

[1]Lv Bingjun,Wang Pengfei,Wang Dongbo,et al.A highperformance closed-loop fourth-order sigma delta micromachined accelerometer[J].Key Engineering Materials,2012(503):134-138.

[2]徐伟鹤,林友玲,车录锋,等.一种圆片级硅三层键合的三明治加速度传感器[J].传感技术学报,2008,21(2):230-232.

[3]孙腾,车录锋,黎晓林,等.基于 PID反馈的高Q值加速度计闭环检测电路[J].传感器与微系统,2011,30(2):101-106.

[4]LIU X W,XU H L,YIN L,et al.A low noise sigma-delta microaccelerometer interface circuit[J].IEICE Electronics Express,2014,11(12):1-6.

[5]刘云涛.电容式SIGMA-DELTA微加速度计接口ASIC芯片研究[D].哈尔滨:哈尔滨工业大学,2010.

[6]吕炳均.高阶SIGMA DELTA微加速度计接口ASIC芯片研究[D].哈尔滨:哈尔滨工业大学,2013.

[7]戚玉婕,车录锋,孙腾,等.反馈补偿对高Q值加速度计动态性能的影响[J].半导体技术,2011,36(1):26-30.

[8]PETKOV V P,BOSER B E.A fourth-orderΣΔ interface for micromachined inertial sensors[J].IEEE Journal of Solid-State Circuits,2005,40(8):1602-1609.