高速ADC接口技术最新进展

2014-12-05钱宏文付俊爱陈珍海

钱宏文,付俊爱,陈珍海

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

当前集成电路行业进入超深亚微米和纳米(28 nm及以下)设计时代,电子系统内部不同芯片之间的互联问题越来越突出,以往许多被忽视的物理效应对信号完整性和设计可靠性的影响日益显著,己成为影响芯片功能和性能的关键因素。随着ADC采样速率和动态范围的不断提高,高速ADC数据输出端口的重要性日益突出。高速ADC所使用的输出接口类型种类繁多,从传统的TTL、CMOS数字逻辑接口到LVTTL、LVCMOS等优化的数字逻辑接口,再到差分串行LVDS、CML输出接口以及近几年采用的Serdes接口,各类输出接口的数据传输率也不断提高。

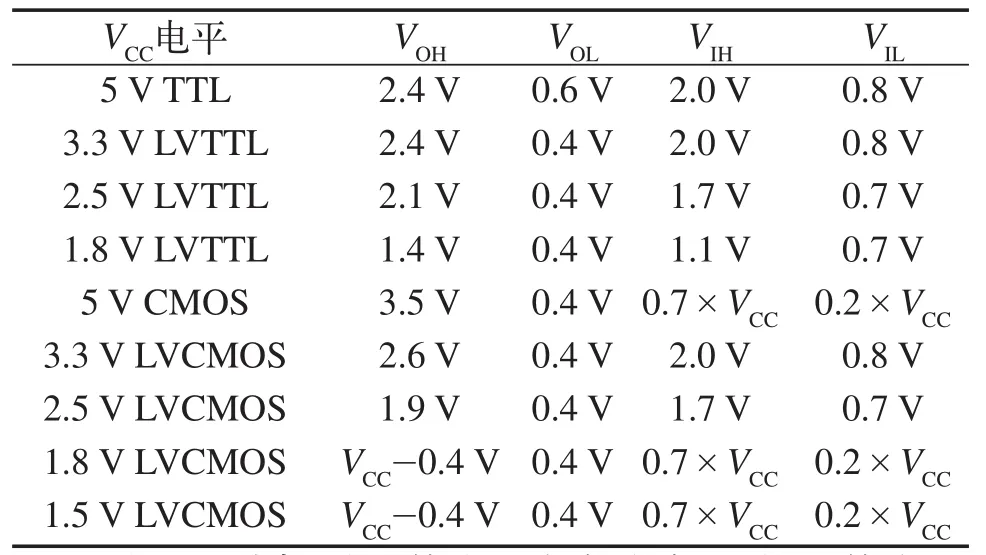

2 数字逻辑接口标准

高速ADC电路发展的早期,绝大多数ADC器件都采用TTL和CMOS数字逻辑标准。近几年随着数字处理系统电源电压的不断降低,产生了许多针对不同应用的低压、高速的数字逻辑标准,典型的标准是LVTTL和LVCMOS。它们的主要性能参数如表1所示。

表1 数字接口逻辑标准对比

对于芯片间需要的大量数据传输,传统的实现方式通常采用并行输出。然而由于并行传输在高频下时钟抖动和偏斜所带来的设计挑战,阻碍了并行传输频率的进一步提高。相比较而言,高速串行差分数据传输系统采用了源同步数据传输方式,所以高速串行差分数据传输系统更适合于现代信息系统的需要[1]。串行差分信号传输技术将两个信号耦合在一起,并确保这两个信号之间保持180°的理想相位偏移,使信号源电流和反馈电流方向正好相反。这样可以使得各对耦合差分信号有较大的抑制噪音能力,免受共模噪音影响。

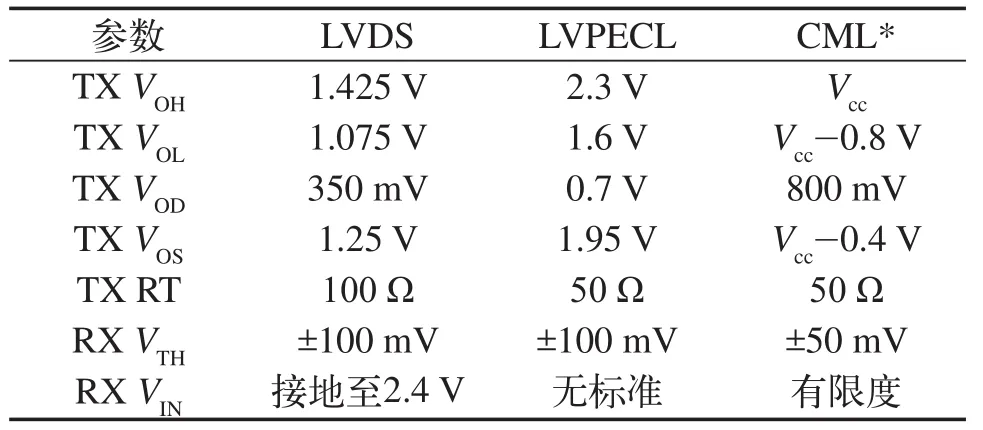

3 串行差分输出接口

目前国内外常用的串行接口形式主要有3种:LVPECL、LVDS和CML。3种串行接口技术的电参数标准如表2所示[2~3]。其中LVDS和CML无论从结构、成本、功耗上都优于LVPECL,所以LVDS和CML是应用最为广泛的高速串行接口电路。

表2 常用高速串行接口技术的电参数标准

3.1 LVDS输出接口技术

图1是适用于高速数据传输的LVDS传输技术原理示意图。图中全差分负载ZL是为了提高传输路径的阻抗匹配[4~5]。LVDS是一种电流环信号传输技术,其电流环的方向(顺时针或逆时针)决定逻辑电平(高态或低态)。在线对的1条线上激励3.5 mA左右的电流,并通过线对的另1条线返回。在终端电阻器RT-R产生大约± 350 mV 电压(± 3.5 mA × 100 Ω = ±350 mV)。接收器量测此压降的极性,正电压对应逻辑高态、负电压对应逻辑低态。

图1 LVDS传输原理

LVDS的相对恒定、小输出电流降低了电源/地噪声。由于信号对中的电流是紧密耦合的电流环,所以边缘场趋于消除,从而降低了电磁干扰。同时,采用差分方式传送数据,有着比单端传输方式更强的共模噪声抑制能力。因为一对差分线对上的电流方向是相反的,当共模方式的噪声耦合到线对上时,在接收器输入端产生的效果是相互抵消的,因而对信号的影响很小。

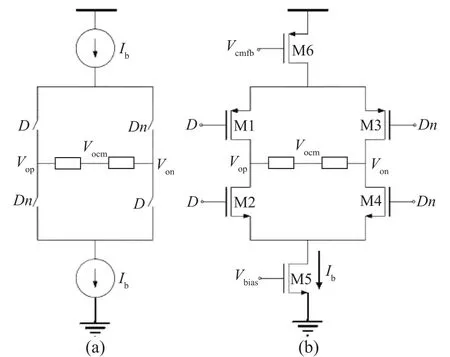

3.1.1 LVDS发送电路原理

LVDS发送电路的基本原理如图2所示。发送电路的基本原理为一个全桥式驱动电路(见图2(a)),Ib是3.5 mA的恒流源。Ib在输入信号D和Dn的控制下通过改变流过终端电阻的电流方向发送逻辑信号。当D开关有效时,Ib从Vop向右经过终端电阻流过Von;当Dn开关有效时,Ib从Von向左经过终端电阻流过Vop。

图2 LVDS发送电路的基本原理

图2(b)是这种全桥式驱动电路的一种实现方式,M1和M3是尺寸工艺相同的PMOS管,M2和M4是尺寸工艺相同的NMOS管,D和Dn是由同一Vin输入CMOS信号导出的互为反相的信号,输出Vop和Von在外部接阻值为100 Ω的终端电阻,构成回路。当Dn为高电平、D为低电平时,Ml和M4管导通,M2和M3管截止,电流从Vop流向Von,并产生350 mV的压降;反之,当Dn为低电平、D为高电平时,M2和M3管导通,Ml和M4管截止,电流从Von流向Vop,并产生350 mV的压降。这样就把一个CMOS信号转换成了LVDS信号。

3.1.2 LVDS发送电路结构

LVDS驱动器电路主要分为电平转换单元、输入信号调整单元、电流模主体驱动单元、共模反馈电路等几大功能模块,如图3所示。电平转换单元主要完成的功能为将core内电压进行升压处理,将低压内部高速数据信号转换为高压接口信号。输入信号转换单元将输入的经过升压后的数据流信号进行改善,恢复成其输入的数据(包括最小数据宽度,数据组成等)。由于LVDS电流模驱动电路的驱动开关管尺寸一般都比较大,而输入信号为没有任何驱动能力的数字逻辑信号,因此我们需要一个开关驱动电路将输入数字信号转换成互补驱动信号D和Dn。电流模驱动模块一般采用图2(b)所示电路,M1~M6组成了全桥式驱动电路,以提供输出电流方向不断切换的3.5 mA的电流。由于LVDS输出信号的共模电平必须稳定在1.2 V左右,因此需要设置一个共模反馈电路来稳定共模输出电压。

图 3 LVDS发送电路结构

3.2 CML接口技术

CML(current mode logic)是继ECL、LVDS之后又一种采用低电压差分信号传输技术的高速串行接口,是一种广泛应用于网络物理层和SerDes电路的一种非官方标准[7~9]。CML串行数据传输率的范围一般为1 Gbps~10 Gbps,而且还可以达到更高,其支持的最大传输速率取决于发送器和接收器所采用的制造工艺。CML接口信号电平没有一个固定的标准,因此不同厂商设计的CML有自己特定的规范。

3.2.1 CML接口结构和工作原理

单级CML buffer类似于传统的差分放大器,图4是标准的单级CML buffer。CML工作原理和它的结构一样简单,如图4所示。

尾电流源提供一个稳定的电流Iss,输入信号A、AN使Ml、M2轮流导通,也就是M1、M2推挽输出。这样输出就在(VDD-Iss×R)到VDD之间摆动,差分输出摆幅为Iss×R,通过调整Iss和R就可以得到理想摆幅的输出驱动电压。

图4 单级CML buffer结构示意图

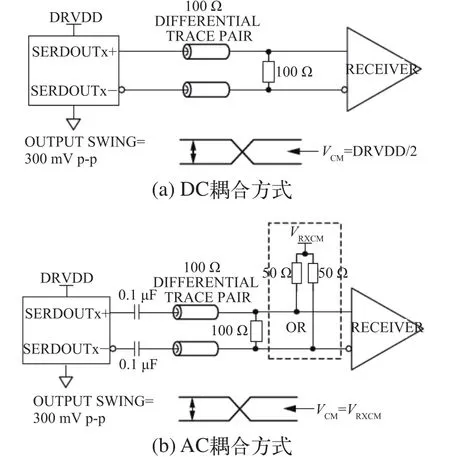

CML信号传输系统有多种信号传输方式。可以使用AC耦合,当使用编码的时候也可以使用DC耦合。AC耦合可以用在发送器和接收器使用不同供电电压的系统中。当使用AC耦合时,耦合电容要足够大,这样可以避免在连续传相同数据位时出现数据丢失。图5为CML信号摆幅在300 mV条件下的AC耦合和DC耦合方式。

图5 CML的耦合方式

3.2.2 CML发送器电路结构

CML驱动器分为主体电路和辅助电路两部分[10]。主体驱动电路主要包含电平转换模块、信号转换模块、CML驱动模块;辅助电路主要有用于测试的伪随机码生成器模块PRBS和用于生成偏置电压的基准电压模块,如图6所示。

CML驱动器的设计中,电平转换模块的作用就是将ADC数字内核电压转换为接口电平电压,若内外电压一致,则可以省略该电路的使用。驱动器中CML缓冲驱动模块主要是由多级CML buffer构成。单级CML buffer的结构类似于差分放大器,可以采用如图4所示的标准单级CML buffer[9]。采用该结构的CML输出速率达28 Gbps。

图6 CML驱动器结构

4 总线输出接口在ADC中的应用

高速流水线ADC产品的输出最先开始采用的是并行CMOS/LVDS输出。随着ADC分辨率的提高和多通道集成的应用需求,采用并行输出技术所需要的输出引脚数过多,极大地增加了系统PCB连线的设计复杂度。通过采用高速串行输出接口格式,每个ADC的数据输出引脚数目大为减少,极大地简化了系统间连线设计的复杂度。近年来,随着ADC数据传输率的进一步增加,光传输系统所用的SerDes技术开始运用于高速高精度ADC的输出接口模块。

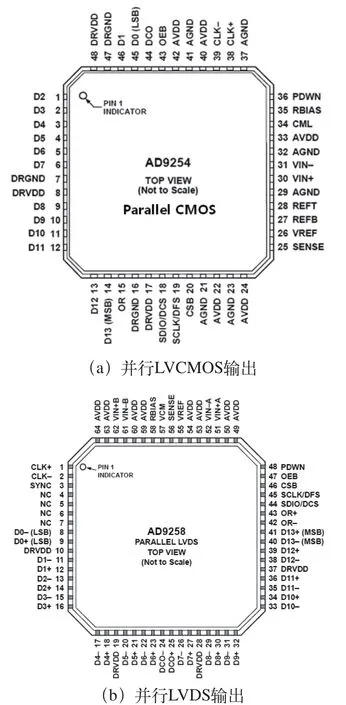

4.1 并行LVCMOS/LVDS输出格式

对于采用并行接口的ADC来说,当ADC采样速率在150 MSPS以下时,通常采用LVCMOS输出即可满足要求;对于采样速率超过150 MSPS的ADC电路产品来说,CMOS电平的高低转换时间太长,已经无法满足应用需求,因此大都采用并行LVDS输出技术,即每位输出采用一对LVDS差分输出引脚的方式。

图7所示为ADI公司2款分别采用LVCMOS和LVDS输出形式的14位125 MSPS的ADC电路产品的封装引脚图。图7(a)是AD9254电路的引脚排列,其采用的是并行LVCMOS输出,可以看出其使用的引脚数目为48[11]。图7(b)是AD9258电路的引脚排列,其采用的是并行LVDS输出,可以看出其使用的引脚数目为64,有效输出引脚数目增加了14个[12]。LVDS电路根据其输出数据率的不同,可以工作在单倍数据率和双倍数据率两种模式。

图8是ADI公司的AD9230电路在不同工作模式下的引脚排列,该电路是一款12位250 MSPS的流水线ADC电路产品,其采用的是并行LVDS输出[13]。图8(a)是AD9230电路采用单倍数据率LVDS模式下的引脚排列,可以看出其所使用的引脚数目为56;图8(b)是AD9230电路采用双倍数据率LVDS模式下的引脚排列,可以看出其通过引脚复用,所使用的有效引脚数目为44个,减少了12个。

图9所示为上述采用LVCMOS和LVDS输出形式的14位125 MSPS的ADC电路产品中输出接口时序图。图9(a)是AD9254电路所采用的典型并行LVCMOS输出时序,可以看出对于CMOS输出,一个时钟周期输出一个并行14位的数字码,采用DCO上升沿采样;图中的模拟输入为N时对应的数字输出码为N-13,原因在于AD9254内部流水线冗余延时为13个时钟周期。

图7 采用并行输出格式的ADC电路

图9(b)是AD9230电路所采用的单倍数据率LVDS输出时序,即一个时钟周期输出一个并行12位的数字码,采用DCO上升沿采样;图中的模拟输入为N时对应的数字输出码为N-7,原因在于AD9254内部流水线冗余延时为7个时钟周期。图9(c)是AD9230电路所采用的双倍数据率LVDS输出时序,即一个时钟周期输出两个并行12位的数字码,采用DCO上升沿和下降沿双沿同时采样,从而数据率翻倍,但同时时钟抖动要求增加。

图8 ADC电路采用的并行LVDS输出格式

4.2 串行LVDS输出格式

采用并行LVDS输出技术可有效解决ADC输出速率的限制问题,但是随着单片集成ADC通道数的增加,其所需要使用的输出引脚数也会相应倍增。通过采用双倍数据率数据输出,输出时钟的上升沿和下降沿同时采样,可以使所需要的引脚数减半。依此类推,通过采用更高倍数据率的输出技术和采样时钟,则可以将输出引脚的数目进一步压缩,最大化发挥LVDS输出技术的数据吞吐率优势,这就是串行LVDS输出技术。例如,对于16位125 MSPS的ADC电路,通过16倍数据率输出和2 GHz采样时钟进行采样,采用一对LVDS差分输出引脚即可满足需求。然而,由于LVDS传输速率小于2 Gbps,16×125 MSPS的数据传输率接近上限,通常将16位数据分为2组进行输出,因此总共需要4个数据输出引脚。

图9 典型并行输出ADC的输出时序图

图10所示为ADI公司1款采用串行LVDS输出形式的4通道单片集成16位125 MSPS的ADC电路产品AD9653的封装引脚图,可以看出其使用的引脚数目仅为48[14]。若采用双倍数据率并行LVDS输出,则需要使用96个引脚,可见串行LVDS技术的输出引脚数目大为降低。图11是AD9653电路所采用的串行LVDS输出时序,电路根据不同输出模式可以采用奇数8位和偶数8位各用一对LVDS差分输出引脚的组合,或者采用高8位和低8位各用一对LVDS差分输出引脚组合,采样时钟CLK一个周期差分数据线D0和D1各输出一组8位的串行数字码;输出时钟DCO为采样时钟CLK的8倍频时钟, FCO为与输入采样时钟同频的时钟,输出数据采用DCO上升沿采样。

对于16位ADC的高速串行输出,输出16位数字码必须转换为串行码流才能用于LVDS串行输出。图12是一种可用于AD9653电路的16位并行数字码转串行输出的电路模块结构图。首先,输入16位并行数字码进行并转串处理得到两组8位串行码;其次,8位串行码进入卷积处理模块,同8位1 GHz的伪随机码进行编码处理,以增加输出数字码的抗干扰能力,降低误码率;最后,经编码后的码流由LVDS发送器输出。

图10 AD9653引脚图

图11 AD9653串行数据输出时序

图12 用于AD9653电路的16位并行转串行模块

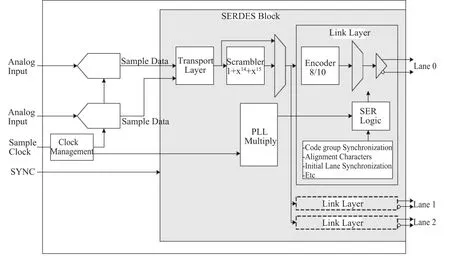

4.3 SerDes总线输出

虽然串行LVDS输出技术较并行CMOS/LVDS输出技术减少了大量的输出引脚,但由于其可支持的最高速度受到了限制,在传输更高采样率的ADC输出数据时,一对LVDS差分输出电路的数据吞吐率难以满足要求,需要采用多对LVDS输出电路,从而增加了输出引脚数目。通过采用输出数据吞吐率更高的SerDes总线接口技术,一个ADC仅需一组SerDes输出线,即2个输出引脚,就可满足需求。

SerDes总线接口包括编码发送和解码接收两大组成部分,对于高速ADC来说仅使用编码发送模块。图13所示为一种2.5 Gbps传输速率的SerDes发送电路的系统结构,可以看出该发送电路主要包括8 b/10 b编码电路、并转串电路、输出驱动器和锁相环电路等部分[15]。

图13 一种SerDes发送电路的系统结构

发送电路中的 8 b/10 b 编码电路对输入到发射机的16位并行数据以及控制码(也即K码)进行编码。发送器电路中的8 b/10 b编码电路是为了串行数据的直流平衡,避免出现长时间的“0”或者“1”,以方便接收器实现时钟数据恢复(CDR)。输入的16位并行数据TXD0~TXD15首先分成高低两个字节,每个字节附带一位控制位(TKMSB和TKLSB)。数据位和控制位总共18位信号分成两组,分别进入两个并行的编码器。当控制位TKMSB或TKLSB为高电平时,编码电路对相应的数据字节进行K码编码,即控制码编码;为低电平时,对相应的字节进行D码编码,即数据编码。并串转换模块由并行输入控制逻辑、输入寄存器、高速移位寄存器和若干逻辑门组成,一般有串行结构、并行结构和树形结构3种。图13电路中经过8 b/10 b编码后的数据为2 组10 bit的并行数据,经过多选器后输出一组频率为2倍发射时钟频率的并行数据,再经过10:1并串转换电路,实现高速的并串转换。

在SerDes总线技术的各种形式中,近年来在高速ADC中运用最为广泛的是JESD204B标准接口。JESD204B标准串行接口技术,较之CMOS和LVDS接口产品在速度、尺寸和成本上更有优势。图14所示是一种用于Intersil公司14位500 MSPS流水线ADC电路ISLA214S50的JESD204B输出电路的模块结构图[16]。其核心模块结构和图13中的SerDes发送器电路结构类似,由于该14位ADC采样速率达500 MSPS,因此所使用的JESD204B模块的数据率为7 Gbps。

5 总结

随着ADC采样速率和分辨率的持续提高,高速高精度ADC的输出数据吞吐率同步提高。传统的TTL和CMOS等数字接口逻辑已无法满足高速ADC的应用需求。为解决该类瓶颈限制问题,LVTTL、LVCMOS等优化的数字逻辑接口、更高速的差分串行LVDS、CML输出接口以及最近几年采用的SerDes接口均被运用于ADC输出接口模块。

图14 用于ISLA214S50电路的JESD204B模块结构图

在高速ADC的具体应用中,并行LVTTL和LVCMOS接口时序简单易于使用,但最高传输速率被限制在150 MSPS以下;并行LVDS技术可以大幅提高传输速率,但是PAD接口数目太多,无法在多通道集成的ADC系统中使用;采用多倍速率采样的高速串行LVDS技术可以大幅减小ADC所使用的PAD端口数目,特别适用于多通道系统集成ADC系统使用,然而LVDS数据传输率的上限限制了ADC采样速率;采用SerDes技术可以突破串行LVDS技术的速率限制,但是接口系统的设计复杂度大幅提升。

[1] 季惠才,陈珍海,孙华,张甘英,等. 一种基于CMOS工艺的Gbps高速LVDS发送电路[J]. 电子与封装,2009,9(1):24-27.

[2] Boni, Andrea. LVDS I/O Interface for Gb/s per Pin Operation in 0.35μm CMOS [J]. IEEE J. Solid-State Circuits. 2001, 36(40) : 706-711.

[3] 美国国家半导体公司.差分时钟脉冲传送技术成为发展趋势[J]. 世界电子元器件,2003,25(8): 39-42.

[4] IEEE Standard for Low-Voltage Differential Signals(LVDS) for Scalable Coherent Interface (SCI)[C]. IEEE Std. 1596.3-1996, July.

[5] Electrical characteristics of low-voltage differentialsignaling (LVDS) interface circuits[C]. TIA/ EIA-644,National Semiconductor Corp., ANSI/TIA/EIA, 1996.

[6] Chen Mingdeng,Silva-Martinez Jose, Nix Michael, et al.Low-Voltage Low-Power LVDS Drivers[J]. IEEE J. Solid-State Circuits. 2005. 40(2): 472-479.

[7] Schrader J,Klumperrink E A M,Visschers J, et a1. Pulse width modulation pre-emphasis applied in a wireline transmitter, achieving 33 dB loss compensation at 5 Gb/s in 0.13-μm CMOS[J]. IEEE J Solid-State Circuits, 2006,41(4): 990.

[8] Higashi H,Masaki S,Kibune M,et a1. A 5~6.4 Gb/s 12-channe1 transceiver with pre-emphasis and equalization[J]. IEEE J Solid-State Circuits, 2005. 40(4) :978.

[9] U. Sigh, A. Garg, N. Huang, etc. A 780mW 4×28 Gb/s Transceiver for 100 Gb E Gearbox PHY in 40nm CMOS[C].ISSCC 2014, Dig. of Tech. Papers, Feb. 2014: 40-42.

[10] 2.5 V/3.3 V Differential l:2 Clock/Data Fanout Buffer/Translator with CML Outputs and termination[EB/OL].http://www. Onsemi.com

[11] Analog Devices. 14-Bit 150MSPS 1.8V Analog to Digital Converter[P]. AD9254, 2006.

[12] Analog Devices. 14-Bit 125MSPS 1.8V Dual Analog to Digital Converter[P]. AD9258, 2009

[13] Analog Devices. 12-Bit 250MSPS 1.8V Analog to Digital Converter[P]. AD9230, 2007.

[14] Analog Devices. Quad 16-Bit 125MSPS, Serial LVDS 1.8V Analog to Digital Converter[P]. AD9653, 2012.

[15] Texas Instruments. 1.6 to 2.7 Gbps Serdes Transciever[P].TLK2711-SK, 2004.

[16] Intersil. 14-Bit 500MSPS JESD204B High Speed Serial Output ADC [P]. ISLA214S50, 2012.